ю

4

Изобретение относится к вычислительной технике и может быть использовано при построении запоминающих устройств.

Целью изобретения является упрощение ячейки памяти.

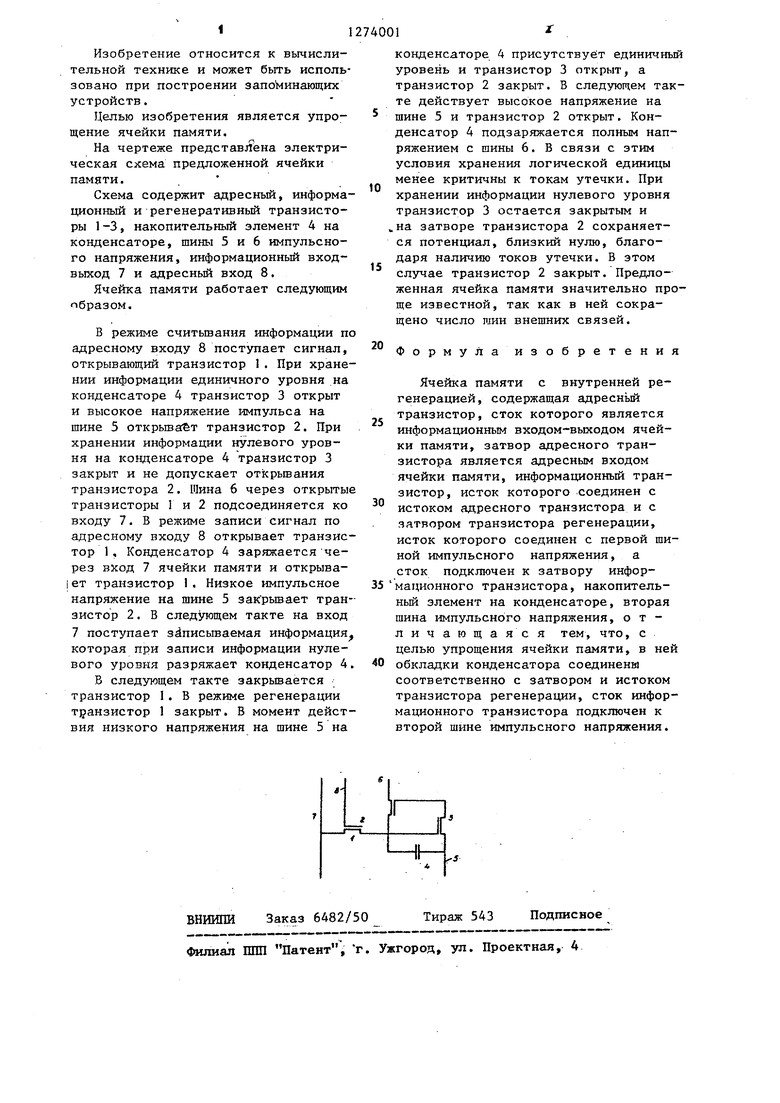

На чертеже представлена электрическая схема предложенной ячейки памяти.

Схема содержит адресный, информационный и регенеративный транзисторы 1-3, накопительный элемент 4 на конденсаторе, шины 5 и 6 импульсного напряжения, информационный входвыход 7 и адресньй вход 8.

Ячейка памяти работает следующим образом.

В режиме считьюания информации по адресному входу 8 поступает сигнал, открывающий транзистор 1. При хранении информации единичного уровня на конденсаторе 4 транзистор 3 открыт и высокое напряжение импульса на шине 5 открьтабт транзистор 2. При хранении информации нулевого уровня на конденсаторе 4 транзистор 3 закрыт и не допускает открьшания транзистора 2. Шина 6 через открытые транзисторы 1 и 2 подсоединяется ко входу 7. В режиме записи сигнал по адресному входу 8 открывает транзистор 1, Конденсатор 4 заряжается через вход 7 ячейки памяти и открываi ет транзистор 1. Низкое импульсное напряжение на шине 5 закрьшает транзистор 2. В следующем такте на вход 7 поступает зёписьтаемая информация которая при записи информации нулевого уровня разряжает конденсатор 4.

В следующем такте закрьюается ; транзистор I. В режиме регенерации транзистор 1 закрыт. В момент действия низкого напряжения на шине 5 на

конденсаторе 4 присутствует единичны уровень и транзистор 3 открыт, а транзистор 2 закрыт. В следующем такте действует высокое напряжение на шине 5 и транзистор 2 открыт. Конденсатор 4 подзаряжается полным напряжением с шины 6. В связи с этим условия хранения логической единицы менее критичны к токам утечки. При хранении информации нулевого уровня транзистор 3 остается закрытым и .на затворе транзистора 2 сохраняется потенциал, близкий нулю, благодаря наличию токов утечки. В этом случае транзистор 2 закрыт. Предложенная ячейка памяти значительно проще известной, так как в ней сокращено число шин внешних связей.

Формулаизобретения

Ячейка памяти с внутренней регенерацией, содержащая адресньй транзистор, сток которого является информационным входом-выходом ячейки памяти, затвор адресного транзистора является адресным входом ячейки памяти, информационный транзистор, исток которого соединен с истоком адресного транзистора и с затвором транзистора регенерации, исток которого соединен с первой шиной импульсного напряжения, а сток подключен к затвору информационного транзистора, накопительньй элемент на конденсаторе, вторая шина импульсного напряжения, отличающаяся тем, что, с целью упрощения ячейки памяти, в ней обкладки конденсатора соединена соответственно с затвором и истоком транзистора регенерации, сток информационного транзистора подключен к второй шине импульсного напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Элемент памяти для ассоциативного накопителя | 1976 |

|

SU690565A1 |

| Полупроводниковая ячейка памяти | 1976 |

|

SU723680A1 |

| Ячейка памяти | 1977 |

|

SU693437A1 |

| Ячейка памяти | 1981 |

|

SU1275545A1 |

| Элемент памяти | 1979 |

|

SU788175A1 |

| Ассоциативный запоминающийэлЕМЕНТ | 1979 |

|

SU805412A1 |

| Ячейка памяти для оперативного запоминающего устройства с энергонезависимым хранением информации | 1986 |

|

SU1531163A1 |

| Ячейка памяти | 1982 |

|

SU1327187A1 |

| Ячейка памяти для регистра сдвига | 1980 |

|

SU902075A1 |

| Ассоциативная ячейка памяти | 1976 |

|

SU605268A1 |

Изобретение относится к области вычислительной техники и может быть использовано при построении запомиг нающих устройств. Цель изобретения упрощение ячейки памяти - достигается тем, что, в ячейке памяти, содержащей три транзистора и накопительный элемент на конденсаторе, конденсатор подключен к затвору и кистоку : третьего транзистора подсоединением стока второго транзистора к одной из шин импульсного напряжения. Это позволило значительно упрос тить ячейку памяти за счет сокращения числа внешних связей. 1 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Электроника, № 4, 1981, с.57-58. | |||

Авторы

Даты

1986-11-30—Публикация

1984-07-05—Подача