УСТРОЙСТВО для ВОСПРОИЗВЕДЕНИЯ ФУНКЦИИ

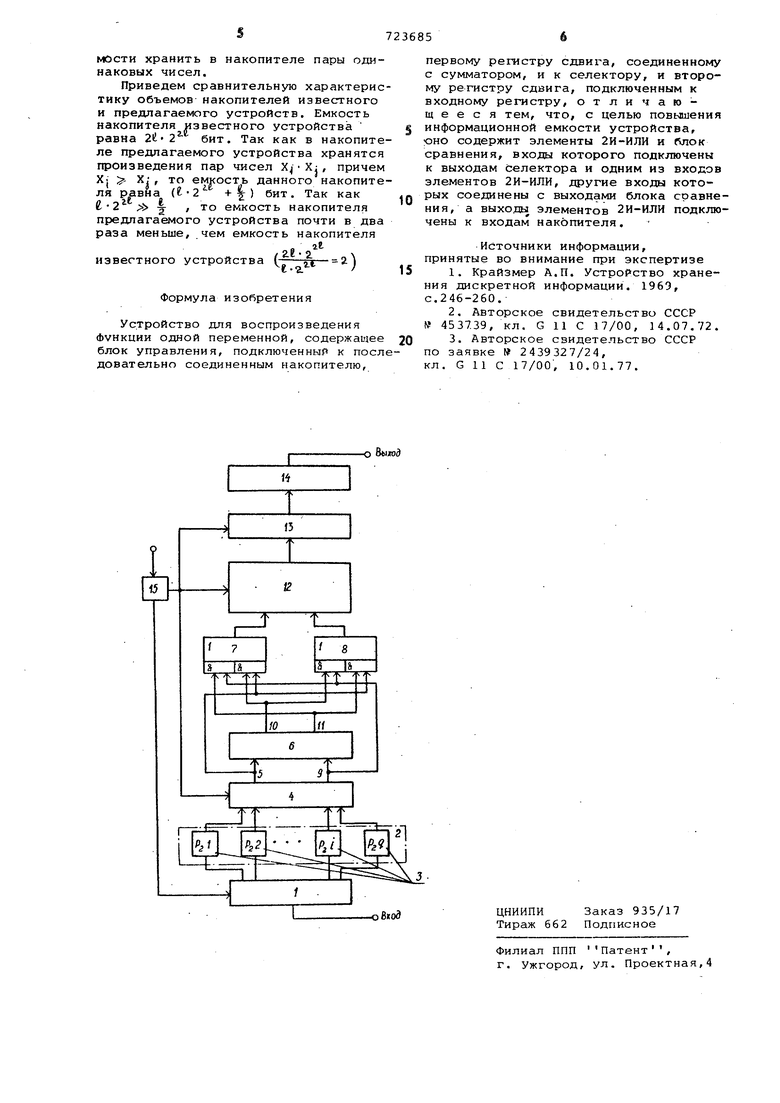

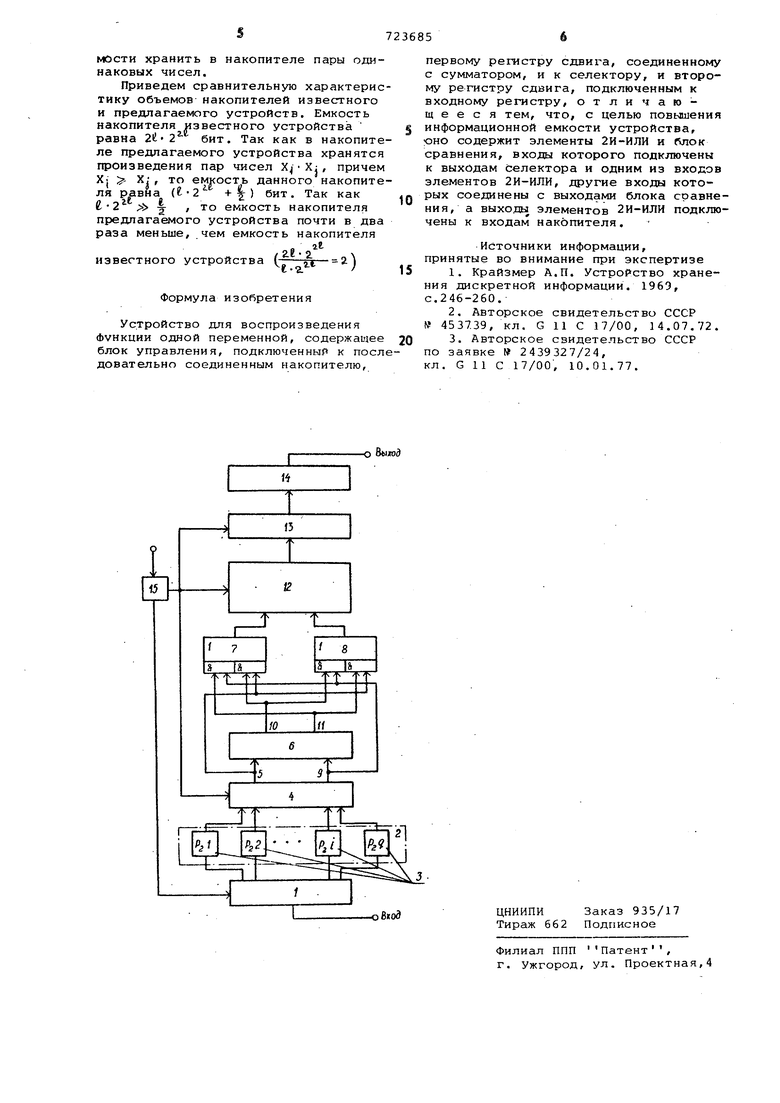

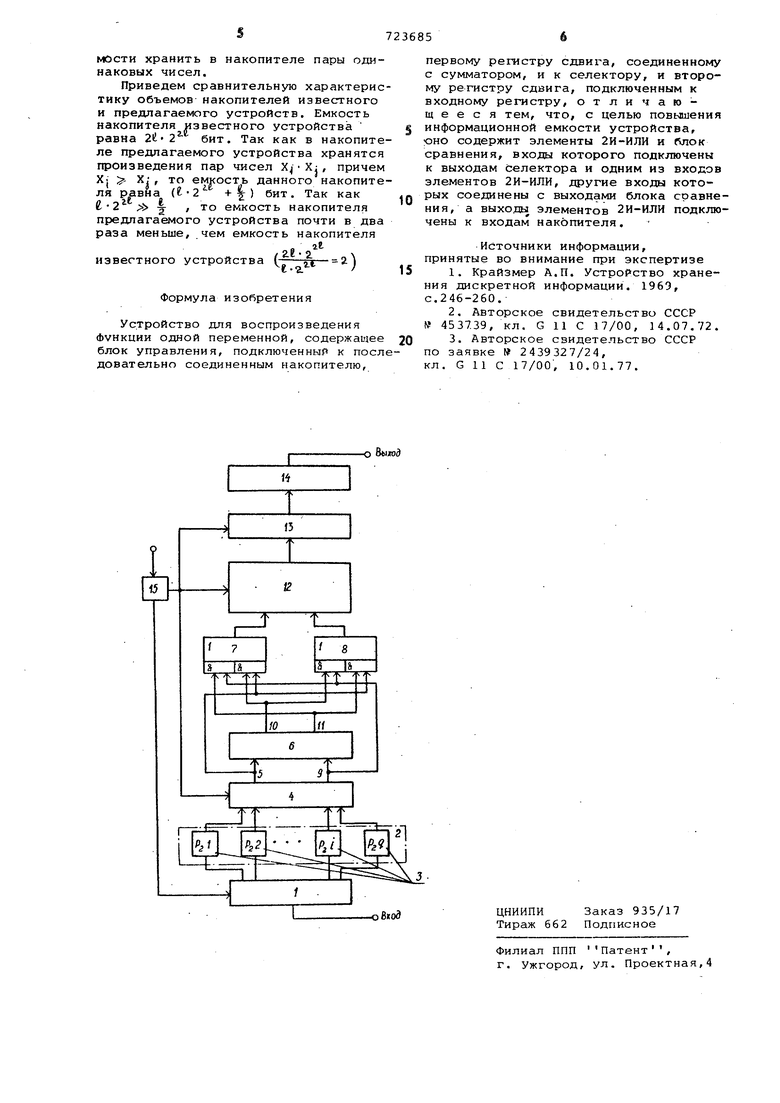

(54: ОДНОЙ ПЕРЕМЕННОЙ на определенное число разрядов. Емг кость накопителя равна 2- 28- бит з Недостатком указанных устройств является большой объем памяти при хр нении значений функции Х. Цель изобретения - повышение инфо мационной емкости устройства. Это достигается тем, Что в устрой ство для воспроизведения функции одной переменной содержащее блок упра ления, подключенный к по.следовательн соединенным накопителю, первому регистру сдвига, соединенному с сумматором, и к селектору, и второму регистру сдвига, подключенным к входно регистру, введены элементы 2И-ИЛЙи блок сравнения, входы которого подклю чены к выходам селектора и одним из входов элементов 2И-ИЛИ, другие входы которых соединены ;С выходами блока сравнения, а выходы элементов 2И-ИЛИ подключены к входам накопителя, На чертеже представлена блок-схема устройства для воспроизведения функции одной переменной. Устройство состоит из второго регистра сдвига 1, соединенного с п-разрядным входным регистром 2, состоящего из q2 -разрядны.,: регистров 3 (п Яй, п - разрядность входного слова), выходы которого соединены со входами селектора 4, один выход 5 ко торого подключен к первому входу бло ка сравнения 6 и к первым входам пер вых элементов и обеих блоков элементов 2И-ИЛИ 7 и 8, а другоГ выход 9 - ко второму вхо.цу блока сравнения 6 и первым входам вторых элементов И обо их блоков 7 и 8. Выход 10 блока срав нения 6 подключен ко вторым входам первого элемента И первого блока 8 и второго элемента И второго блока 7. Выход 11 блока сравнения 6 подключен ко вторым входам второй схемы И-первого блока 8 и первого элемента И второго блока 7. Выход блока 8 подключен к f -cTapuMM, а выход блока схем 7 - к - младшим разрядам адресных цепей накопителя 12 (разрядность адресных цепей. - 2Й). Выходы накопителя 12 через первый регистр сдвига 13 соединены с сумматором 14, выход которого является выходом устройства. , Блок местного управления 15 соеди нен со входами регистра сдвига 13, селектора 4, накопителя 12, регистра сдвига 1, Устройство работает следующим образом. Входное п-разрядное слово X поступает на вход устройства последовательно-параллельным кодом (например, побайтно со стар1иих разрядов в виде q -разрядных кодовых посылок). Каждая i-я кодовая посылка представляет собой li-разрядное слово X. Число X можно представить в виде x-x..r), ,,., Тогда функцию X можно представить в виде М xt-. i,.., . 1 г.,..,-i-i,.i i. j . По тактовому сигналу Т блок местного управления 15 настраивает регистр .сдвига 1 таким образом, что i-ая кодовая посылка (число заносится в i-ый регистр 3. После записи 1-ой кодовой посылки в i-ый регистр 3 блок местного управления 15 вырабатывает серию сигналов C|i (j 1, 2, 3,..., i), кот рые поступают на управляющие входы селектора 4, накопитель 12 и первый регистр сдвига 13. По каждому сигналу С.;; (j 1/ 2,,.., i) содержимое i-ro регистра 3 (4Hvjло Х() передается на вход 5 блока сравнения 6, а содержимое j-ro регистра 3 (число Х;) - на вход 9 блока сравнения 6. . При Х| :г Х; на выходе 10 схемы сравнения 6 появляется сигнал, по .которому число Xj через блок 8 элементов 2И-ИЛИ передается в стар1чие разряды, а число Xi через блок 7 элементов 2И-ИЛИ передается в младшие разряды адресных цепей накопителя 12. Адрес, сформированный таким образом, будет иметь вид Xj (с Х; , где знак Обозначает последовательную запись цифр числа Х-, и Xi (например, если Х| 011, Xj 101, то запись Х. представляет собой код 01110 l). При Xj i на выходе 11 схемы сравнения б появляется сигнал, по коTopOMi число X ; через блок 8 элементов 2И-ИЛИ передается в старшие разряды, а число X; через блок 7 элементов 2И-ИЛИ передается в младшие разряды адресных цепей накопителя 12. Адрес, сформированный в этом случае, будет иметь вид Xj Х . Выбранное из накопителя 12 произ- ведение XjХ со сдвигом влево на (2q- i - j) + 1 разрядов подается на вход накапливаюьчего сумматора 14 и суммируется с его содержимым. Сдвиг произведения Xj-X; осуществляется первым регистром сдвига 13 по сиг-налу из блока местного управления 15. После выполнения описанного цикла, соответствующего сигналу Cqi , на выходе сумматора 14 будет получено число X . Другими словами, в каждом ij-том такте в старшие разряды регистра адреса накопителя 12 заносится большее, .а в младшие - меньшее из чисел Xj и Xi. Это позволяет избежать необходимости хранить в накопителе пары одинаковых чисел. Приведем сравнительную характерис тику объемов накопителей известного и предлагаемого устройств. Емкость накопителя известного устройства равна бит. Так как в накопите ле предлагаемого устройства хранятся произведения пар чисел Х/Х;, причем Xj X;, то емкость данного накопите ля (4-2 ) бит. Так как 2 2 /то емкость накопителя предлагаемого устройства почти в два раза меньше,.чем емкость накопителя а известного устройства ( ч t L Формула изобретения Устройство для воспроизведения ФУНКЦИИ одной переменной, содержащее блок управления, подключенный к посл довательно соединенным накопителю. первому регистру сдвига, соединенному с сумматором, и к селектору, и второму регистру сдвига, подключенным к входному регистру, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит элементы 2И-ИЛИ и Плок сравнения, входы которого подключены к выходам селектора и одним из входов элементов 2И-ИЛИ, другие входы которых соединены с выходами блока сравнения, а выходы элементов 2И-ИЛИ подключены к входам накопителя. Источники информации, принятые во внимание при экспертизе 1.Крайзмер А.П. Устройство хранения дискретной информации. 1969, с.246-260. 2.Авторское свидетельство СССР 4537.39, кл. G 11 С 17/00, 14.07.72. 3.Авторское свидетельство СССР по заявке 2439327/24, кл, G 11 с 17/00, 10.01.77.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1979 |

|

SU926653A2 |

| Устройство для воспроизведения функции одной переменной | 1977 |

|

SU597008A1 |

| Запоминающее устройство | 1987 |

|

SU1443029A1 |

| Постоянное запоминающее устройство для многоместных симметричных функций | 1979 |

|

SU873277A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для вычисления стандартных функций | 1980 |

|

SU942032A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Цифровой синтезатор частот | 1983 |

|

SU1190457A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Устройство для возведения в квадрат | 1975 |

|

SU606156A1 |

Авторы

Даты

1980-03-25—Публикация

1978-03-20—Подача