1

Изобретение относится к вычислительной технике и предназначено для вычисления функции х.

По основному авт. св. № 796841 известно кстройство для шлчисления функции X , содержащее входной п-разрядный регистр, сумматор, блоки памяти, причем входной регистр содержит дв-разрядных групп (где п q), выходы i-ой группы разрядов (1 1,2...q-l,q) входного регистра соединены со входами i-блока памяти первой группы и 2 -входовых блоков памяти второй группы, причем k и j (k j , k l,2...q-l, j 2,3...q)e разрядных групп входного регистра соединены со входами kj-ro блока памяти второй группы, выходы которого подключены к (k+j-2)t+2- (k+j) +1 входам сумматора, а выходы i-ro блока памяти первой группы соединены с (21 - 2)6 + 1 - 21 входами сумматора 11).

В блоках- памяти такого устройства необходимо хранить произведения всех возможных пар Р -разрядных чисел, в том числе и одинаковые произведения типа х |.-х g и. JCg-xj., что требует увеличенного объема постоянного запоминающего устройства (ПЗУ).

Цель изобретения - повышение информационной -емкости устрюйства для вычисления функции и сокращение объема аппаратуры.

Поставленная цель достигается тем, что а устройстве для вычисления функции х выходы k-ой и j-ой ( , k l,2...q-l; j 2,3.. .q)e-разрядной группы разрядов входного регистtoра соединены непосредственно с первой группой входов и через схему сравнения - Со второй группой входов первой и второй групп элементов 2И - 2ШШ, выходы которых подключе15ны соответственно ко входам младших и старьгах разрядов kj-ro блока памяти второй группы.

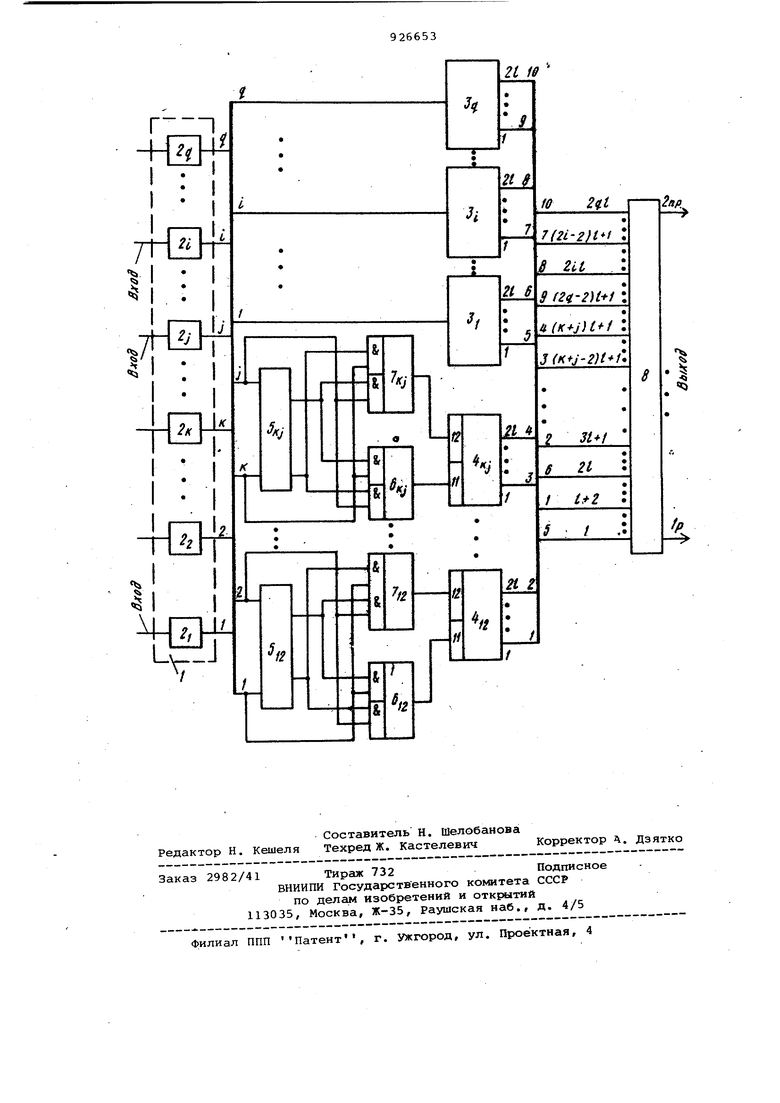

На чертеже представлена структурная схема Устройства для вычисления

20 функции х.

Предлагаемое устройство содержит входной гг-разрядный регистр 1, выполненный в.виде qe-разрядных групп разрядов 21(1 1,2...q-1,q), 25входовые блоки 3 памяти первой группы и 2В-входевые блоки 4 памяти второй группы схемы 5 сравнения, группы элементов 2И - 2 ИЛИ 6 и 7, Ксшсдый из которых содержит f эле30ментов 2И-2ИЛИ, сумматор 8, выходы 9 и 10 схемы сравнения, младшие 11 и Старшие 12 разряды блоков памяти второй группы. Устройство работает следующим образом. Двоичное, число х можно преде тавить в виде X X л+ Хп- 2 +.. .+х ., 2 ,. . +. .. ...+ 4-2Гк-1)г +...Wy +... ... 4 х.Тогда выражение для функции х имеет вид О Л ( И-Ч-) IliDX .Х.-Ч Ы i В каждом е-входном блоке 3 памят пер&ой группы хранятся кващраты все -раз рядных чисел, а в Кс1ждом 2 В-в х довом блоке 4 памяти второй группы произведения всех возможных пар Е-разрядных чисел x.xj, удовл-етворяющих условию X / Xj . После подачиаргумента х на регистр 1 на выходе 8-разрядных групп разрядов 2, 2(2,... ,2q,, записываетс 6-разрядные числа х ,XQ, .. . ,xq, соответственно. Из каждого блока 3 памяти по адресу X. выбирается число х , которо подается на (21-2) +1-21 выходы сумматора -8, т.е. число х подаете на сумматор 8 со сдвигом на (21-2)6 разряда влево, что соответствует умножению числа х на величину 2(li1)2 , т.е. первое слагаемое формулы (1). На каждую схему сравнения пос тупает пара в-разрядных чисел хц и X j. При X 1 , X ; на выходе 9 схемы SK; сравнения появляется сигнал, по которому число XK через группу элементов 2И-2ИЛИ 7Kj передается в 6 старших- разрядов 12, а число xj через группу элементов 2И-2ИЛИ цв младших разрядов 11 блока 4 п мяти. Адрес, сформированный таким образом, будет иметь вид х + xj , где знак -х обозначает последовател ную запись цифр чисел х j, и xj . При X Xj на выходе lO схемы сравнения появляется сигнал, по которому число X,- через блок 7KJ пере дается в 2 старших разрядов 12, а число Х|; через блок 6ц в Р младших разрядов 11 данного блока 4| памяти. Адрес, сформированный в этом случае, имеет вид х; # х. Другими словами, в старшие разряды k -го блока 4 памяти второй группы через элементы б и 7 заносится большее, а в младшие - меньшее из чисел х и xj . Это позволяет избежать необходимости хранить в каждом-блоке 4 памяти второй группы пары одинаковых чисел Xs и Хд.Х. Из каждого блока 4 памяти второй группы по адресу выбирается число Xj.xj, которое подается на (k+j-2)E + +2-(k+j)2-M входы сумматора 8, т.е. со сдвигом на (k+j-2)e разряда влево, что соотве;тствует Т. нию чисна величину 2 , т.е. второе слагаемое формулы (1). После сложения чисел, выбранных из всех блоков памяти первой 3 и второй 4 групп, на выходах сумматора 8 получаем значение функции х. Предлагаемое устройство дает, возможность снизить объем памяти и повысить информационную емкость. Формула изобретения Устройство для вычисления функции, х по авт. св. № 796841, отличающееся тем, что, с целью повышения информационной емкости устройства и сокращения объема аппаратуры, выходы k-ой и j-ой (k j , k l,2,...q-l, i 2,3,..,g)e-разрядной группы разрядов входного регистра соединены непосредственно с первой группой входов и через схему сравнения - со второй группой входов первой и второй групп элементов 2И-2ИЛИ, выходы которых подключены соответственно ко входам младших и стараих разрядов kj-ro блока памяти второй группы. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 796841, кл. G 06 F 7/38, 17.09.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций одной переменной | 1978 |

|

SU723685A1 |

| Устройство для вычисления функции | 1976 |

|

SU796841A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Скалярный умножитель векторов | 1988 |

|

SU1619254A1 |

| Постоянное запоминающее устройство для многоместных симметричных функций | 1979 |

|

SU873277A1 |

| Устройство для умножения | 1981 |

|

SU1013946A1 |

| Устройство для деления нормализованных чисел | 1985 |

|

SU1290302A1 |

| Генератор многомерных случайных величин | 1981 |

|

SU966692A1 |

| Устройство для вычисления логарифмов чисел | 1980 |

|

SU932491A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

Авторы

Даты

1982-05-07—Публикация

1979-06-19—Подача