Изобретение относится к радиотехнике и может использоваться в системах связи с импульсно-кодовой модуляцией в целях определения в передаче местоположения синхроимпульсов и дальнейшего осуществления синхронизации по циклам.

По основному авт.. свид. № 565402 известно устройство синхронизации по циклам, со 1ержащее на входе формирователь тактовых импульсов и N блоков oпp6бьшa y я импульснь1х позиций с расширителями, а также делитель-распределитель и последовательно соединенные элементы И-ИЛЙ, ИЛИ и элемент задержки, вход и выходы которого подключены к соответствующим входам блоков опробьшания импульсных позиций, причем выход и вход первогорасширителя подключены к соответствующим входам элемента И непосредственно и через накопитель, а также регистр сдвига, уз.ел перезаписи сигналов несоответствия и элемент запрета, при этом выход формирователя тактовых импульсов непосредственно, и через последовательно соединенные ,эдемеИ:Т запрета и делитель-распределитель подkлючeн к соответствующим входам регистра сдвига, одна группа выходов которого подключена к соответствующим входам блоков опробования импульсных позиций, первого, узла перезаписи сигналов несоответствия и элементов И-ИЛИ, а другая группа выходов - к входу, первого расширителя непосредственно, а к входам (N-1) расширителей - через элемент И, при0чем выходы расширителей непосредственно подключены к соответствующим входа1М элемента И-ИЛИ, выхоД которого подключен к второму входу элемента запрета, а йыход узла перезаписи

5 сигналов несоответствия подключен к дополнительному входу одного из расширителей 1..

Однако известное устройство обладает недостаточной помехоуст ойчи0востью,/

Цель изобретения - повышение помехоустойчивости устройства синхронизации по циклам..

Для достижения указанной цели в

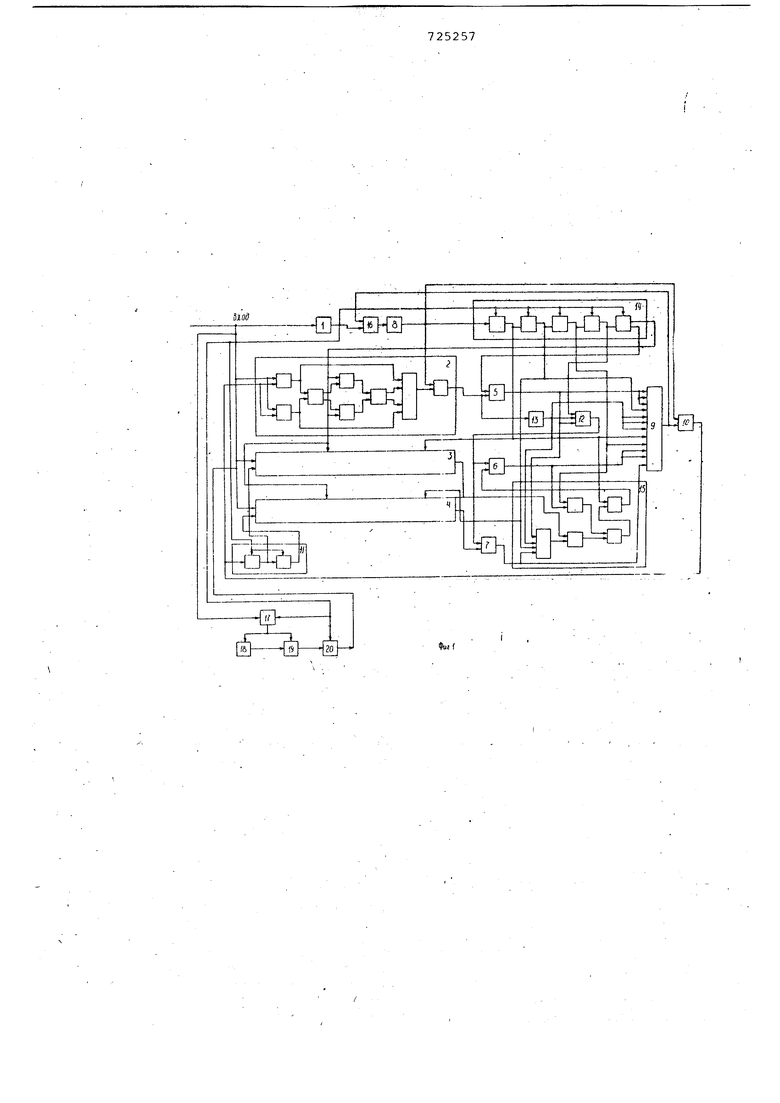

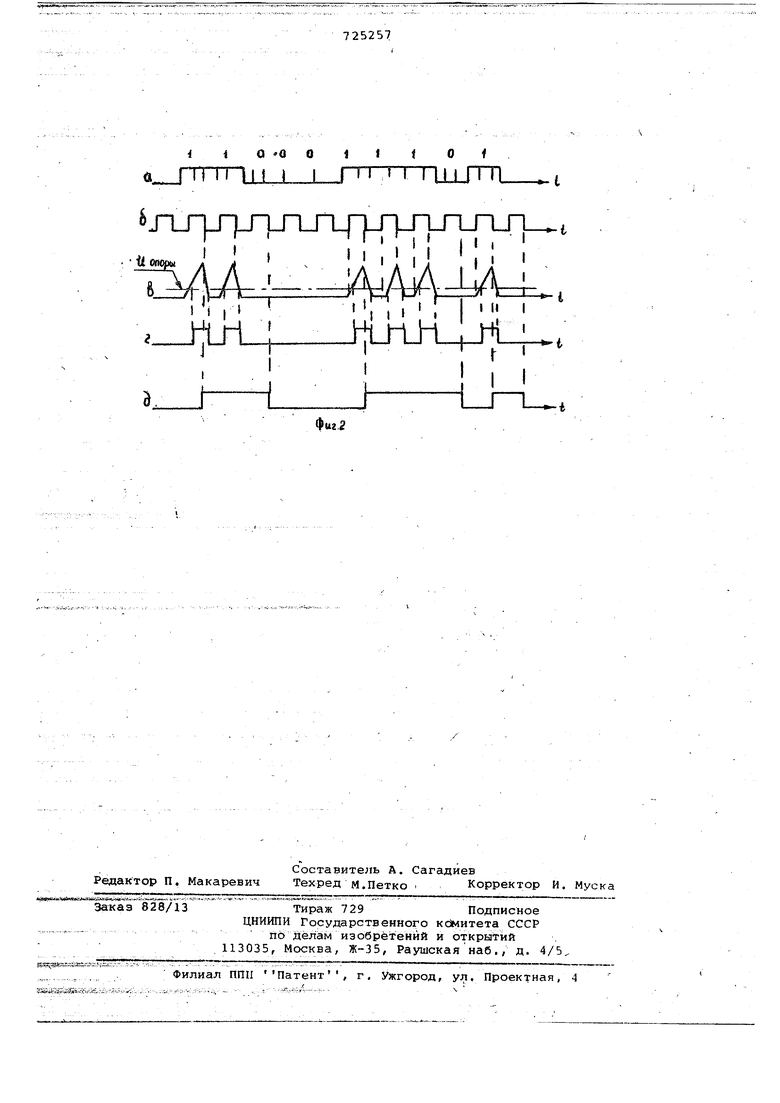

5 устройство синхронизации па циклам, содержащее на входе формирователь тактовых-импульсов и N блоков опробывания импульсных позиций с расширителями, а также делитель-распределитель и последовательно соединенные элементы И-ИЛИ, ИЛИ и элемент задерж ки, вход и выходы которого подключены к соответствующим входам блоков опробывания импульсных позиций, причем выход и вход первого расширител подключены к соответствующим входам элемента И непосредственно ичерез накопитель, а также регистр сдвига, узел .перезаписи сигналов несоответст вия и элемент запрета, при этсм выхо формирователя тактовых импульсов нейосредствённо и через последовательн соёдийенные элемент запрета и дели ёйБ-раепрбделитель подключен к соот ёШгГТВуюЩим входам регистра сдвига, Шйа группа выходов которого подключена к соответствующим входам блоков опробования импульсных позиций,.крой% Первого, узла перезаписи сигналов несоответствия и элементов И-ИЛИ, а другая группа выходов - к входу первого расширителя непосредственно, а к входам (N-1) расширителей - через элемент И, причем выходы расширителей Непосредственно подключены к соЬтветствующим входам элвиента И-ИЛИ, выход которого подключен к второму ВХОДУ элемента запрета, а выход узла перезаписи сигналов несоответствия пойключен к дополнитель.ному входу од рого иэ расширителей, введены последойательно соединенные интегратор, фильтр нижних частот, компаратор и регенератор, выход которого подключе к входам N блоков опробования импуль ных позиций, причем выход формирователя тактовых импульсов подключен к другому входу регенератора и входу Ийтегратора, выход которого подключе К другому входу компаратора, при этс на другой вход интегратора подан входной сигнал. На фиг, 1 приведена структурная электрическая схема устройства; на фиг. 2 - временные диаграммы, поясняющие работу предложенного устройс ва. Устройство синхронизации по цикла содержит формирователь 1 тактовых им пульсов, блоки 2, 3 и 4 опробования импульсных позиций, расширители 5, б и 7, делитель-распределитель 8, элементы И-ИЛИ 9, элемент И 10, эле мент задержки 11, элемент И 12, накопитель 13, регистр 14 сдвига, уэе 15 п;0рёзаписи сйГйалов несоответств элемент 16 з&прета, интегратор 17, фильтр 18 нижних частот, компаратор 19 и регенератор 20. Устройство синхронизации по циклам работает следующим образом. . в режиме синхронизма входной CHI нал с шумом (фиг. 2а) поступает на интегратор 17, куда также поступает и сигнал с формирователя 1 тактовых импульсов (фиг. 26), который управляет работой интегратора 17. Заряд емкости интегратора 17 осуществляется лишь в моменты времени, соответствующие высоким уровням внешнего входного сигнала и сигнала формирователя тактовых импульсов 1, следующего со скважностью, равной двум, в остальные моменты времени емкость интегратора 17 разряжена низким уровнем сигйала формирователя 1 тактовых импульсов. Далее импульсы пилообразной формы (фиг. 2в) подаются на сигнальный вход компаратора 19, а опорное напряжение с выхода фильтра 18 нижних частот, соответствующее среднему уровню входного сигнала интегратора 17, поступает на опорный вход кся паратора 19, где .происходит отсечка уровня сигнала, лежащего ниже уровня напряжения опоры (фиг. 2в). С выхода компаратора 19 сигнал (фиг. 2г) поступает на регенератор 20, где восстанавливается исходная форма внешнего сигнала, но очищенная от шумов (фиг. 2д). Стробирование сигнала в регенераторе 20 осуществляется отрицательным перепадом импульсов с формирователя 1 тактовых импульсов. С выхода регенератора 20 сформированный сигнал поступает на блоки 2, 3 и 4 опробования импульсных позиций. Эффективность предложенного устройства заключается в повышении помехоустойчивости при достижении и поддержании условий синхронизма в устройстве синхронизации по циклам. Формула изобретения Устройство синхронизации по циклам по авт. евид. № 565402, о т л и чающееся тем, что, с целью повышения Помехоустойчивости, введены «последовательно соединенные интегратор, фильтр нижних частот, компаратор и регенератор, выход которого подключен к входам N блоков опробования импульснЕЛХ позиций, причем выход формирователя тактовых импульсов подключен к другому входу регенератора и.ВХОДУ интегратора, выход которого подключен к другому входу компаратора, при этой на другой вход интегратора подан входной сигнал. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 565402, кл. Н 04 L 7/08, 1974 (прототип) .

i i Q 0 0 1 i i 01

II Lit i 1 -П rUJjTT . (.

jy7JiJiJVKH

1i, 1

j

H,i;j

S M ; J%nK4-rt

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| Устройство синхронизации по циклам | 1980 |

|

SU944134A2 |

| Устройство синхронизации по циклам | 1982 |

|

SU1075434A2 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

| Устройство цикловой синхронизации оконечных станций систем связи с импульсно-кодовой модуляцией | 1974 |

|

SU500594A1 |

| Устройство синхронизации сигналов | 1981 |

|

SU1021005A2 |

| Многофазный импульсный стабилизатор постоянного напряжения | 1983 |

|

SU1111140A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2005 |

|

RU2280956C1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2003 |

|

RU2231228C1 |

Авторы

Даты

1980-03-30—Публикация

1977-10-27—Подача