Vl

СП

4;

00 4 Изобретение относится к технике связи и может использоваться в мног канальных системах передачи сигнало с импульсно-кодовой модуляцией (ИКМ и дельта-модуляцией (ДМ). По основному авт. св. 944134 известно устройство синхронизации по циклам, содержащее последовательно соединенные формирователь тактовых импульсов, элемент запрета, делитель распределитель и регистр сдвига, кх второму входу которого и первому вх ду 3лемента задержки подключен второй выход формирователя тактовых им пульсов, вход которого объединен с первыми входами блоков опробования импульсных позиций, к вторьш входам которых, кроме первого, подключены выходы 3лe 4eнта задержки, к второму входу которого, а также к второму входу первого блока опробования импульсных позиций подключен выход первого элемента ИЛИ, при этом выходе регистра сдвига подключены соответственно к третьим входам блоков опробования импульсных позиций, узла перезаписи сигналов несоответствия, к первому входу первого расширителя и через элемент И к первым входам остальных расширителей., третьему вхо ду элемента И и соответствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета и первому входу которого и четвертому входу первого блока, опробования импуль.сных позиций подключен выход делителя-распределителя, при этом выхопы первого и третьего блоков опробования импульсных позиций подколочены к вторым входам соответствующих расширителей, а .выход второ го блока опробования импульсных позиций подключен к сооветствующему входу Узла перезаписи сигналов несоответствия, к другим соответствующим входам которого подключены выходы втсфого и третьего расширителей, а выход первого расширителя подключен к первсмлу входу первого дополнительного элемента И, причем выход первого блока опробования импульсных позиций подключен к входу первого накопителя, а выход третьего расширирителя подключен к соответствующему входу элемента И-ИЛИ, а также Первый и второй дополнительные элементы И, второй накопитель, последовательно соединенные первый триггер и блок инднксщии, второй.элемент ИЛИ и последовательно соединенные коммутатор второй триггер и третий дополнительный элемент И, выход которого подклю чен к установочным входам первого и второго накопителей, выходы которых подключены к первому и второму управляющим входам коммутатора, к первому разрешаквдему входу которого и к первому входу второго элемента ИЛИ подключен выход первого блока опробования импульсных позиций, а к второму разрешающему входу коммутатора, входу второго накопителя и второму входу второго элемента ИЛИ через первый дополнительный элемент И подключен второй выход- цервого расширителя, при этом выход второго элемента ИЛИ подключен к второму входу третьего дополнительного алемента И, выход второго накопителя подключен к второму входу второго триггера и первому входу первого триггера, к второму входу которого подключен второй выход коммутатора, а выход первого триггера подключен к второму входу элемента И и первому входу второго дополнительного элемента И, к втйрому и третьему входам которого подключены выходы первого и второго расширителей,а выход второго дополнительного элемента И подключен к соответствующим входам элемента И-ИЛИ, к дополнительному входу которого, а также дополнительному входу узла перезаписи сигналов несоответст-. ВИЯ подключен дополнительный выход элемента И 11. Однако данное устройство синхронизации по циклам имеет частые сбои синхронизации при низком соотношении сигнализации на его входе, т.е. недостаточную помехоустойчивость. Цель изобретения - повышение псЛлехоустойчивости при установившемся режиме синхронизации. Цель достигается тем, что в устройство синхронизации по циклам, содержащее последовательно соединенные формирователь тактовых импульсов, элемент запрета, делитель-распределитель и регистр сдвига, к второму входу которого и первому входу элемента задержки подключен второй выход формирователя тактовых импульсов, вход которого объединен с первыми входакш блоков опробования импульсных позиций, к вторым входам которых, кроме первого, подк.лючены выходы элемента задержки, к второму входу которого, .а также к второму входу первого блока опробования импульсных позиций подключен выход первого элемента ИЛИ, при этом выходы регистра сдвига подключены соот-ветственно к третьим входам блоков опробования импульсных позиций, узла перезаписи сигналов несоответствия, к первому входу первого расширителя и через элемент И к первым входам остальных расширителей, третьему входу Элемента И и соответствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета и первому входу первого элемента ИЛИ, к второму входу которого и четвертому входу первого блока опробования импульсных позиций подключен выход делителя-распределителя, при этом выходы первого и третьего блоков опробования импульсных позиций подключены к вторым входам соответствующих расширителей, а выход второго блока опробования импульсных позиций подключен к .соответствующему входу узла перезаписи сигнёшоЁ несоответ.ствия, к другим соответствуюишм входам которого подключены выходе второго и третьего расширителей, а выход первЬгр расширителя подключен к первому входу первого . дополнительного элемента И, причем выход первого блока опробования импульсных позиций подключен к входу первого накопителя, а выход третьего расширителя подключен к соответствующему входу элемента И-ИЛИ, а также первый и второй дополнительные элементы И, второй накопитель, последовательно соединенные первый триггер и блок индикации, а также второй элемент ИЛИ и последовательно соединенные .коммутатор, второй триггер и третий дополнительный элемент И, выход которого подключен к установленным входам первого и второго накопителей выходы которых подключены к первому и второму управлякицим входам коммутатора, к первому разрапающему входу которого, а также к первому входу второго элемента ЦЛИ подключен выход первого блока опробования импульсных позиций, а к второму разрешающему входу коммутатора, входу второго накопителя и второму входу второго элемента ИЛИ через первый дополнительный элемент И подключен второй выход первого расширителя, при этом выход второго -элемента ИЛИ подклю- чен к второму входу третьего допол-. нительного элемента И, выход второго накопителя подключен к второму входу второго триггера и первому входу первого триггера к второму входу которого подключен второй выход коммутатора, а выход первого триггера подключен к второму входу элемента И и первому входу второго дополнительного элемента И, к второму и третьему входам которого подключены выходы первого и второго расширителей, а выход второго дополнительного элемента И подключен к соответствующим входам элемента И-ИЛИ, к дополнительному входу которого, а также дополнительному входу узла перезаписи сигналов несоответствия подключен дополнительный выход элемента И,- введены последовательно со единенные блок-триггеров и четвертый дополнительный элемент И, к второму входу которого подключен дополнительный выход первого триггера, а выход подсоединен к дополнительному входу первого накопителя, вход

которого подключен к первому входу блока триггеров, к второму входу которого подключен выход третьего дополни тельного элемента И. .

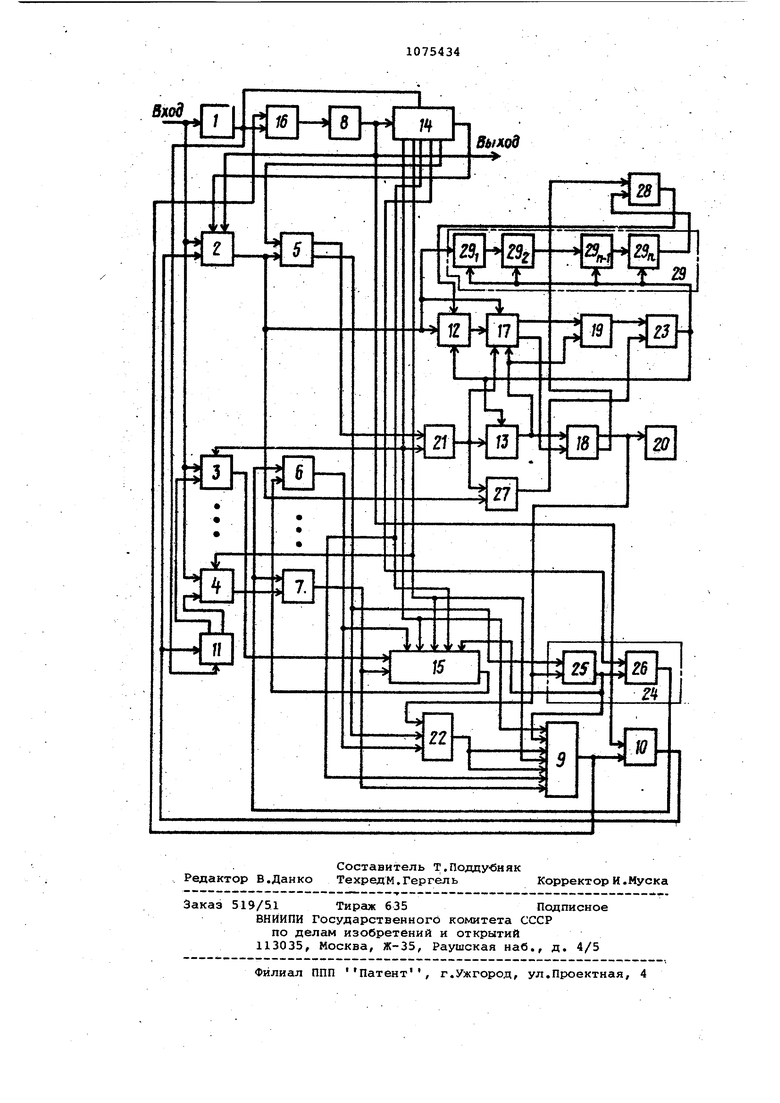

На чертеже представлена структурная электрическая схема устройства синхронизации по циклам.

Устройство синхронизации по IWKлам содержиf формирователь 1 тактовых импульсов, блоки 2-4 опробо0вания импульсных позиций,, расширители 5 - 7, 9влитель-.распределитель 8, элемент Й-ИЛИ 9, первый элемент ИЛИ 10, элемент. 11 задержки, накопители 12 и 13, регистр 14 сдвига, узел 15 перезаписи сигналов несоот5ветствия, элемент 16 запрета, коммутатор 17, триггеры 18 и 19, блок 20 индикации, первЕ й, второй и третий дополнительные элементы И 21 - 23., элемент И 24, содержащий первый и

0 второй элементы И 25 и 26, второй элемент ИЛИ 27, четвертый дополнительный элемент И 28, блок 29 триггеров , содержащий триггеры ,29 29 ,

Устройство-, синхронизации по цик5лам работает .следующим образом.

В состоянии синхронизации импульсы тактовой частоты с выхода фор мирователя 1поступают на один из входов регистра 14 сдвига, а че0рез элемент 16 запрета на вход делителя-распределителя 8. На выходе делителя-распределителя 8 фо{жируется последовательность импульсов, следукхдих с цикловой частотой, а на

5 первом - пятом выходах регистра сдвига формируются импульсы, задержанные относительно выходного импульса делителя-распределителя 8 на один пять периодов тактовой частоты соот0ветственно. Входной групповой сигнал с ИКМ или с ДМ поступает на соответствующие входы блоков 2 - .4 опробования, на другие входы которых подаются опробывающие импульснью сигналы.

5

В случае опробования блоком 2 импульсных позиций, синхросимволы на которых отсутствуют, сигналы сшибки с его выхода поступают на вход накопителя 13,.

0

Несмотря на то, что в состоянии синхронизма на вход накопителя 13 поступают импульсы сшибки, заполнения (счета этих импульсов).накопителя 13 не происходит, так как в это

5 время с выхода четвертого дополнительного элемента И 28 на дополнительный вход накопителя 13 поступает сигнал, запрещающий счет импульсов этим накопителем 13. Этот запре0щающий сигнал изменяется на сигнеш разрешения счета импульсов сигнгилов ошибок накопителем 13 только поедав опрокидывания блока 29, т.е. только после заполнения импульсами сигналов сишбки триггеров 29(-29п блока 29.

5

Таким образом, в режиме (Синхронизма сигнал ошибки (сигнал включений режима поиска) на вход ком14утатора 17 поступает с выхода накопителя 13 только после .заполнения всех триггеров 2У -;г9п блока 29 и накопителя 13, что исключает ложные сбои установившейся синхронизации по циклгим при низких соотношениях (Жгнал-шум.

После достижения синхронизации по циклам, при которой блок 2 опробывает позиции с синхросимволами цикла, на выходе дополнительного элемента И 21 формируется сигнгип синхронизма. После заполнения Накопителя 12 триггер 19 устанавливается в состояние, при котором на его втором выходе формируется сигнал логической единицы, разрешающий поступление сигнсшов с выхода п триггера 29|) на дополнительный вход накопителя 13. В исходном состоянии, задаваемом, выходными импульсами элемента И 23, триггер 29ц находится в состоянии, при котором на вход четвертого .дополнительного элемента И 28 с его выхода поступает сигнал логической единицы. Таким образом, подсчет накопителем 13 импульсов сигналов

ошибок, поступающих на его вход непосредственно а выхода блока 2, будет запрещен. В этом случае сигналы сшибок подсчитываются последовательно триггерами 294-:29f, блока 29 и лишь после опрокидывания триггера 29f, подсче1Т ошибок продолжается с помощью накопителя 13.

Таким образом, для включения режима поиска в устройстве синх|ронизации поциклам в установившемся режиме опробования синхропозиций цикла необходимо значительно большее количество сшибок, чем в режиме поиска для подтверждения правильности этого режима.

Это исключает ложные сбои синхрониз щии при повышенном содержании синхросимволов цикла, которое наблюдается при низких соотношениях сигнал-шум на входе устройства.

Технико-экономическая эффективность изобретения заключается в повыиёнии помехоустойчивости предлагаемого устройства при установившемся режиме синхронизации за счет исключения ложных сбоев синхронизации при низких соотношениях сигналшум .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1980 |

|

SU944134A2 |

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU725257A2 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| СПОСОБ СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2812335C1 |

| Устройство для асинхронного сопряжения цифровых потоков | 1986 |

|

SU1312556A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ КОДОВЫХ КОМБИНАЦИЙ | 2023 |

|

RU2810267C1 |

| Устройство синхронизации по циклам | 1976 |

|

SU618858A1 |

| Устройство для выделения тактового колебания | 1978 |

|

SU788408A2 |

УСТРСЯ СТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ по авт.св. 944134, отличающее с я тем, что, с целью повсяаения помехоустойчивости при установившемся режиму синхронизгщни,. в иего введеиы последовательно соединенные блок Т1риггеров и четвертый дополнительный элемент И, к второму входу подключен дог олнительный шхсщ первого триггерс1, a выход подсоединен к дополнительному входу первого накопителя, вход которого подключен к первому входу блока триггеров, к втсфому входу которого подключен выход третьего дополнительного элемента И.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство синхронизации по циклам | 1980 |

|

SU944134A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1984-02-23—Публикация

1982-09-03—Подача