(54) УСТРОЙСТВО СИНХРОНИЗАЦИИ ПО ЦИКЛАМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство синхронизации по циклам | 1974 |

|

SU565402A1 |

| Устройство синхронизации по циклам | 1982 |

|

SU1075434A2 |

| Устройство синхронизации по циклам | 1977 |

|

SU725257A2 |

| Приемник синхросигнала | 1986 |

|

SU1424129A1 |

| Устройство для индикации синхронизма | 1980 |

|

SU944131A1 |

| Устройство для цикловой синхронизации | 1989 |

|

SU1778913A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ СИСТЕМЫ С ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ | 1970 |

|

SU279701A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

1

Изобретение относится к технике связи и может использовано в многоканальных системах передачи сигналов с импульсно-кодовой модуляцией и дельта-модуляцией.

По основному апт. св. № 565402 известно устройство синхронизации по циклам, содержащее последовательно соединенные формирователь тактовых импульсов, элемент запрета, делитель-распределитель и регистр сдвига, к второмувходу которого и первому входу элемента задержки подключен выход формировате-. ля тактовых импульсов, вход которого объединен с первыми входами блоков опробывания импульсных позиций, к вторым входам которых, кроме первого, подключены выходы элемента задержки, к Второму входу которого, а также к второму входу первого блока опробывания импульсных ПО31ЩИЙ подключен выход первого элемента ИЛИ, при этом Выходы регистра сдвига подключены соответственно к третьим входам блоков

опробывания импульсных позиций, узла перезаписи сигналов несоответствия, к первому входу первого расшириуеля и через элемент И к первым входам остальных расширителей, третьему входу элемента И и соответствующим входам элемента И-ИЛИ, выход которого подключен к второму входу элемента запрета и первому входу первого элемента

,д ИЛИ, к второму входу которого и четвертому входу первого блока опробывания импульсных позиций подключен выход делителят-распределителя, при этом выход первого и третьего блоков опробывания

5 импульсных поз|щий подключены к )лторым входам соответствующих расширителей, а Выход второго блока onpc Gi-iBaНИЯ импульсных позицией ПОДКЛЮЧ«Е1 к

соответствующему входу узла переаапп20 си сигналов несоответствия, к другим соответствующим входам которого подключены выходы второго и третьего рясщирителей, а выход первого pnciiiiTfunoля подключен к первому входу

И, причем выход первого блока опробываиия импульсных позиций подключен ко входу первого накопителя, а выход третьего расширителя подключен к соответствующему входу элемента И-ИЛИ ClJ

Однако известное устройство характеризуется низкой помехоустойчивостью.

Цель изобретения - повышение помехоустойчивости.

Цель достигается тем, что в устройство синхронизации по циклам введены первый и второй дополнительные элементы И, второй накопитель.последовательjfo соединенные первый триггер и блок индикации, а также второй элемент ИЛИ и последовательно соединенные коммутатор, второй триггер и третий дополнительный элемент И, выход которого подключен к установочным входам первого и второго накопителей, выходы которых подключены к первому и второму управляющим входам коммутатора, к первому разрешающему входу которого, а также к первому входу второго элемента ИЛИ подкт ючен выход первого блока опробывания импульсных позиций, а к второму разрешающему входу KOMMyTaTqja, входу накопителя .и второму входу второго элемента ИЛИ через пе1)Вый дополнительный элемент И подключен выход первого расширителя, при этом выход второго элемента ИЛИ подключен к второму входу третьего дополнительного элемента И, выход второго накопителя подключен к второму входу второго триггера и первому входу первого триггера, к второму входу которого подключен выход коммутатера, а выход первого триггера подключен к второму входу элемента И и первому входу второго дополнительного элемента И, к второму, и третьему входам которого подключены выходы первого и второго расширителей, а выход втсрого дополнительного элемента И подключен к соответствующим входам элемента ИИЛИ, к дополнительному входу которого, а также дополнительному входу узла. перезаписи сигналов несоответствия подключен дополнительный выход элемента И

Кроме того, элемент И выполнен в виде последовательно соединенных первого элемента и второго элемента И, при этом входы первого элемента И являются первым и вторым входами элемента И вход второго элемента И является третьим входом элемента И, а выходы первого и второго элементов И являются соответственно дополнительными выходом и выходом элемента И.

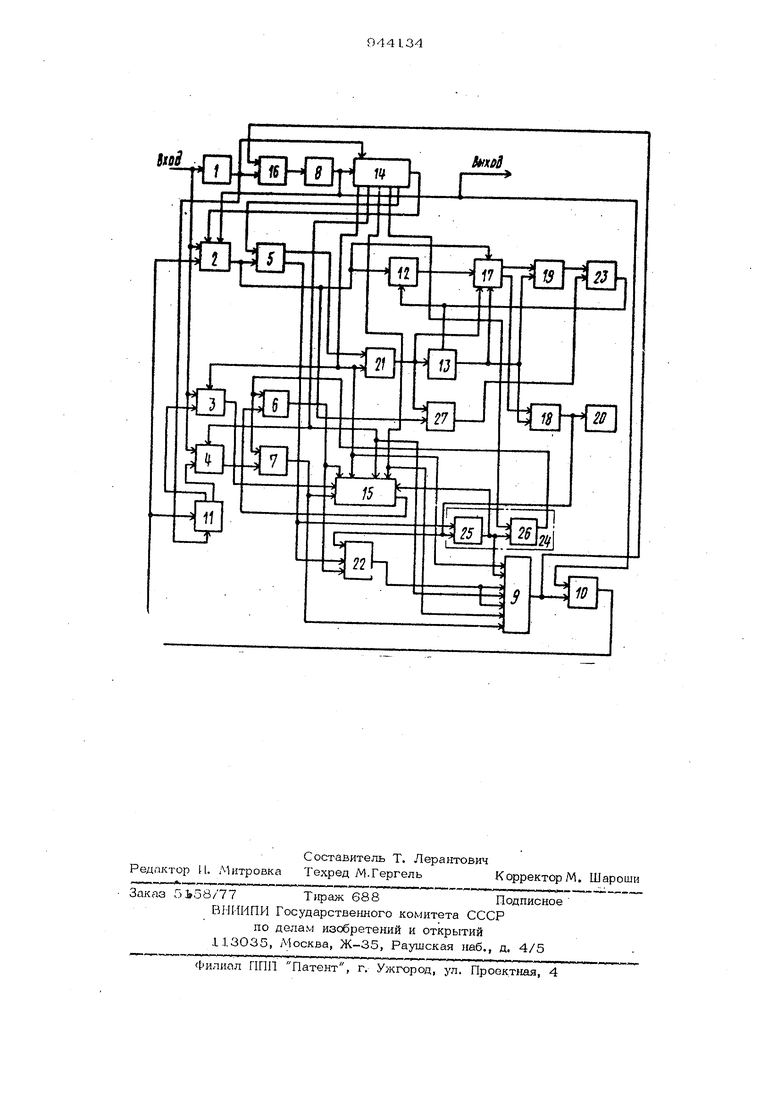

На чертеже приведена структурная электрическая схема устройства.

Устройство синхронизации по циклам содержит формирователь 1 тактовых импульсов, блоки 2-4 опробывания импульсных позиций, расширители 5 - 7, делитель-распределитель 8, элементы ИИЛИ 9, первый элемент ИЛИ 10, элемент задержки 11, накопители 12 и 13, регистр 14 сдвига, узел 15 перезаписи сигналов несоответствия, элемент запрета 16, коммутатор 17, триггеры 18 и 19, блок 2О индикации, дополнительные элемента И 21 - 23, элемент И 24, содержащий первый и второй элементы И 25 и 26, второй элемент ИЛИ 27.

Устройство работает следующим образом.

В состоянии синхронизации импульсы

тактовой частоты с выхода формирователя 1 через элемент загфета 16 поступают на-вход делителя-распределителя 8, осуществляющего деление частоты сле.дования тактовых импульсов до частоты

следования циклов.

На первом - пятом выходах регистра 14 сдвига формируются импульсы, задержанные относительно выходного импульса делителя-распределителя 8 на один - пять периодов тактовой частоты соответственно. На вход блока 2 опро- бывания импульсных позиций в режиме синхронизма с выхода делителя-распределителя 8 через первый элемент ИЛИ 10 поступает опробывающий сигнал с частотой следовения цикла, а на входы блоков 3 и 4 опробывания импульсных позиций с выходов элемента задержки 11 поступают такие же последовательности импульсов, но задержанные на один и два периода тактовой частоты соответственно. В установившемся режиме (в режиме синхронизма) блок 2 огфобывания импульсных позиций опробывает чередующиеся символы 1-0 - 1-О... синхросигнала цикла, а блоки 3 и 4 опробывания импульсных позиций опробывают символы, чередующиеся по случайному закончу. Если блок 2 опробывания импульсных позиций

опробывает пары символов, среди которых имеются пары одинаковых символов, разделенных временем цикла, то на выходе блока 2 опробьшания импульсных позиций формируются импульсы несоответствия отробываемых символом символам синхросигнапа цикла( сигнал ошибки). В случае отсутствия на выходе блока 2 опробывания импульсных позиций сигнала ошибки гфи опробывании лары символов, разде- ленных временем цикла, на выходе первого дополнительного элемента И 21 формируется сигнал синхронизма т.е. сигнал соответствия опробываемых символов символам синхросигнала цикла. Сигналы ошибок поступают на вход первого накопителя 12, а сигналы синзфонизма поступают на вход второго накопителя 13 (сигналов синхронизма). При частоте следования сигналов ошибки большей частоты следования сигналов синзфонизма, первым заполняется первый накопитель 12. Сигнал с выхода первого накопителя 12 разрешает поступление сигнала ошибки через коммутатор 17 на вход втсрого триггера 19. Псюледний ус танавливается в состояние, при котором сигнал с выхода второго элемента ИЛИ 2 через третий дополнительный элемент И 23 устанавливает накопители 12 и 1 в исходное состояние. Таким образом, в режиме синхронизма, при котором чаС тота следования сигналов синхронизма вьпце частоты следования сигналов , второй накопитель 13 сигналов синхронизма заполняется раньше первого накопителя 12. Это обеспечивает систематический сброс первого накопителя 12 в исходное состояние и предотвращает переход устройства в режим поиска (сбой синхронизма) при искажениях последовательности сишфосимволов. Сигналами с одного из выходов коммутатора 17 или с выхода второго накопителя 13 первый триггер 18 переводится в соответствующее состояние, обеспечивающее соответственно установление режима поиска или режима синхронизма. Сигнал с выхода первого триггера 18 поступает на входы второго дополнительного элемента И 26 и элемента И 25, а также на вход блок 2О индикации с помощью которого индицируется режим работы устройства (поиск или синхронизм). Индикация режима работы позволяет оценить степень помехоустойчивости синхронизма по циклам и принять необходимьш меры по повыше нию верности приема символов группово го сигнала (например, путем более тщательного подбора порога отсечки шумового сигнала, изменения с иентацин антенны и т.п.). Таким образом, устройство синзфонизации по циклам обеспечивает повьш1е кие помехоустойчивости при уменьшении соотношения сигнал/шум на его входе. Формула изобретения 1. Устройство синхронизации по цик лам по авт. св. N 5654О2, отличающееся тем, что, с целью повышения помехоустойчивости, введены первый и второй дополнительные элементы И, второй накопитель, последовательно соединенные первый триггер и блок индикации, а также второй элемент ИЛИ и последовательно соединенные коммутатор, второй триггер и третий дополнительшый элемент И, выход которо го подключен к установочным: входам первого и второго накопителей, вькоды которых подключены к первому и второму управляющим входам коммутатора, к первому разрешающему входу которого, а также к первому входу элемента ИЛИ подключен выход первого блока опробывания импульсных позиций, а к второму ра ешающему входу ком мутатора, входу второго накопителя и втсфому входу второго элемента ИЛИ через первый дополнительный элемент И подключен второй Выход первого расялирителя, при этом выход элемента ИЛИ подключен к второму входу третьего дополнительного элемента И, выход второго накопителя подключен к второму входу второго триггера и первому входу первого триггера, к второму входу которого подключен второй выход коммутаTqpa, а выход первого триггера подключен к второму входу элемента И и первому входу второго дополнительного элемента И, к второму и третьему входам подключены выходы первого и расшщ)ителей, а выход BTqporo дополнительного элемента И подключен к соответствующим входам элемента ИИЛИ, к дополнительному входу которого, а также дополнительному входу узла перезаписи сигналов несоответствия подключен дополнительный выход элемента И. 2. Устройство по п. 1, о т л и ч а ю щ е е с k тем, что элемент И выполнен в виде последовательно соединённых первого и второго элементов И, при этом входы первого элемента И являются первым и вторым входами элемента И, вход второго элемента И является третьим входом дпемента И, а выходы первого и второго эпе ментов И являются соответственно дополнительным выходом и выходом элемента И. Источники информации, щ йнятые во внимание при экспертизе 1. Автсфское свидетельство СССР N 5654О2, кЛ. Н 04L 7/О8, 1974 (ЕРОТОТИП).

Авторы

Даты

1982-07-15—Публикация

1980-07-16—Подача