(54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРЕРЫВАНИЕМ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания программ | 1978 |

|

SU736101A1 |

| Микропрограммное устройство для обработки прерываний | 1983 |

|

SU1126956A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Устройство для отладки программ | 1988 |

|

SU1594546A1 |

| Устройство прерывания | 1982 |

|

SU1084795A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство для управления прерыванием программ | 1981 |

|

SU978150A1 |

| Устройство для формирования сигналов прерывания | 1986 |

|

SU1341640A1 |

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Многоканальная система управления распределением ресурсов в вычислительном комплексе | 1987 |

|

SU1432580A1 |

I

Изобретение относится к области вы числительной техники и может найти применение в вычислительных системах, работающих в реальном масштабе времейи.

Известны устройства i для управления прерьшаниями, содержащие схему приоритета, выполйеиную на элементах коммутации, схему сброса, триггеры для запоминания запросов, триггеры блокироаки, которые при новом поступлении только что обслуженного запроса запрещают, его прием на обработку до завершения обслуживания запросов, ранее принятых в устройство.

Недостатками данных устройств явлйется большая вероятность несвоевременного обслуживания запросов из-за отсутствия возможности снятия блокировки при наличии менее приоритетных запросов повторной обработки более приоритет ных запросов.

Кроме того, возможна потеря повторН.ЫХ запросов, так как они временно не

фиксируются за период действия блокировки.

Наиболее близким по технической сущйости к изобретению является устройство

управления прерыванием программ, содержащее Nj -разрядные регистры прерывйний и блокировки запросов, узел выбора приоритета и элемент ИЛИ. Прямой выход -го. триггера регистра прерьюйний подключен к -му входу узла выбора приоритета i -и выход кото.рого является i -ым выходом устройства i -и вход гашения которого подклк чен к единичному входу i -го триггера блокировки и кулевому входу i -го триггера регистра прерываний.

Недостатком этого устройства является то что при работе в реальном времени запросы, поступающие на обработку в систему, могут остаться не обслуженными и теряться.

Цель изобретения состоит в сокращении числа необслуженных запросов

Поставленная цепь достигается тем, то в предложенное устройство введены егибтр очереди запрсюов, регистр дебло кировки запроса, элемент И и элемент задержки. Прямой и инверсный выходы 5 I- -го триггера регистра блокировки запросов подключены соответственно к первым единичным входам i -ых триггеров регистра очереди запросов, второй единичный вход которого соединен с i -ым 10 аходом запроса устройства и регистра прерьюаний, соединенного вторым единичКьЩ вхоДбМ с выходом -го элемента ИЛИ, первый аход которого подключен к первому единичному входу i -го триг- |5 гера регистра деблокировки запроса и -му аходу запроса устройства. Второй вход I -го элемента ИЛИ соединен со вторым единичным аходом i -го триггера регистра деблокировки запроса иО прямым выходом i -го Триггера регистра очереди запросов, первый и вторые йулевые входы которого, соединенные соответственно с первым и вторым нулевьпут входами i -го триггера регистра деблокировки запроса, подключены Соответственно через элемент задержки к выходу элемента И и i -му выходу узла в ыбора приоритета. Первый и второй нулевые входы i -го триггера регист- 30 ра блокировки запросов соединены соответственно с прямым выходом i -го триггера регистра деблокировки запроса и выходом элемента И, аходы которого подключены к инверсным.выходам триг- 35 геров регистра прерываний ( 1N ),

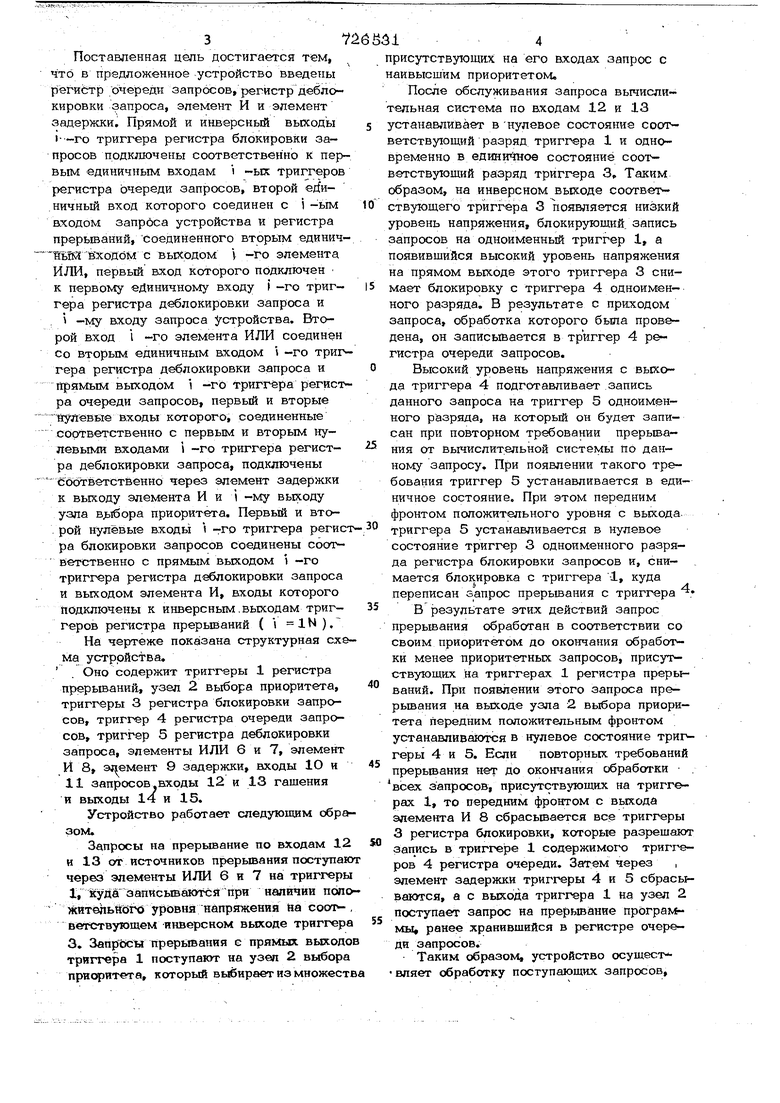

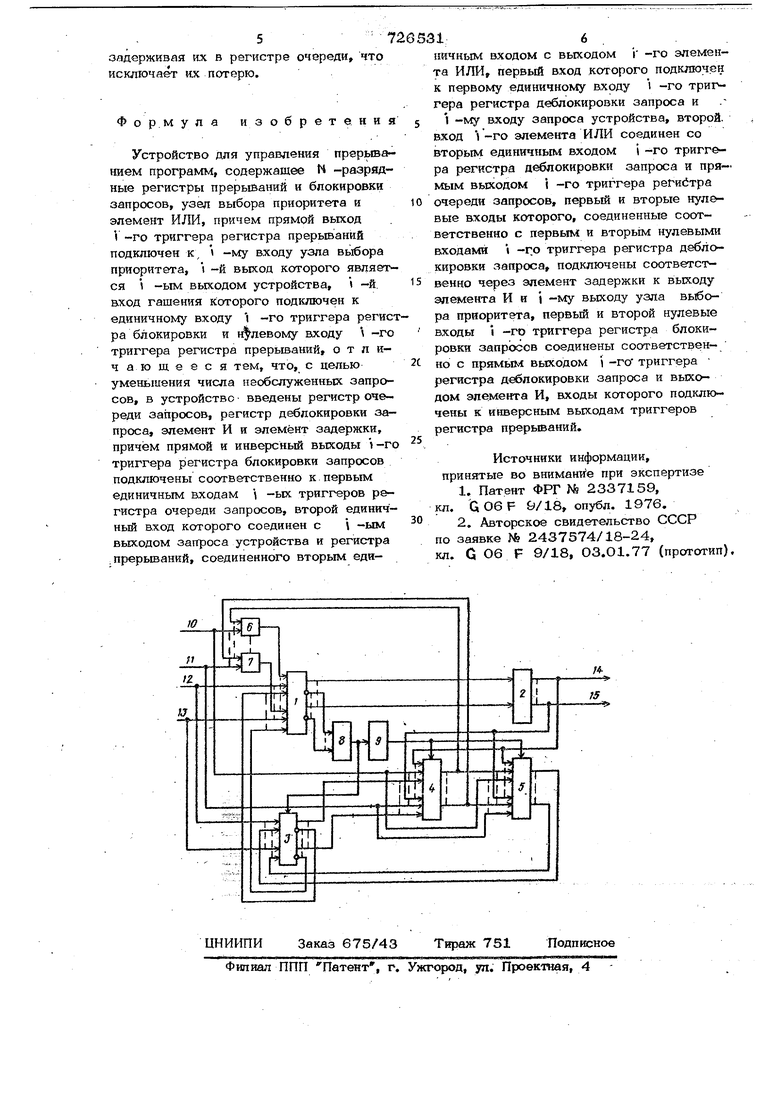

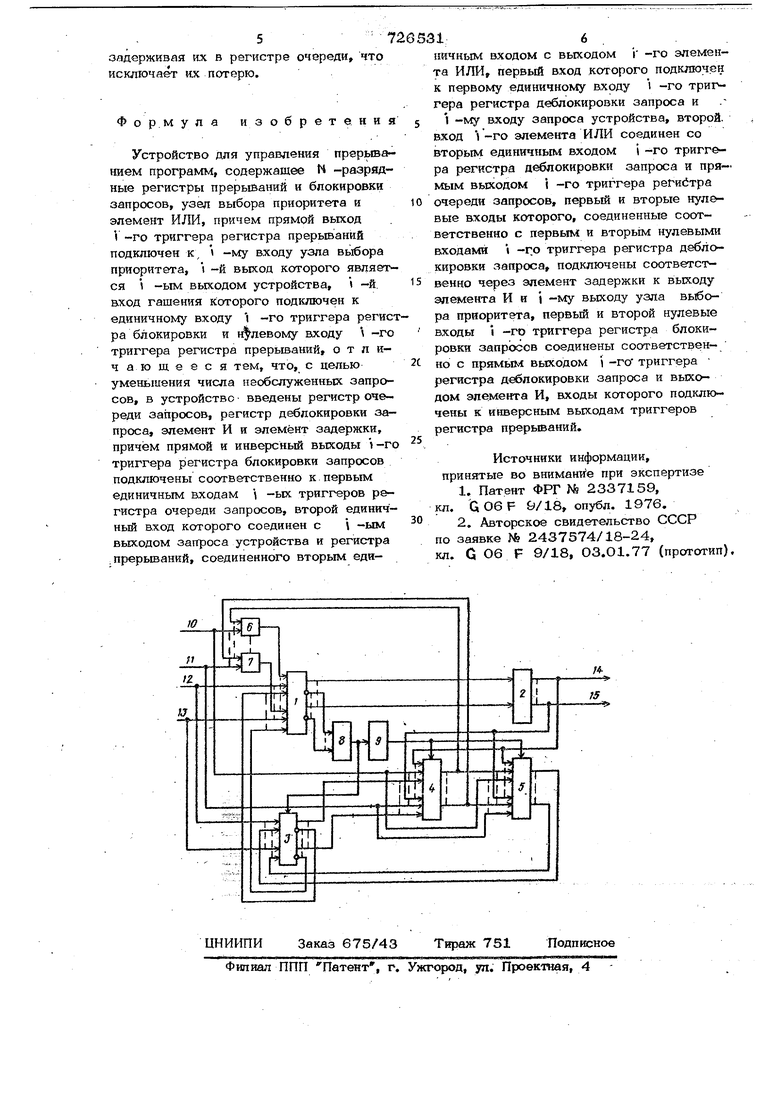

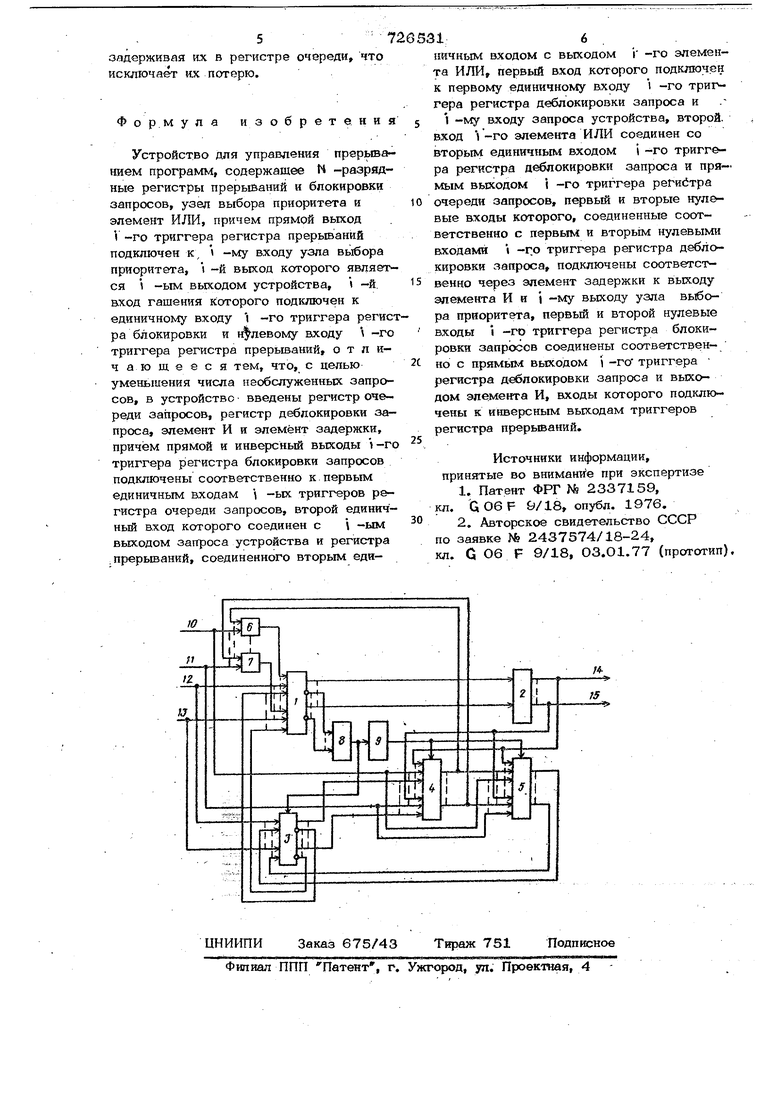

На чертеже показана структурная схема устройства,

Оно содержит триггеры 1 регистра прерьюаний, узел 2 выбора приоритета, 40 триггеры 3 регистра блокировки запросов, триггер 4 регистра очереди запросов, триггер 5 регистра деблокировки запроса, элементы ИЛИ 6 и 7, элемент И 8, элемент 9 задержки, входы 10 и 45 11 запросов-ВХОДЫ 12 и 13 гашения и выходы 14 и 15.

Устройство работает следующим образом.

Запросы на прерывание по входам 12 SO и 13 суг источников прерьшаНИН поступают через элементы ИЛИ 6 и 7 на триггеры 1, кудазаписываются при наличии попожйтепьного уровня напряжения на соот- , ветствутощем инверсном выходе триггера 55 Зф ЗапрсЛы прерыватшя с прямых выходов триггера 1 поступают на узел 2 выбора npHqpHTSTa, который выбирает из множества

присутствующих на его входах запрос с наивысшим приоритетом.

После обслуживания запроса вычислительная система по аходам 12 и 13 устанавли)вает в нулевое состояние соответствующий разряд триггера 1 и одновременно в единичное состояние соответствующий разряд триггера 3, Таким образом, на инверсном выходе соответствующего триггера 3 появляется низкий уровень напряжения, блокирующий/запись запросов на одноименный триггер 1, а появившийся высокий уровень напряжения на прямом выходе этого триггера 3 снимает блокировку с триггера 4 одноименного разряда. В результате с приходом запроса, обработка которого была проведена, он записывается в триггер 4 регистра очереди запросов.

Высокий уровень напряжения с выхода триггера 4 подготавливает запись данного запроса на триггер 5 одноименного разряда, на который он будет записан при повторном требовании прерывания от Вычислительной системы по данному запросу. При появлении такого требования триггер 5 устанавливается в единичное состояние. При этом передним фронтом положительного уровня с выхода, триггера 5 устанавливается в нулевое состояние триггер 3 одноименного разряда регистра блокировки запросов и, снимается блокировка с триггера 1, куда переписан запрос прерьшания с триггера

В результате эти.х действий запрос прерывания обработан в соответствии со своим приоритетом до окончания обработ ки менее приоритетных запросов, присутствующих На триггерах 1 регистра прерываний. При появлении этого запроса пре- рьтания на выходе узла 2 выбора приоритета передним положительным фронтом устанавливаются в нулевое состояние триггеры 4 и 5. Если повторных требований прерывания нет ДО окончания обработки всех запросов, присутствующи.х на триггерах 1, то передним фронтом с выходи элемента И 8 сбрасьгоается все триггеры 3 регистра блокировки, которые разрешаю запись в триггере 1 содержимого триггеров 4 регистра очереди. Затем через , элемент задержки триггеры 4 и 5 сбрасываются, а с выхода триггера 1 на узел 2 поступает запрос на прерывание программы, ранее хранившийся в регистре очереди запросов.

Таким образом, устройство осуществляет обработку поступающих запросов. задерживая ax в регистре очереди, что исключает як потерю. Формула изобретения Устройство для управления прерьюанием программ, содержащее М -разрядные регистры прерываний и блокировки запросов, узел выбора приоритета и элемент ИЛИ, причем прямой выход V-го триггера регистра прерываний подключен к, -му входу узла вьйора приоритета, i -и выход которого являет ся 1 -ым выходом устройства, -и. В.ХОД гашения к:оторого подключен к единичному входу ( -го триггера регис ра блокировки и нулевому входу -го триггера регистра прерываний, отличающееся тем, что, с целью уменьшения числа необслуженных запросов, в устройство введены регистр очереди запросов, регистр деблокировки запроса, элемент И и элемент задержки, причём прямой и инверсный выходы -г триггера регистра блокировки запросов подключены соответственно к первым единичным входам -ых триггеров регистра очереди запросов, второй единичный вход которого соединен с -ым выходом запроса устройства и регистра .прерьшаний, соединенного вторым единичным входом с выходом I -го элемента ИЛИ, первый вход которого подключен к первому единичному входу i -го триггера регистра деблокировки запроса и I -му входу запроса устройства, второй, вход V-ro элемента ИЛИ соединен со вторым единичным входом i -го триггера регистра деблокировки запроса и прямым выходом i -го триггера регийтра очереди запросов, первый и вторые нулевые входы которого, соединенные соответственно с первым и BTOpbiM нулевыми входами I -г.о триггера регистра деблокировки запроса, подключены соответственно через элемент задержки к выходу элемента И и i -му выходу узла выбора приоритета, первый и второй нулевые входы I -го триггера регистра блокировки запросов соединены соответственно с прямым выходом i -ГО триггера регистра деблокировки запроса и выходом элемента И, входы которого подключены к инверсным выходам триггеров регистра прерываний. Источники информации, принятые во внимание при экспертизе 1.Патент ФРГ № 2337159, кл. ia06F 9/18, опубл. 1976. 2.Авторское свидетельство СССР по заявке № 2437574/18-24, кл. G Об F 9/18, ОЗ.О1.77 (прототип).

Авторы

Даты

1980-04-05—Публикация

1977-10-10—Подача