Изобретение предназначено для использования в процессах прокатки и может быть использовано для определения наличия металла в валках реверсивного обжимного или балочного прокатных станах.

Наиболее близким по технической сущности и достигаемому результату к изобретению является устройство, содержащее сдвигающее запоминающее устройство для хранения результатов измерения сигналов на М слов (элементов одной выборки), вычислительное устройство (вк.лючающее схему управления и схему сравнения результатов измерений) и схему сравнения статистики с порогом (компаратор), причем вход запоминающего устройства соединен с выходом аналогово-цифрового преобразовател.я, а выход со входом вычислительного устройства, вхсд которого соединен также с аналого-цифровым преобразователем, а выход через схему И - со схемой сравнения с порогом 1,

В силу того, что принимаемые сигна.71к г«5дулированы по амплитуде в соответствии с формой диаграммы направленности антенны локатора, в принимаемых данных при наличии сигнала noaeляется характерный ранговый порядок, благодаря чему оказывается возможным применение критерия проверки гипотезы о тренде. При этом сдвигающее эапоминакяцее устройство при поступлении каждого очередного результата измерения сдвигает всю информацию, хранимую в нем, на 1 сщрес.

Однако при произвольном характере поведения сигнала, не имеющего характерного рангового порчдка (например, тока якоря двигателя, стйтического момента прокатки, давления на валки) в интервалы времени нахождения металла в валках прокатного стана, т. е. для проверки гипотезы о сдвиге сигнала, известное устройство не может обеспечить приемлемой вероятности правильного обнаружения сигнала.

Целью изобретения является повышение надежности устройства в работе во всех фазах реверсивной прокатки, включая захват, прокатку, выброс и паузу, и сокращение .времени определения наличия мета.71ла в валках.

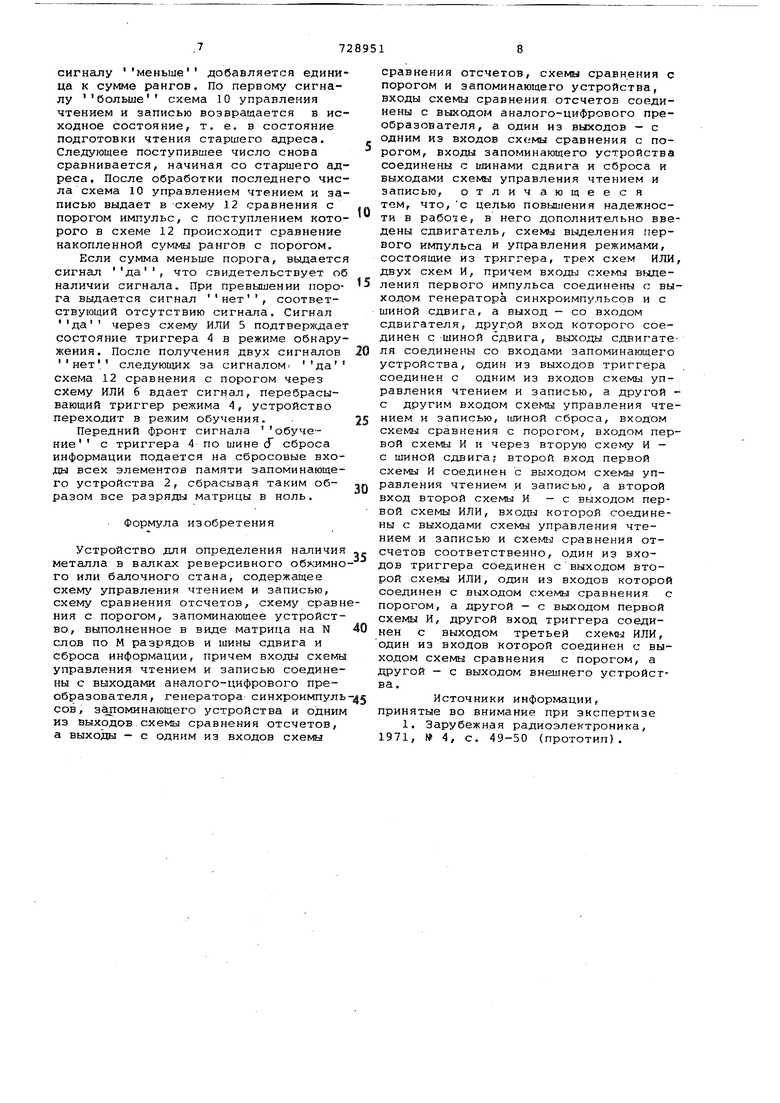

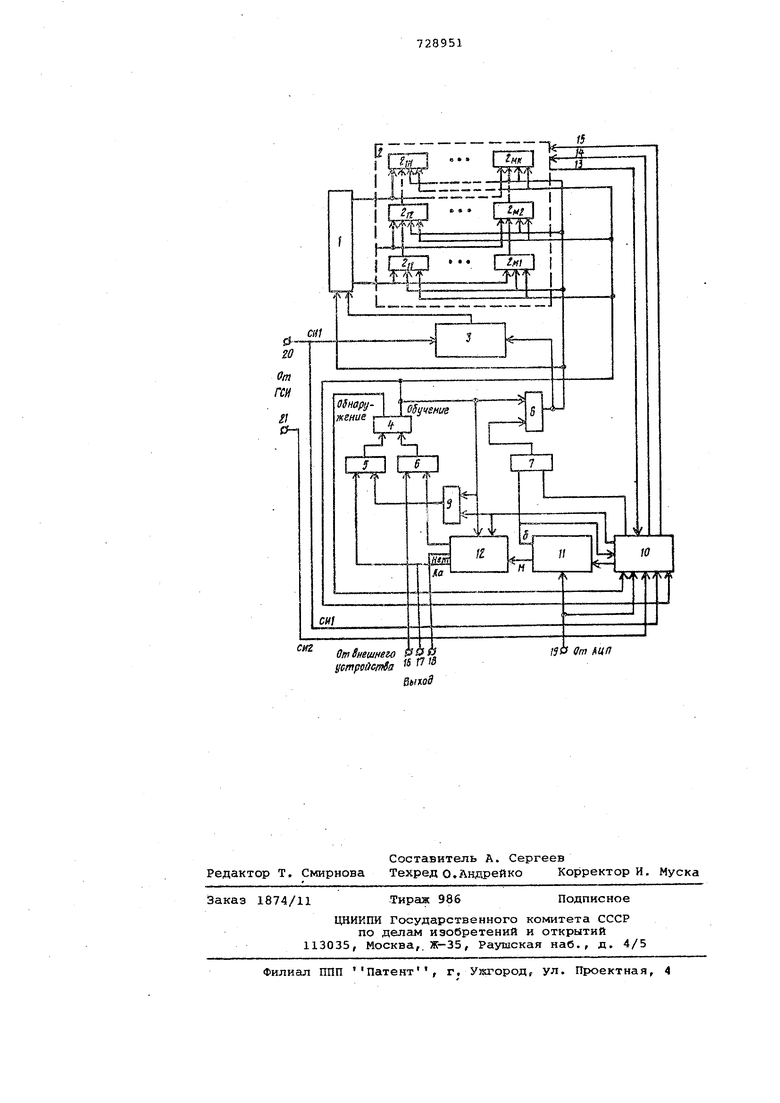

Это достигается тем, что устройств содержит схему управления чтением и записью, схему сравнения отсчетов, схему сравнения с порогом, запоминающ устройство, выполненное в виде матриц на N слов по М разрядов и шины сдвига и сброса информации, причем входы схе мы управления чтением и записью соеди нены с выходами аналого-цифрового пре образователя, генератора синхроимпуль сов, запоминающего устройства и одним из выходов схемы сравнения отсчетов, а выходы -- с одним из входов схемы сравнения отсчетов, схемы сравнения с .порогом и запоминающего устройства, входы схемы сравнения отсчетов соединены с выходом аналого-цифрового преобразователя, а один из выходов - с о ним из входов схемы сравнения с порогом, входы запоминающего устройства соединены с шинами сдвига и сброса и выходами схемы управления чтением и записью. Кроме того, устройство содер жит дополнительно сдвигатель, схемы выделения первого импульса и управления режимами, состоящие из триггера, трех схем ИЛИ, двух схем И, причем входы схемы выделения первого импульса соединены с выходом генератора син хроимпульсов и с шиной сдвига, а выход - со входом сдвигаталя, другой вход которого соединен с шиной сдвига Выходы сдвигателя соединены со входами запоминающего устройства, один из выходов триггера соединен одним из входов схемы управления чтением и зап СЬЮ, а другой - с другим входом схемы управления чтением и записью, шиной сброса, входом схемы сравнения с поро гом, входом первой схемы И и через вторую схему И - с шиной сдвига; второй вход первой схемы И соединен с выходом управления чтением и записью, на второй вход второй схемы И - с выходом первой схемы ИЛИ, входы которого соединены с выходами схемы управления чтением и записью и схемы сравнения отсчетов соответственно один из входов триггера соединен с выходом второй схемы ИЛИ, один на входов которой соединен с выходом сравнения с порогом, а другой - с выходом первой .схемы И, другой вход триггера соединен с выходом третьей схемы ИЛИ, один из выходов которой соединен с выходом схемы сравнения с порогом, а другой - с выходом внешнего устройства. На чертеже представлена структурная схема предлагаемого устройства, О.на содержит сдвигатель 1, матричное запоминающее устройство 2, состоящее из элементов памяти на триггерах схему 3. выделения первого импульса, схему управления, режимами, состоящую из триггера 4, схем ИЛИ 5-7,схем И 8 и 9( схему 10 управления чтением и записью, схему И сравнения отсчетов, схему 12 сравнения с порогом, шину сдвига информации и шину f сброса информации . Входы сдвигателя 1 соединены с шийой а сдвига информации и выходом схемы 3 выделения первого импульса, а выходы сдвигателн 1 - со входами элементов памяти запоминающего устройства 2, входы ка кдого из которых соединены также с шинами сдвига ct и сброса f информации соответственно и шинают 13-15 чтения, записи и управле- ния. Входы схемы 3 выделения первого импульса соединены с выходом генератора синхроимпульсов и шиной а сдвига информации,.а выход - со входом сдвигателя 1, Входы триггера 4 через схемы ИЛИ 5 и б и схему И 9 соединены с выходами схемы 10 управления чтением и записью и схемы 12 сравнения с порогом, а также с входной клеммой 16 подачи сигнала от внешнего устройства. Выходы триггера 4 соединены со входами схемы 10 управления чтением и записью и схемы 12 сравнения с порогом, с шиной (f сброса информации, входом схемы И 9 и через схему И 8 - с шиной d сдвига информации. Входы схемы 10 управления чтением и записью соединены о выходами триггера 4, аналого-цифрового преобразователя, генератора синхроимпульсов, схемы 11 сравнения отсчетов и шиной 13 чтения. Выходы схемы 10 управления чтением и записью соединены с шинами записи 14 и управления 15, входом схемы 11 сравнения отсчетов, входом схемы 12 сравнения с порогом, входом схемы И 9 и через схему ИЛИ 7 и схему И 8 с шиной О сдвига информации. Входы схемы сравнения отсчетов 11 соединены с одниМ из выходов схемы 10 управления чтением и записью и выходом аналогово-цифрового преобразователя, а выходы - со входом схемы 12 сравнения с порогом, с одним из в.ходов схемы 10 управления чтением и записью и через схему ИЛИ 7 и схему И 8 с шиной Q сдвига информации. Входы схемы 12 сравнения с порогом соединены с одним из выходов схемы10 управления чтением и записью, выходом схемы 11 сравнения отсчетов и выходом триггера 4, а выходы - с выходными клеммами 16-18 и входами схем ИЛИ 5 и 6, Работа предлагаемого устройства основана на реализации непараметрического двухвыборочного рангового критерия Вилкоксона проверки гипотезы о сдвиге сигнала. Согласно этому критерию необходимо запоминание обучающей и проверяемой выборок результатов измерения сигнала, построение вариационного ряда их, подсчет суммы рангов од ной из выборок в общем вариационном РЯДУ и cpaBHeiaie суммы рангов с порогом. С целью повышения быстродействия устройства (без снижения эффективности обнаружения сигнала) в предложенном устройстве построение вариационного ряда выборки и подсчет cyMJvw рангов происходит в темпе поступления ин формации. При этом запоминается и ран жируется только обучающая выборка, а каждый последовательно поступающий элемент проверяемой выборки сравнивается с ранжированным рядом, и результаты сравнения используются для подсчета суммы рангов обучающей выборки в общем вариационном ряду. Это дости гается схемой построения матричного запоминающего устройства и сдвигателя, позволяющего параллельно (за 1 такт) сдвигать на 1 адрес часть массива элементов выборки. В матричном запоминающем устройст ве элементы обучающей выборки хранятся в порядке возрастания их величины причем меньшие элементы выборки располагаются в более младших адресах. При поступлении очередного элемента обучающей выборки он сравнивается по величине последовательно с уже запо ненными. Сравнение происходит до нахождения элемента, большего по величине, чем поступивший. После этого часть массива элементов обучающей вы борки, начиная с первого элемента, большего поступившего, сдвигается на 1 адрес в направлении увеличения адреса. Если же поступивший элемент больше всех уже запомненных он записывается за самым старшим элементом. Про цесс ранжировки продолжается до заполнения всех элементов памяти запоминающего устройства. После этого начинается цикл (режим) обнаружения. Элементы проверяемой выборки в темпе поступлени я инфо мации сравниваются последовательно с запомненными элементами обучающей вы борки, начиная со старшего. Сравнение осуществляется до первого элемен та обучающей выборки, меньшего посту пающего. При этом по каждоьгу сравнению, давшему результат больше, к числу, определяющему су.мму рангов, добавляется единица. При поступлении последнего элемента проверяемой выборки производится сравнение накопленной суммы рангов с пороговой вели чиной. При превышении порога выдается признак нет отсутствия сигнала, в противном случае признак

наличия сигнала, при этом признак да запоминается. Переход в режим обучения происходит при получении двух подряд признаков нет и наличия запомненного призн.са да или при поступлении внешнего сигнала на обучение.

Взаимодействие элементов устройства происходят следующим образом.

При включении устройства или подаче сигнала от внешнего устройства на клемму 16 устанавливается режим обучения. Синхронизация всех операций осуществляется по сигналам генератора синхроимпульсов, выдающего две серии

обучение cxeiviy И 9, и схережимом

му ИЛИ 5 перебрасывает триггер режима 4, устройство переходит в режим обнаружения.

5

В режиме обнаружения схема И 8 закрыта, сдвиги информации в запоминающем устройстве не производятся.

Числа, принимаемые с АЦП, сравниваются с записанными в запоминающем устройстве 2, начиная со старших адресов, в схеме 11 сравнения отсчетов.

Если принятое число меньше запомненного, схема 11 формирует сигнал меньше, который поступает на схе 12

5 сравнения с порогом, где по каждому импульсов СИ1 и СИ2, которые поступают на клеммы 20, 21 и далее на входы схемы 10 управления чтением и записью и вход cxeNbj 3 выделения первого импульса. Поступаю1цие от аналогоцифрового преобразователя на клемму 19 и на вход cxefvttj 10 управления чтением и записью элементы обучакадей выборки сравниваются последовательно, начиная с младшего адреса, с запом,ненными в запоминающем устройстве 2 числами. При нахождении числа большего, чем поступившее, схема 11 сравнения отсчетов, вьщает сигнал ше , который через схему И 8, открытую режимом обучение, поступает по шине CS сдвига информации в цепи сдвига информации. Информация в запоминающем устройстве 2, начиная с адреса, в котором находится первое число, большее поступившего, сдвигается на 1 адрес в сторону увеличения адреса. Определение части массива, подлех ащей сдвигу, производится с помощью сдвигателя 1, В исходном состоянии при отсутствии единиц во Bceji разрядах сдвигателя 1 открыты все цепи сдвига. По каждому синхроимпульсу СИ происходит сдвиг содержимого сдвигателя на 1 разряд и в освободившийся младший разряд заносится единица. Наличие едмницы в разряде сдвигателя 1 означает запрещение сдвига информации в группе элементов памяти, составляющих один адрес и подключенных к данному разряду сдвигателя, что достигается подачей занрещающего уровня в цепи сдвига данного адреса, В начале цикла Сравнений происходит вы.деление первого импульса, что обеспечивает отставание продвижения залрещающих уровней на 1 адрес. Первое поступившее с аналогб-цифрового преобразователя число сравнивается с Hi/левым значением первого адреса запоминающего устройства 2,,поэтому сигнал больше вырабатывается по первому импульсу, и поступившее число записывается в первый адрес. При заполнении всех элементов.памяти запоминающего устройства 2 схема 10 управления чтением и записью вЬадает импульс, который через открытую сигналу меньше добавляется едини ца к сумме рангов. По первому сигналу больше схема 10 управления чтением и записью возвращается в ис ходное состояние, т. е. в состояние подготовки чтения старшего адреса. Следующее поступившее число снова сравнивается, начиная со старшего ад реса. После обработки последнего чис ла схема 10 управлением чтением и за писью выдает в схему 12 сравнения с порогом импульс, с поступлением кото рого в схеме 12 происходит сравнение накопленной суммы рангов с порогом. Если сумма меньше порога, выдаетс сигнал да, что свидетельствует об Наличии сигнала. При превышении порога выдается сигнал нет, соответствующий отсутствию сигнала. Сигнал да через схему ИЛИ 5 подтверхсдае состояние триггера 4 в режиме обнару жения. После получения двух сигналов нет следуюву х за сигналом/ да схема 12 сравнения с порогом через схему ИЛИ б вдает сигнал, перебрасывающий триггер режима 4, устройство переходит в режим обучения. . Передний фронт сигнала обучение с триггера 4 по шине (f сброса информации подается на сбросовые входы всех элементов памяти запоминающего устройства 2, сбрасывая таким образом все разряды матрицы в ноль. Формула изобретения Устройство для определения напичия металла в валках реверсивного обжимно го или балочного стана, содержащее схему управления чтением и записью, схему сравнения отсчетов, схему сравн ния с порогом, запоминающее устройство, выполненное в виде матрица на N слов по М разрядов и шины сдвига и сброса информации, причем входы схемы управления чтением и записью соединены с выходами аналого-цифрового преобразователя, генератора синхроимпуль сов, заломинающего устройства и одним из выходов схемы сравнения отсчетов, а выходы - с одним из входов сравнения отсчетов, схемы сравнения с порогом и запоминающего устройства, входы схемы сравнения отсчетов соединены с выходом аналого-цифрового преобразователя, а один из выходов - с одним из входов схемы сравнения с порогом, входы запоминающего устройства соединены с иинами сдвига и сброса и выходами схемы управления чтением и записью, отличающееся тем, что, с целью повышения надежности в работе, в него дополнительно введены сдвигатель, схемы выделения первого импульса и управления pemHMah-m, состоящие из триггера, трех схем ИЛИ, двух схем И, причем входы выделения первого импульса соединены с выходом генератора синхроимпульсов и с шиной сдвига, а выход - со входом сдвигателя, другрй вход которого соединен с-шиной сдвига, выходы сдвигателя соединены со входами запоминающего устройства, один из выходов триггера соединен с одним из входов схемы управления чтением и записью, а другой с другим входом схемы управления чтением и записью, шиной сброса, входом схемл сравнения с порогом, входом первой схемы И и через вторую схему И - с шиной сдвига; второй вход первой схемы И соединен с выходом схемы управления чтением и записью, а второй вход второй схемы И - с выходом первой схемы ИЛИ, входы которой соединены с выходами схемы управления чтением и записью и схемы сравнения отсчетов соответственно, один из входов триггера соединен с выходом второй схемы ИЛИ, один из входов которой соединен с выходом схемы сравнения с порогом, а другой - с выходом первой схемы И, другой вход триггера соединен с выходом третьей схеьв-j ИЛИ, один из входов которой соединен с выходом схемы сравнения с порогом, а другой - с выходом внешнего устройства. Источники информации, принятые во внимание при экспертизе 1. Зарубежная радиоэлектроника, 1971, 4, с, 49-50 (прототип).

О К Внешнею ЬЬЬ

ycmpfOcmSs °

130 От f(Un

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения наличия металла | 1979 |

|

SU910249A2 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Многоканальный программируемый преобразователь код-фаза | 1990 |

|

SU1742998A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1991 |

|

SU1807516A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

Авторы

Даты

1980-04-25—Публикация

1977-02-01—Подача