Устройство предназначено для определения наличия или отсутствия металла в валках реверсивного обжимного или балочного стана, используется при управлении и контроле процессом прокатки на реверсивных станах.

По основному авт.св. № 728951 известно устройство для определения зраличия или отсутствия металла в валках реверсивного обжимного или балочного стана, используемое при управлении и контроле процессом прокатки на реверсивных станах. Это устройство содержит схему сравнения отсчетов, схему сравнения с порогом, запоминающее устрой ство, сдвигатель, схему вьщеления первого импульса, шины сдвига и сброса информации,схему управления режимами, состоящую из триггера режима, трех схем ИЛИ и двух схем И,причем входы схемы управления чтением и записью соединены с клеммами подачи сигнала от аналогово-цифрового преобразователя и от генератора синхроимпульсов, с выходом запоминающего устройства и выходом схемы сравнения отсчетов, а выходы соединены с входом схемы сравнения отсчетов, с входом схемы сравнения с порогом и входами запоминающего устройства;входы схемы сравнения отсчетов соединены с клеммой подачи сигналов от аналогово-цифрового преобразователя и ВЕЛХОдом схемы управления чтением и записью, а выходы соединены с входом схемы сравнения с порогом и выходом схемы управления чтением и записью,входы схемы сравнения с порогом соединены с

10 выходом схемы управления чтением и записью и выходом схемы сравнения отсчетрв, а выходы соединены с выходными клеммами устройства, входы запоминающего устройства соединены с

15 шинами сдвига и сброса информации и двумя выходами схемы управления чтением и записью, а выход соединен с входом схемы управления чтенйём и записью, входы схемы вьщеления пер20вого импу.пьса соединены с одной из клемм подачи сигналов от генератора синхроимпульсов и с шиной сдвига информации, а выход соединен с входом сдвигателя, второй вход которого

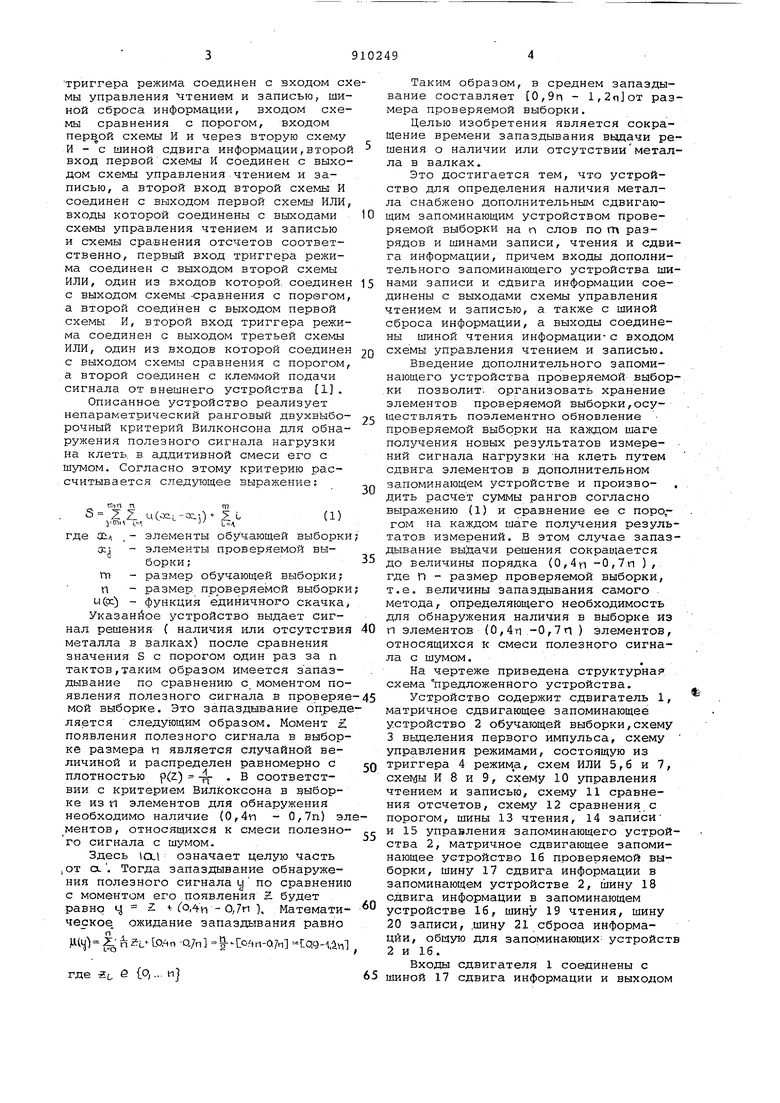

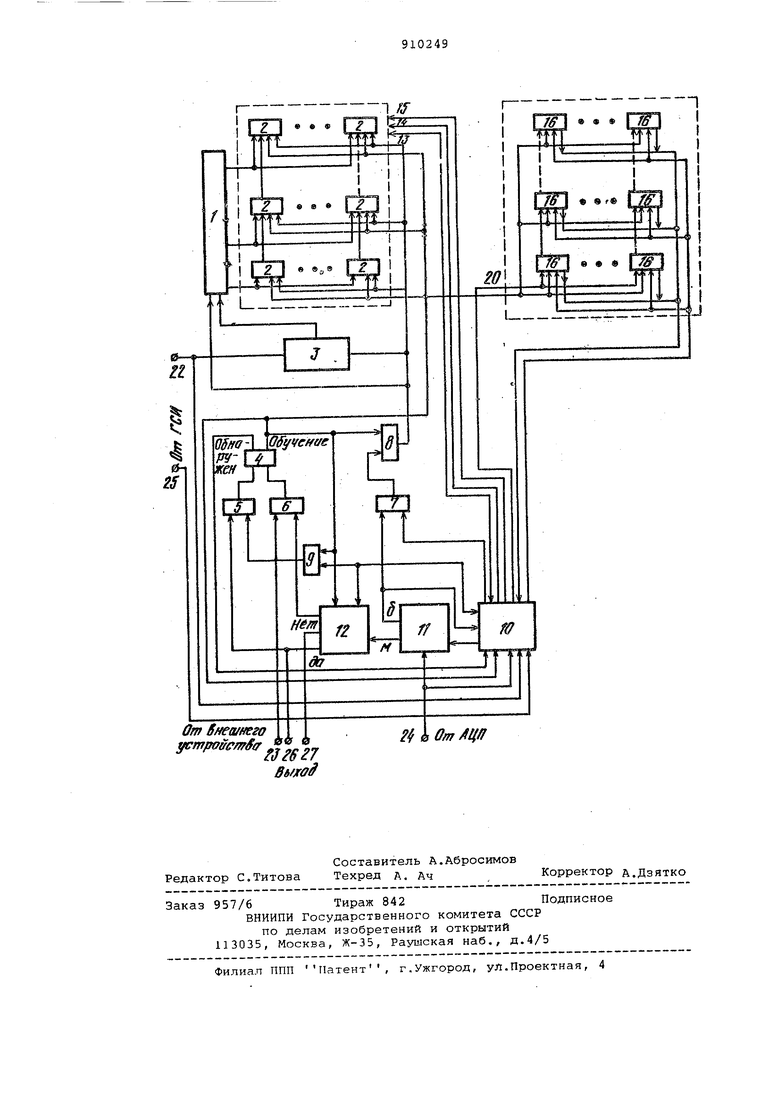

25 соединен с шиной сдвига информации, выходы сдвигателя соединены с входами элементов памяти запоминающего устройства, один из выходов триггера режима соединен с входом схемы управ30ления чтением и записью,второй выход триггера режима соединен с входом сх мы управления чтением и записью, шиной сброса информации, входом схемы сравнения с порогом, входом первой схемы И и через вторую схему И - с шиной сдвига информации,второ вход первой схемы И соединен с выходом схемы управления чтением и записью, а второй вход второй схемы И соединен с выходом первой схемы ИЛИ входы которой соединены с выходами схемы управления чтением и записью и схемы сравнения отсчетов соответственно, первый вход триггера режима соединен с выходом второй схемы ИЛИ, один из входов которой, соединен с выходом схемы сравнения с порэгом а второй соединен с выходом первой схемы И, второй вход триггера режима соединен с выходом третьей схемы ИЛИ, один из входов которой соединен с выходом схемы сравнения с порогом а второй соединен с клеммой подачи сигнала от внешнего устройства 1. Описанное устройство реализует непараметрический ранговый двухвЬ1борочный критерий Вилконсона для обнаружения полезного сигнала нагрузки на клеть, в аддитивной смеси его с шумом. Согласно этому критерию рассчитывается следующее выражение itn пШ S,(oc,-oc,5). где Oi-A , - элементы обучающей выборки ОС элементы проверяемой выборки ; m - размер обучающей выборки; п - размер, проверяемой выборки ц Со;) - функция единичного скачка Указанйое устройстве) выдает сигнал решения ( наличия или отсутствия металла в валках) после сравнения значения S с порогом один раз за п тактов,таким образом имеется запаздывание по сравнению с моментом появления полезного сигнала в проверяв мой выборке. Это запаздывание опред ляется следующим образом. Момент появления полезного сигнала в выборке размера ц является случайной величиной и распределен равномерно с плотностью p(z) -pj- .В соответствии с критерием ВилКоксона в дыборке из ti элементов для обнаружения необходимо наличие (0,4п - 0,7п) эл ментов, относящихся к смеси полезного сигнала с шумом. Здесь SOLI означает целую часть ,от о.. Тогда запаздывание обнаружения полезного сигнала у по сравнению с моментом его появления Z будет равно (олп - О,7п ). Матемафическое, ожидание запаздывания равно д(4) ; -а/п §- :оя-п-о.7п -tqg-i,anl где 2(, е (О,... Таким образом, в среднем запаздывание составляет 0,9п - 1, размера проверяемой выборки. Целью изобретения является сокращение времени запаздывания выдачи решения о наличии или отсутствии металла в валках. Это достигается тем, что устройство для определения наличия металла снабжено дополнительным сдвигающим запоминающим устройством проверяемой выборки на п слов по m разрядов и шинами записи, чтения и сдвига информации, причем входы дополнительного запоминающего устройства шинами записи и сдвига информа.ции соединены с выходами схемы управления чтением и записью, а также с шиной сброса информации, а выходы соединены шиной чтения информации-с входом схемы управления чтением и записью. Введение дополнительного запоминающего устройства проверяемой выборки позволит, организовать хранение элементов проверяемой выборки,осуществлять поэлементно обновление проверяемой выборки на каждом шаге получения новых результатов измере- . НИИ сигнала нагрузки на клеть путем сдвига элементов в дополнительном запоминающем устройстве и произво- . дить расчет суммы рангов согласно выражению (1) и сравнение ее с порогом на каждом шаге получения результатов измерений. В этом случае запаздывание выйачи решения сокращается до величины порядка (0,4п -0,7.п ) ,. где П - размер проверяемой выборки, т.е. величины запаздывания самого . метода, определяющего необходимость для обнаружения наличия в выборке из п элементов (0,4п.-0,7п ) элементов, относящихся к смеси полезного сигнала с шумом. На чертеже приведена структурная схема предложенного устройства. Устройство содержит сдвигатель 1, матричное сдвигающее запоминающее устройство 2 обучающей выборки,схему 3 выделения первого импульса, схему управления режимами, состоящую из триггера 4 режим а, схем ИЛИ 5,6 и 7, схег« ы И 8 и 9, схему 10 управления чтением и записью, схему 11 сравнения отсчетов, схему 12 сравнения с порогом, шины 13 чтения, 14 записи и 15 управления запоминающего устройства 2, матричное сдвигающее запоминающее устройство 16 проверяемой выборки, шину 17 сдвига информации в запоминающем устройстве 2, шину 18 сдвига информации в запоминающем устройстве 16, шину 19 чтения, шину 20 записи, .шину 21 сброса информации, общую для запоминающих: устройств 2 и 16. Входы сдвигателя 1 соединены с шиной 17 сдвига информации и выходом схемы 3 вьщеления первого импульса, выходы сдвигателя соединены с входам элементов памяти запоминающего устройства 2, входы каждого из которых соединены также с шинами 17 и 21 сдвига и сброса информации соответст венно и с шинами 13,14,15 чтения,за писи и управления. Входы схемы 3 выделения первого импульса соединены с входной клеммой 22 подачи сигнала от генератора син хроимпульсов и шиной 17 сдвига информации, а выход соединен с входом сд-вигателя . 1. Входы триггера 4 режима через схе мы ИЛИ 5 и б и схему И 9 зоединены с выходами схемы 10 управления чтением и записью и схемы 12 сравнения с порогом, а также с выходной клеммой 23 подачи сигнала от внешнего устройства. Выходы триггера 4 режима соединены с входами схемы 10 управления . чтением и записью и схемы 12 сравнения с порогом, с шиной 21 сброса информации, входом схемы И 9 и через схему И 8 - с шиной 17 сдвига информации .. . Входы схемы 10 управления чтением и записью соединены с выходами триггера 4 режима, входной клеммой 24 подачи сигнала от аналого-цифрового преобразователя, входными клеммами22 и 25 подачи сигналов от генератора синхроимпульсов, выходом схемы 11 сравнения отсчетов, шиной 13 чтения и шиной 19 чтения. Выходы схемы 10 управления чтением и записью соединены с шиной 14 записи, шиной 15 управления, шиной 20 записи, шиной.18 сдвига информации, входом схемы 11 сравнения,входом схемы 12 сравнения с порогом, входом схемы И 9 и через схему ИЛИ 7 и схему И 8 - с шиной 17 сдвига информации.. Входы схемы 11 сравнения отсчетов соединены с одним из выходов схемы 10 управления чтением и записью и входной клеммой 24, а выходы соединены с входами схемы 12 сравнения с порогом, с одним из входов схемы 10 управления чтением и записью и через схемы ИЛИ 7 и схему И S - с шиной 17 сдвига информации. Входы схемы 12 сравнения с порогом соединены с одним из выходов схе мы 10 управления чтением и записыд, выходом схемы 11 сравнения отсчетов и выходом триггера 4 режима, а выходы соединены с выходными клемманш 26 и 27 и входами схем ИЛИ 5 и б. Входы запоминающего устройства 16 проверяемой выборки соединены шиной 20 записи и шиной 18 сдвига информации с выходами схемы 10 управления чтением и записью и с шиной 21 сброса информации, а выходы шиной 19 чтения соединены с входом схемы 10 управления чтением и запчсью. Работа устройстйа для определения наличия металла в валках основана на реализации непараметрического двухвыборочного рангового критерия Вилконсона проверки гипотезыю сдвиге сигнала. Согласно этому критерию Необходимо запоминание обучающей и проверяемой выборок результатов измерений сигнала датчика нагрузки на клеть, построение вариационного ряда их, подсчет .суммы рангов одной из выборок в общем вариационном ряду в соответствии с выражением (1) и сравнением суммы рангов с порогом.Обучающая выборка обычно принадлежит- к чисто шумовой реализации сигнала. При превышении порога выдается решение Нет отсутствия полезного сигнала датчика нагрузки в смеси его с шумом, Б противном случае выдается решение Да наличия полезного сипнала датчика нагрузки. С целью повышения быстродействия устройства (без снижения эффективности обнаружения сигнала} в предложенном изобретении построение вариационного ряда выборки и подсчет суммы рангов происходит в темпе поступления информации. При этом запоминаются обучающая и проверяемая выборки,ранжируется только обучающая выборка. В режиме обучения,когда нет металла в валках, осуществляется запоминание элементов обучаемой выборки в матричном запоминающем устройстве обучающей выборки в ранжированном порядке. При. поступлении .очередного элемента обучающей выборки он сравнивается пО величине с уже запомненными . Сравнение происходит до нахождения элемента,большего по величине, чем поступивший. После , этого часть массива элементов обучающей выборки, начиная с первого элемента, сдвигается на 1 адрес в направлении увеличения адреса.Если поступивший элемент больше всех уже запомненных, он записывается за самым старшим элементом. Процесс ранжировки продолжается до заполнения всех элементов памяти запоминающего устройства обучающей выборки. Одновременно элементы обучающей выборки запоминаются и в запоминающем устройстве проверяемой выборки в порядке поступления,при этом предварительно вся информация сдвигается на 1 адрес в сторону увеличения адреса, и каждый вновь поступающий элемент запоминается по первому адресу. После этого начинается цикл (режим) обнаружения. Каждый вновь поступающий элемент проверяемой выборки запоминается в запоминающем устройстве проверяемой выборки в порядке поступления, как описано выше. Все элементы, запомненные в запо минающем устройстве проверяемой выборки, сравниваются последовательно с эапомненньл ш элементами обучающей выборки, начиная со старшего. Сравнение осуществляетсядо первого элемента обучающей выборки,меньшего эле мента из проверяемой выборки. При этом по каждому сравнению, давшему результат Больше к числ-у опреде ляющему сумму рангов, добавляется ед ница. Затем производится сравнение накопленной суммы рангов с пороговой величиной. При превышении порога выдается признак Нет отсутствия сигнала, в противном случав выдается признак Да наличия сигнала, «при запоминается.Пеэтом признак реход в режим обучения происходит при получении подряд и признаков Мет и наличия запомненного приз нака Да или при поступлении внеи него сигнала на обучение. Взаимодействие элементов устройства происходит следующим образом. При включении, устройства или подаче сигнала от внешнего устройства на клемму 23 устанавливается режим обучения. Синхронизация всех операций осуществляется по сигналам генератог: а синхроимпульсов .выдающего две серии иг/пульсов СИ1 и СИ2,которые поступают на клеммы 22 и 25,и д лее, - на входы 10 управления чтением и зггписью и вход схемы 3 вы1;,елени5 первого импульса.Поступаю щие от аналогово-цифрового преобразователя на 24 и на вход схе мы 10 управления чтением и записью элементы обучающей выборки запомина ются последовательно в запоминающем устройстве 16 проверяемой выборки, а также сравниваются последовательн начиная с младаюго адреса, с запомненны.1и в запоминающем устррйстве 2 обучающей выборки числами. При на хождении числа большего, чем поступившее, схема 11 сравнения отсчетов выдает сигнал Больше, который Через схему И 8, открытую режимом Обучение, поступает по шине 17 сдвига информации в цепи сдвига информации. Информация в запоминающем устройстве 2, начиная с адреса, в котором находилось первое число,большее поступившего, сдвигается на 1 адрес в сторону увеличения адреса. Определение части массива,подлежаще сдвигу, производится с помощью сдви гателя 1. В исходном состоянии при отсутст вии единиц во всех разрядах сдвигателя 1 открыты все цепи сдвига. По каждому синхроимпульсу СИ1 происходит сдвиг содержимого сдвигателя на 1 разряд, и в освободившийся младший разряд заносится единица. Наличие единицы в разряде сдвигателя 1 означает запрещение сдвига информации в группе элементов памяти обучаемой выборки, составляющих один адрес и подключенных к данному разряду сдвигателя, что достигается Подачей запрещающего уровня в цепи сдвига данного адреса. В начале цикла сравнений происхо- . дит выделение первого импульса, что обеспечивает отставание продвижения запрещающих уровней на 1 адрес.Первое поступившее с аналого-цифрового преобразователя число сравнивается с нулевым значением первого адреса запоминающего устройства 2, поэтому сигнал больше вырабатывается по первому импульсу, и поступившее число записывается в первый адрес. По синхроимпульсу СИ2 происходит также сдвиг информации в запоминающем устройстве 16 проверяемой выборки на 1 адрес в сторону старших адресов и запись поступившего элемента обучающей выборки в первый адрес. При запоминании всех элементов памяти загпоминающего устройства 2 обучающей выборки схема 10 управления чтением и записью выдает импульс, который ч ере э открытую режимом обучение схему И 9 и схему ИЛИ 5 перебрасывает триггер 4 режима, устройство переходит в режим обнаружения. В режиме обнаружения схема И 8 закрыта, сдвиги информации в запоминающем устройстве 2 обучающей выборки не производятся. Числа, принимаемые с АЦП по каждому синхроимпульсу СИ2,запоминаются в запоминающем устройстве 16 проверяемой выборки, при этом предварительно вся информация сдвигается на 1 адрес в сторону старших адресов и каждое вновь поступившее число заносится в первый адрес.Это осущесЛгвляется с помощью схемы управления чтением и записью . Затем по каждому синхроимпульсу СИ все числа, записанные в запоминающем устройртве 16 проверяемой выборки, сравниваются с числами,записанными в запоминающем устройстве 2 обучающей выборки,начиная со старшего адреса последнего.Сравнение происходит в схеме И сравнения отсчетов . 5сли число проверяемой выборки меньше числа обучаемой выборки, схема 11 формирует сигнал Меньше,который поступает на схему 12 сравнения с порогом,где по каждому сигналу Меньше добавляется единица к сумме рангов. По первому сигналу Больше схема 10 управления чтением и записью возвращается в исходное состояние, т.е. подготовки чтения старшего адреса запоминающего устройства 2. Следующее число проверяемой

выборки снова сравнивается с числами обучающей выборки, начиная со старшего адреса. После обработки последнего числа схема 10 управления и записью выдает в схему 12 сравнения с порогом импульс, с поступлением которого в схеме 12 происходит сравнение накопленной суммы рангов с порогом.

Если сумма меньше порога,выдается сигнал Да, что свидетельствует о наличии полезного сигнала. При превышении порога выдается сигнал Нет ,соотетствую1ций отсутствию полезного сигнала. Сигнал Дачерез схему ИЛИ 5 подтверждает состояние триггера 4 в режиме обнаружения После получения и сигналов Нет, следующих за сигналом Да, схема 12 сравнения с порогом через схему ИЛИ б выдает сигнал, перебрасйвающий триггер 4 режима, устройство переходит в режим обучения. Передний фронт сигнала Обучение с триггера 4 по шине 21 сброса информации подается на сбросовые входы всех элементов памяти запоминающего устройства 2 и запоминающего устройствам 16 сбрасывая таким образом все разряды матриц в ноль.

В связи с введением дополнительного запоминающего устройства проверяемой выборки описываемое устройство осуществляет обнаружение полезного сигнала нагрузки на клеть в смеси его с шумом на каждом шаге получения результатов измерения сигнала, тем самым сокращая время запаздывания выдачи решения о наличии или отсутствии металла в валках с величины порядйа (0, -1,2 ) до величины (0,4и -0,7п)1 , где и - размер проверяемой выборки.

Формула изобретения

Устройство для определения наличи металла по авт.св.№728951,о т л и ч ю щ е е с я тем, что, с целью сокращения времени запаздывания выдачи: решения о«наличии или отсутствии металла в валках, оно снабжено дополнительным сдвигающим запоминающим устройством и шинами записи, чтения исдвига информации, причем входы дополнительного запоминающего устройства шинами записи и сдвига информации соединены с выходами схемы управления чтением и записью, а также с шиной сброса информации, а выходы соединены шиной чтения информации с входом схемы управления чтением и записью.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 728951, кл. В 21 В 37/00, 1978 (прототип).

« Г|

TTt

LI

/.

Izrnrzzrrrr:

n

M /cf

ra

JJ

ы

I №

ЕЙ

ПП

в «

ff

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения наличия металла в валках реверсивного обжимного или балочного стана | 1977 |

|

SU728951A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство генерации тестовых последовательностей для контроля оперативных накопителей | 1989 |

|

SU1636858A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Микропрограммный процессор | 1982 |

|

SU1062712A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Микропрограммный процессор | 1985 |

|

SU1275457A1 |

Ofyftf/vs

QSffdptfirfiy

m m

rz

От SfK a/него

00 в yemfmyc/ffSff

(

06/jrff

ff

/

2 k 0m /I tiff

Авторы

Даты

1982-03-07—Публикация

1979-07-11—Подача