13

Изобретение относится к вычислительной технике, может быть использовано при построении средств, микропрограммного управления в системах обработки данных и регулирования и является усовершенствованием известного устройства по авт.св. № 1124275

Цель изобретения - повышение производительности за счет высвобождения его интерфейсной магистрали при выполнении микропрограмм и при работе микропроцессора с оперативной памятью и обеспечение возможности использования освободившегося адресного поля другими активными устройствами, подключенными к этой магистрали .

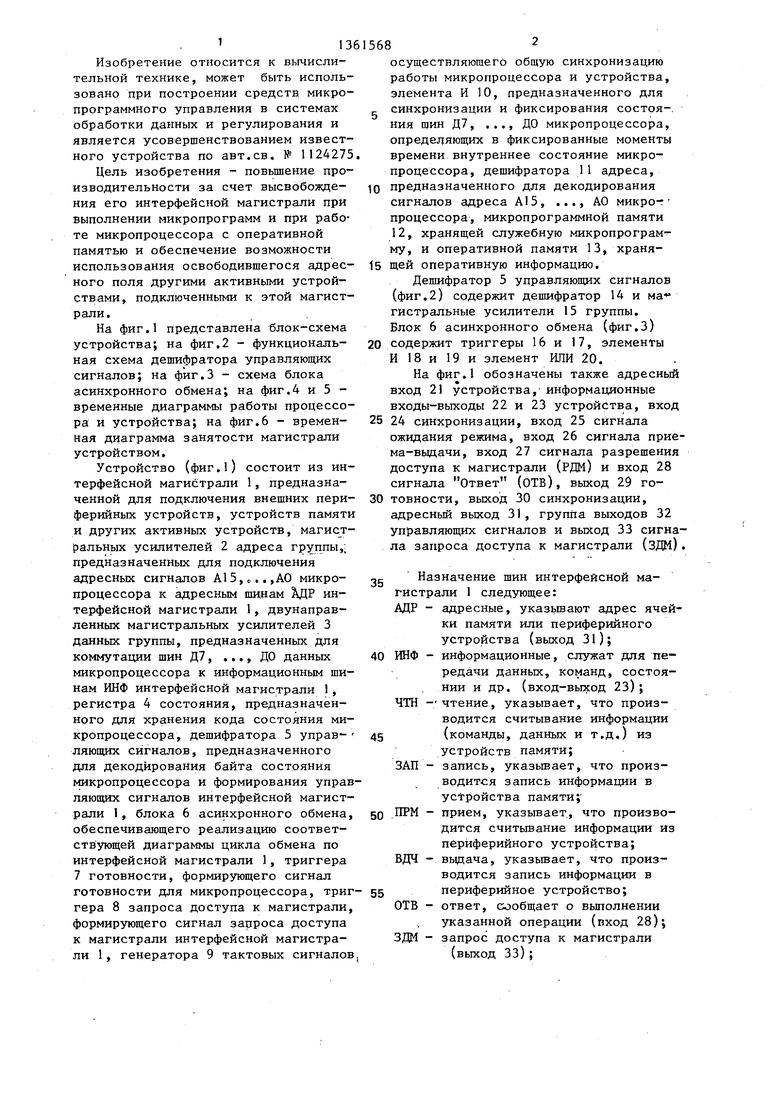

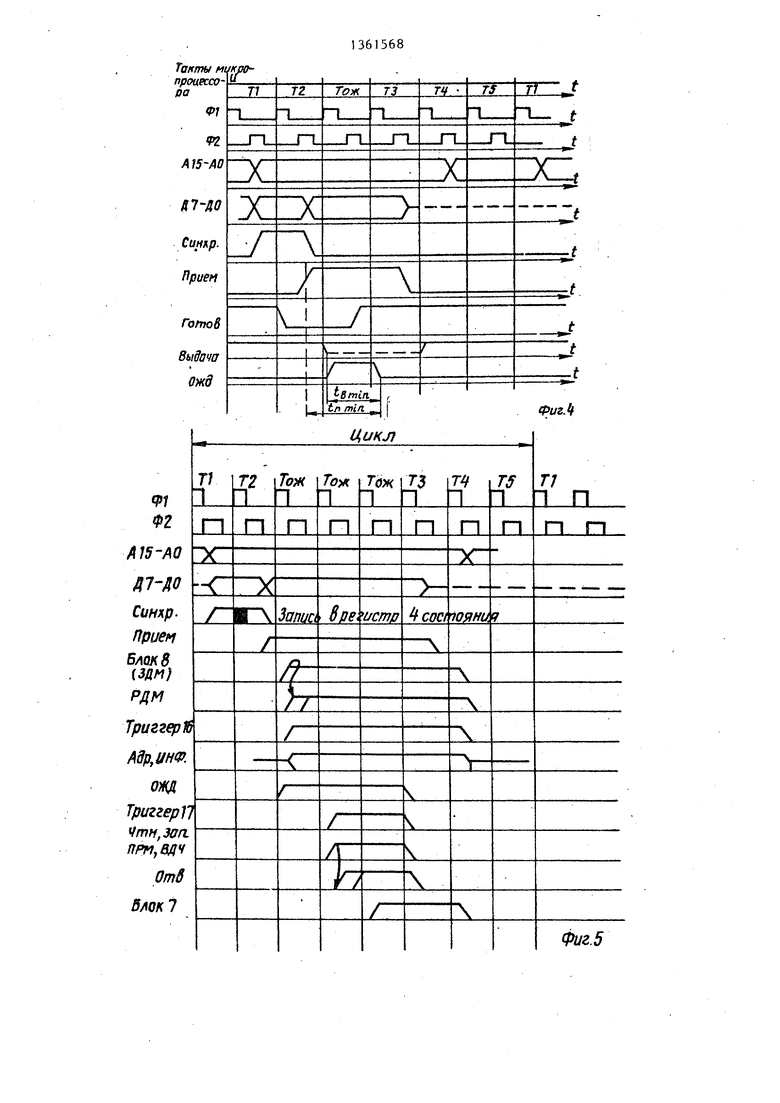

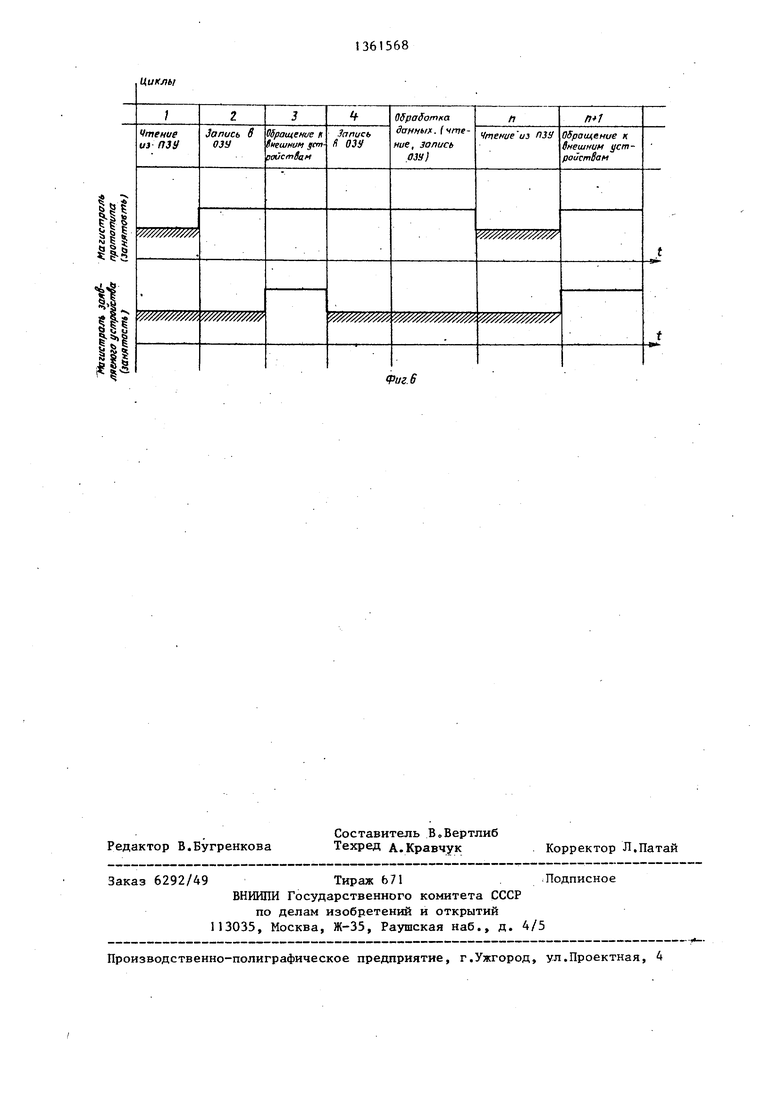

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональная схема депгафратора управляющих сигналов; на фиг.З - схема блока асинхронного обмена; на фиг.4 и 5 - временные диаграммы работы процессора и устройства; на фиг.6 - временная диаграмма занятости магистрали устройством.

Устройство (фиг.1) состоит из интерфейсной магистрали 1, предназначенной для подключения внешних периферийных устройств, устройств памяти и других активных устройств, магист- {)альных усилителей 2 адреса группы,; предназначенных для подключения адресных сигналов А15,„..,АО микропроцессора к адресным шинам 2ЩР интерфейсной магистрали 1, двунаправленных магистральных усилителей 3 данных группы, предназначенных для коммутации шин Д7, ..., ДО данных микропроцессора к информационным шинам ИНФ интерфейсной магистрали 1, регистра 4 состояния, предназначенного для хранения кода состояния микропроцессора, дешифратора 5 управ- ляющих сигналов, предназначенного для декодирования байта состояния микропроцессора и формирования управляющих сигналов интерфейсной магистрали 1, блока 6 асинхронного обмена, обеспечивающего реализацию соответствующей диаграммы цикла обмена по интерфейсной магистрали 1, триггера 7 готовности, формирующего сигнал готовности для микропроцессора, триггера 8 запроса доступа к магистрали, формирующего сигнал зацроса доступа к магистрали интерфейсной магистрали 1, генератора 9 тактовых сигналов

682

осуществляющего общую синхронизацию работы микропроцессора и устройства, элемента И 10, предназначенного для

(- синхронизации и фиксирования состоя-, ния щин Д7, ..., ДО микропроцессора, определяющих в фиксированные моменты времени внутреннее состояние микропроцессора, дешифратора 11 адреса,

0 предназначенного для декодирования сигналов адреса А 5, ..., АО микро-г процессора, микропрограммной памяти 12, хранящей служебную микропрограмму, и оперативной памяти 13, храня5 щей оперативную информацию.

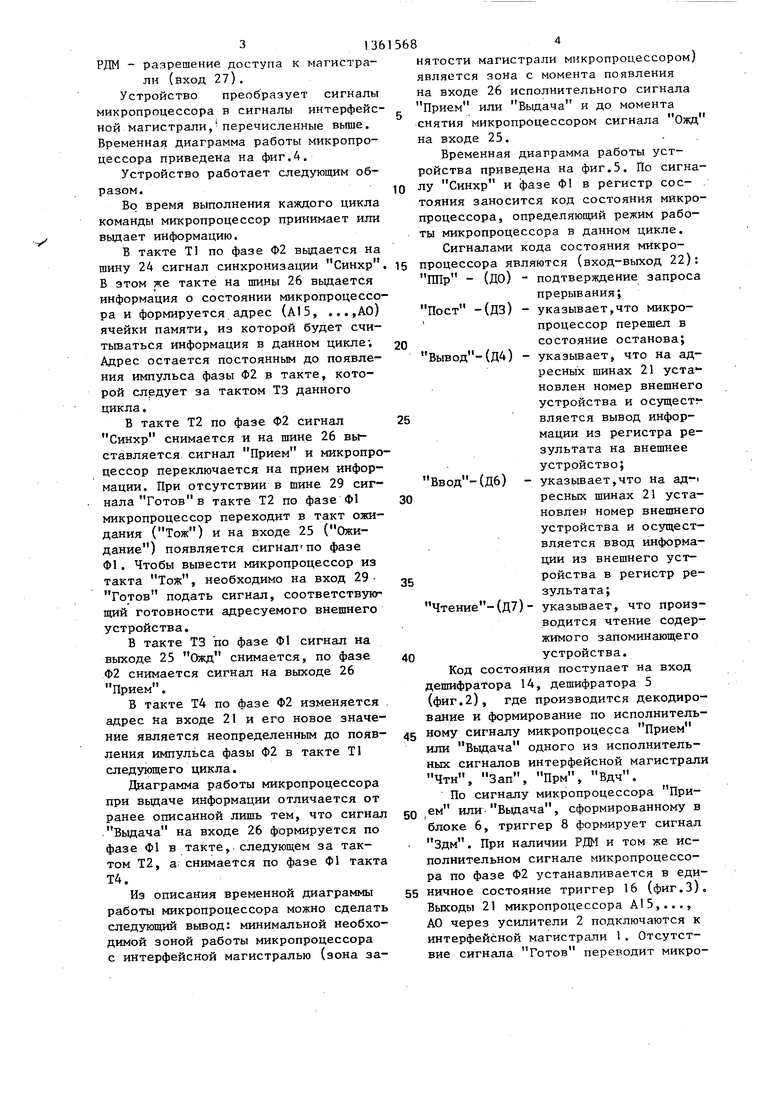

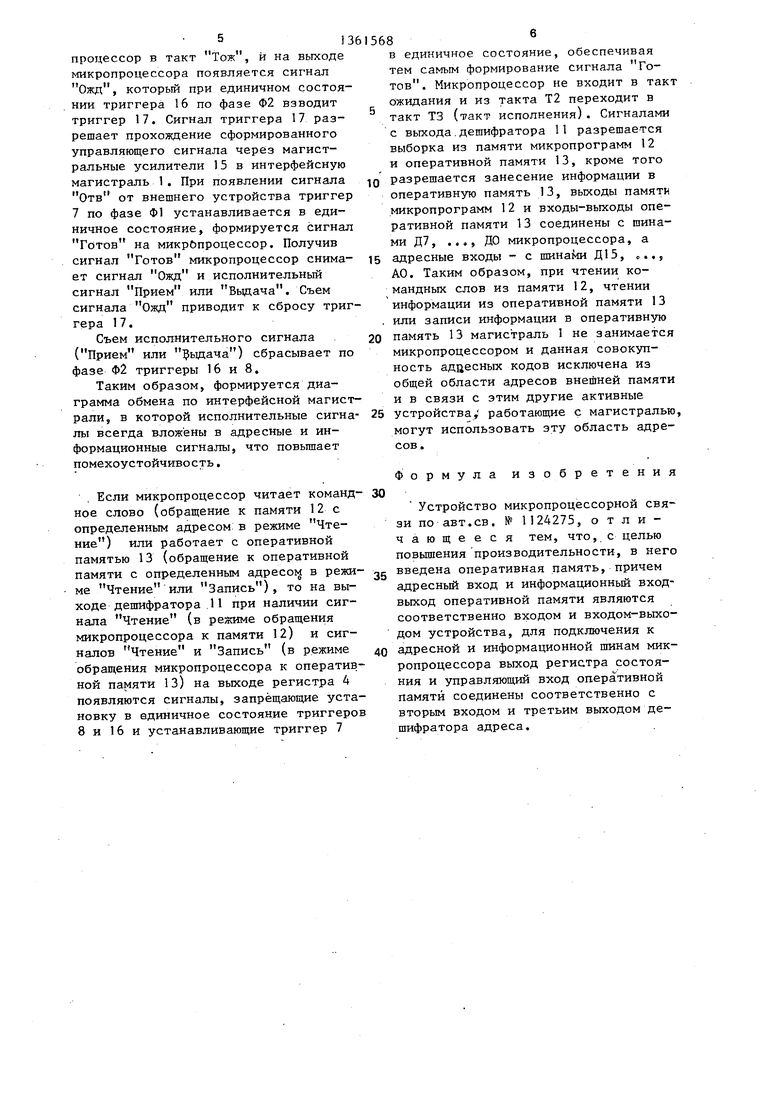

Дешифратор 5 управляющих сигналов (фиг.2) содержит дешифратор 14 и ма гистральные усилители 13 группы. Блок 6 асинхронного обмена (фиг.З)

0 содержит триггеры 16 и 17, элементы И 18 и 19 и элемент ИЛИ 20.

На фиг.1 обозначены также адресный вход 21 устройства, информационные входы-выходы 22 и 23 устройства, вход

5 24 синхронизации, вход 25 сигнала

ожидания режима, вход 26 сигнала приема-выдачи, вход 27 сигнала разрешения доступа к магистрали (РДМ) и вход 28 сигнала Ответ (ОТВ), выход 29 го0 товности, выход 30 синхронизации, адресный вьпсод 31 , группа выходов 32 управляющих сигналов и выход 33 сигнала запроса доступа к магистрали (ЗДМ).

25 Назначение щин интерфейсной магистрали 1 следующее: АДР - адресные, указьшают адрес ячейки памяти или периферийного устройства (вькод 31);

40 ИНФ - информационные, служат для передачи данных, команд, состоя- . НИИ и др. (вход-выход 23); ЧТН -чтение, указывает, что производится считывание информации 5 (команды, данных и т.д.) из

устройств памяти;

ЗАП - запись, указьшает, что производится запись информации в устройства памяти;0 .ПРМ - прием, указьшает., что производится считьгоание информации из периферийного устройства; ВДЧ - выдача, указьгоает, что производится запись информации в 5 периферийное устройство;

ОТВ - ответ, сообщает о выполнении указанной операции (вход 28); ЗДМ - запрос доступа к магистрали (выход 33);

РДМ - разрешение доступа к магистрали (вход 27). Устройство преобразует сигналы

микропроцессора в сигналы интерфейсi5

НОИ магистрали, перечисленные вьпие.

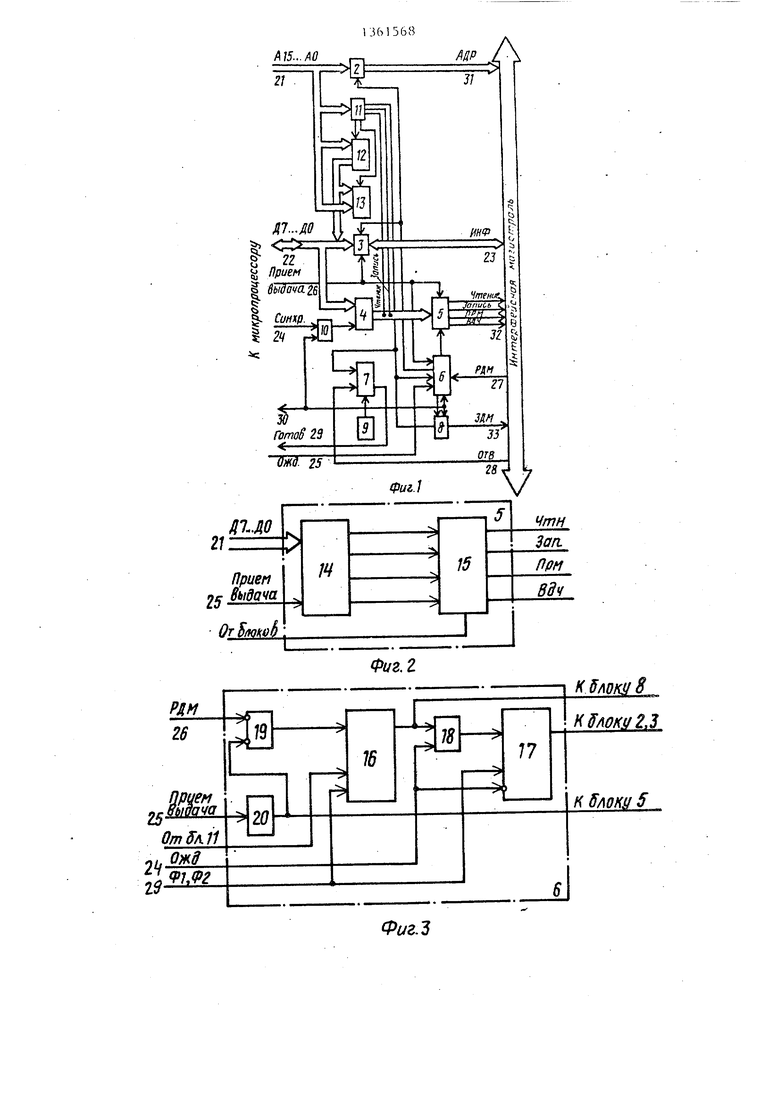

Временная диаграмма работы микропроцессора приведена на фиг.4.

Устройство работает следующим образом.10

Во время выполнения каждого цикла команды микропроцессор принимает или вьщает информацию.

В такте Т1 по фазе Ф2 выдается на шину 24 сигнал синхронизации Синхр. 15 В этом же такте на шины 26 вьщается информация о состоянии микропроцессора и формируется адрес (А15, ...,АО) ячейки памяти, из которой будет счи- тьгоаться информация в данном цикле; 20 Адрес остается постоянным до появления импульса фазы Ф2 в такте, которой слэдует за тактом ТЗ данного цикла.

В такте Т2 по фазе Ф2 сигнал 25 Синхр снимается и на шине 26 выставляется сигнал Прием и микропроцессор переключается на прием информации. При отсутствии в шине 29 сигнала Готов в такте Т2 по фазе Ф1 30 микропроцессор переходит в такт ожидания (Тож) и на входе 25 (Ожидание) появляется сигнал по фазе Ф1. Чтобы вывести микропроцессор из такта Тож, необходимо на вход 29- Б Готов подать сигнал, соответствунг щий готовности адресуемого внешнего устройства.

В такте ТЗ по фазе Ф1 сигнал на выходе 25 Ожд снимается, по фазе 40 Ф2 снимается сигнал на выходе 26 Прием.

В такте 14 по фазе Ф2 изменяется . адрес Иа входе 21 и его новое значение является неопределенным до появ- 45 ления импульса фазы Ф2 в такте Т1 следующего цикла.

Диаграмма работы микропроцессора при выдаче информации отличается от ранее описанной лишь тем, что сигнал 50 Вьщача на входе 26 формируется по фазе Ф1 в такте,следующем за тактом Т2, а снимается по фазе Ф1 такта Т4.

Из описания временной диаграммы 55 работы микропроцессора можно сделать следующий вьшод: минимальной необходимой зоной работы микропроцессора с интерфейсной магистралью (зона занятости магистрали микропроцессором) является зона с момента появления на входе 26 исполнительного сигнала Прием или Выдача и до момента снятия микропроцессором сигнала Ожд на входе 25.. .

Временная диаграмма работы устройства приведена на фиг.5. По сигналу Синхр и фазе Ф1 в регистр сое- тояния заносится код состояния микропроцессора, определяющий режим работы микропроцессора в данном цикле. Сигналами кода состояния микропроцессора являются (вход-выход 22): ППр - (до) - подтверждение запроса

прерывания;

Пост -(ДЗ) - указывает,что микро- процессор перешел в

состояние останова;

Вывод -(Д4) - указывает, что на адресных шинах 21 установлен номер внешнего устройства и осущест вляется вывод информации из регистра результата на внешнее устройство;

(Дб) - указьшает,что на ад-i ресных шинах 21 установлен номер внешнего устройства и осуществляется ввод информации из внешнего устройства в регистр результата;

Чтение -(Д7)- указьшает, что производится чтение содержимого запоминающего устройства.

Код состояния поступает на вход дешифратора 14, дешифратора 5 (фиг.2), где производится декодирование и формирование по исполнительному сигналу микропроцесса Прием или Вьщача одного из исполнительных сигналов интерфейсной магистрали Чтн, Зап. Прм, Вдч.

По сигналу микропроцессора При- ем или Вьщача, сформированному в блоке 6, триггер 8 формирует сигнал Здм. При наличии РДМ и том же исполнительном сигнале микропроцессора по фазе Ф2 устанавливается в единичное состояние триггер 16 (фиг.З), Выходы 21 микропроцессора А15,..., АО через усилители 2 подключаются к интерфейсной магистрали 1. Отсутствие сигнала Готов переводит микропроцессор в такт Тож, и на выходе микропроцессора появляется сигнал Ожд, которьй при единичном состоя- . НИИ триггера 16 по фазе Ф2 взводит триггер 17. Сигнал триггера 17 разрешает прохождение сформированного управляющего сигнала чере:з магистральные усилители 15 в интерфейсную магистраль 1. При появлении сигнала Отв от внешнего устройства триггер 7 по фазе Ф1 устанавливается в единичное состояние, формируется сигнал Готов на микропроцессор. Получив сигнал Готов микропроцессор снимает сигнал Ожд и исполнительный сигнал Прием или Выдача. Съем сигнала Ожд приводит к сбросу триггера 17.

Съем исполнительного сигнала (Прием или : ыдача) сбрасывает по фазе Ф2 триггеры 16 и 8.

Таким образом, формируется диаграмма обмена по интерфейсной магистрали, в которой исполнительные сигналы всегда вложены в адресные и информационные сигналы, что повьшает помехоустойчивость.

35

Если микропроцессор читает команд- 30 нее слово (обращение к памяти 12 с определенным адресом в режиме Чтение) или работает с оперативной памятью 13 (обращение к оперативной памяти с определенным адресом в режи- ме Чтение или Запись), то на выходе дешифратора . 1 1 при наличии сигнала Чтение (в режиме обращения микропроцессора к памяти 12) и сигналов Чтение и Запись (в режиме обращения микропроцессора к оператив.- ной памяти 13) на выходе регистра 4 появляются сигналы, запрещающие установку в единичное состояние триггеров 8 и 16 и устанавливающие триггер 7

40

6

в единичное состояние, обеспечивая тем самым формирование сигнала Готов. Микропроцессор не входит в такт ожидания и из такта Т2 переходит в такт ТЗ (такт исполнения). Сигналами с выхода.дешифратора 11 разрешается выборка из памяти микропрограмм 12 и оперативной памяти 13, кроме того

разрешается занесение информации в оперативную память 13, выходы памяти .микропрограмм 12 и входы-выходы оперативной памяти 13 соединены с шинами Д7, ..., ДО микропроцессора, а

адресные входы - с шинайи Д15, .., АО. Таким образом, при чтении командных слов из памяти 12, чтении информации из оперативной памяти 13 или записи информации в оперативную

память 13 магистраль 1 не занимается микропроцессором и данная совокупность адресных кодов исключена из общей области адресов внешней памяти и в связи с этим другие активные

устройства, работающие с магистралью, могут использовать эту область адресов.

Формула изобретения

Устройство микропроцессорной связи по авт.св. № 1124275, отличающееся тем, что, с целью повышения производительности, в него введена оперативная память, причем адресный вход и информационный вход- выход оперативной памяти являются соответственно входом и входом-выходом устройства, для подключения к адресной и информационной пганам микропроцессора выход регистра состояния и управляющий вход оперативной памяти соединены соответственно с вторым входом и третьим выходом дешифратора адреса.

f 15... АО

От 25

/1ДР

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

| Устройство для сопряжения микропроцессора с периферийными устройствами | 1987 |

|

SU1434440A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для сопряжения с микропроцессором | 1983 |

|

SU1109730A1 |

| Система обмена данными в вычислительной сети | 1991 |

|

SU1807493A1 |

Изобретение относится к вычислительной технике, может быть использовано при построении средств микро- nporpaMfffloro управления в системах обработки данных и регулирования.. Целью изобретения является повышение производительности. Для достижения этой цели в устройство введена оперативная память, обращаясь к которой при вьтолнении микропрограмм, центральный процессор не занимает интерфейсную магистраль. Устройство позволяет увеличить суммарную область памяти, используемую микропроцессором и другими активными устройствами системы, и увеличить зффективность системы в связи с увеличением времени возможного доступа активных устройств к интерфейсной магистрали. 6 ил. со О5 ел о 00 ГЧ)

Фиг. 2

Фиг.

Ф1

Ф2 AJ5-AO

Д7-ЛО Синхр. Прием Блоке

(ЭДМ)

рдм

Тригг Ю

Мр,инФ.

ОЖД

ТриггерП чтн,зап

Отв блок

Редактор В.Бугренкова

Составитель ВоВертлиб Техред А.Кравчук

Заказ 6292/49Тираж 671 Подписное

ВНИИПИ Государствениого комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

Корректор Л.Патай

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-12-23—Публикация

1986-05-28—Подача