Ч

«и

V)

::г о

5(

§- I

Ч

щя

4

со

Изобретение относится к цифровой .вычислительной технике и может быть использовано в микропроцессорных системах управления и обработки данных.

Цель.изобретения - повышение быстродействия устройства.

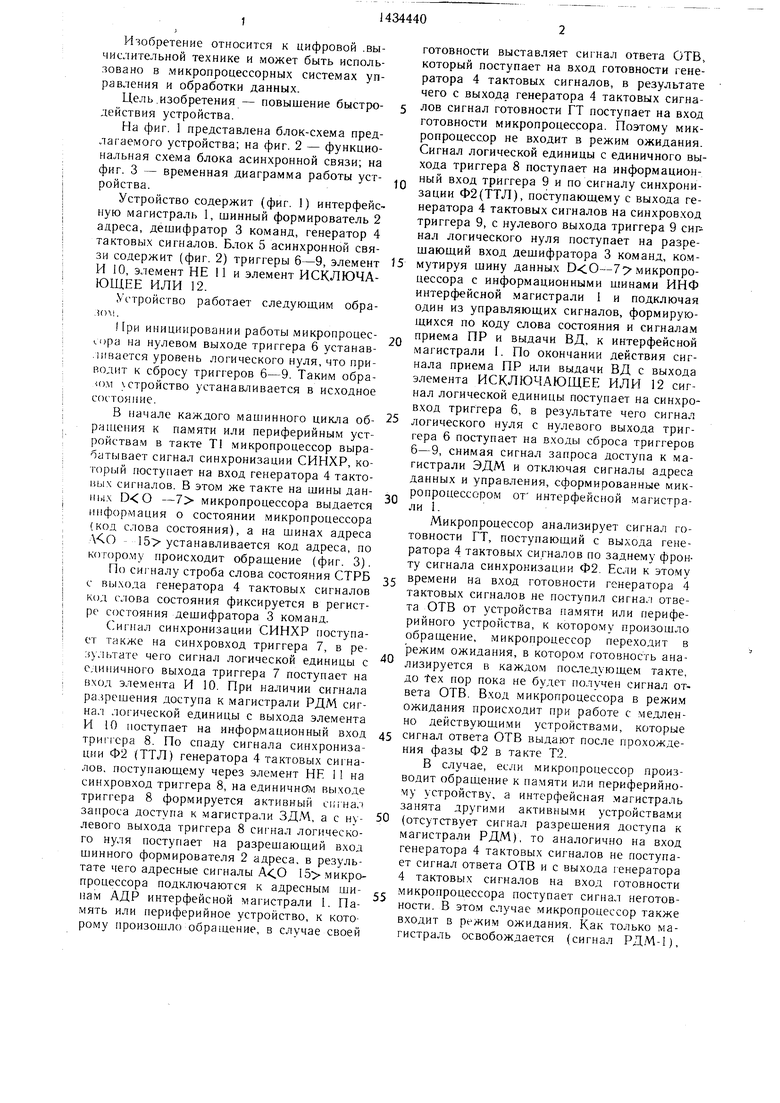

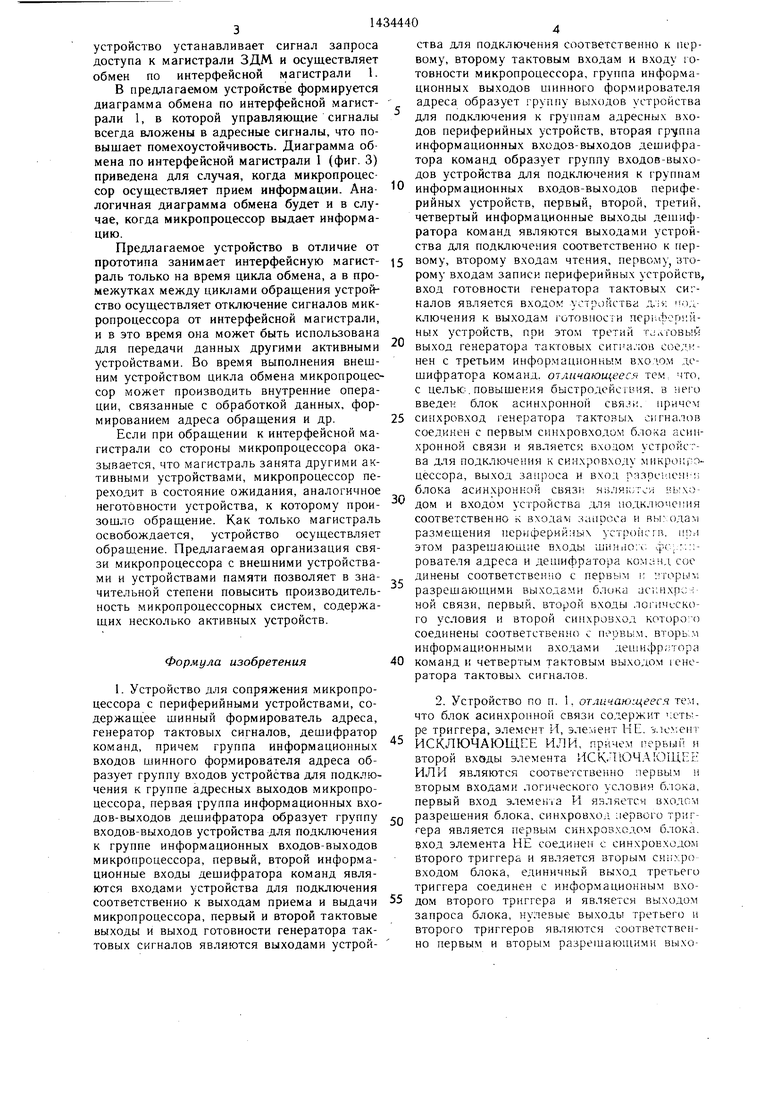

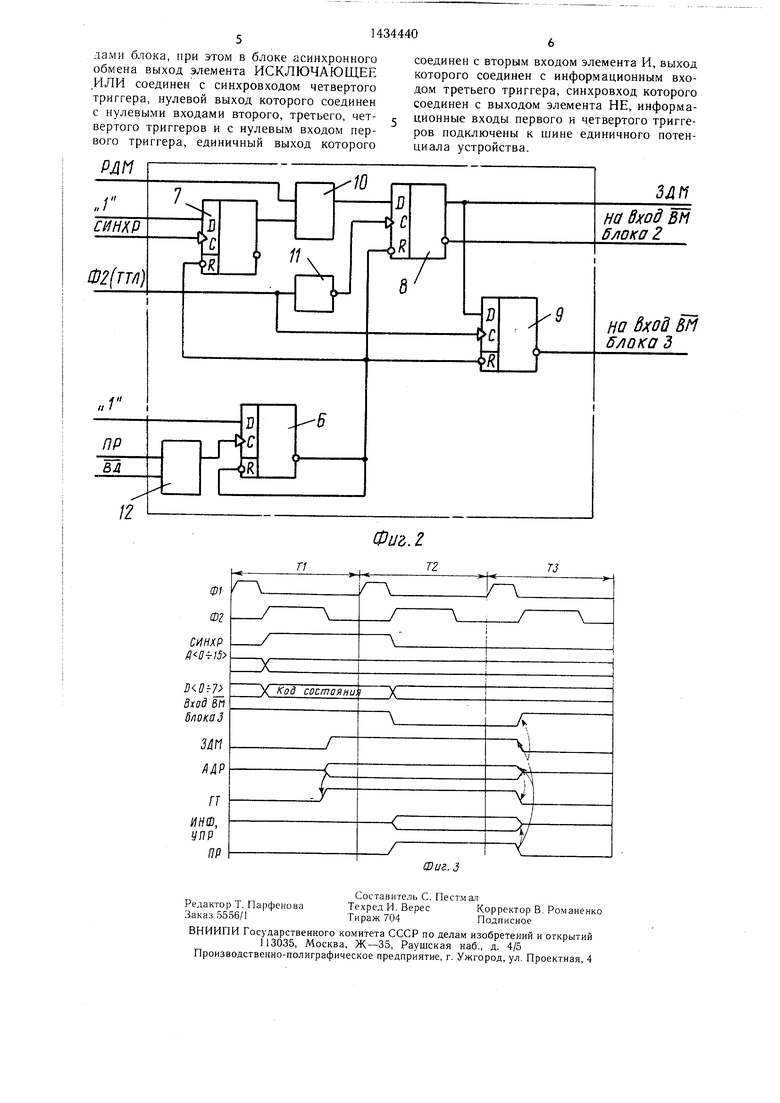

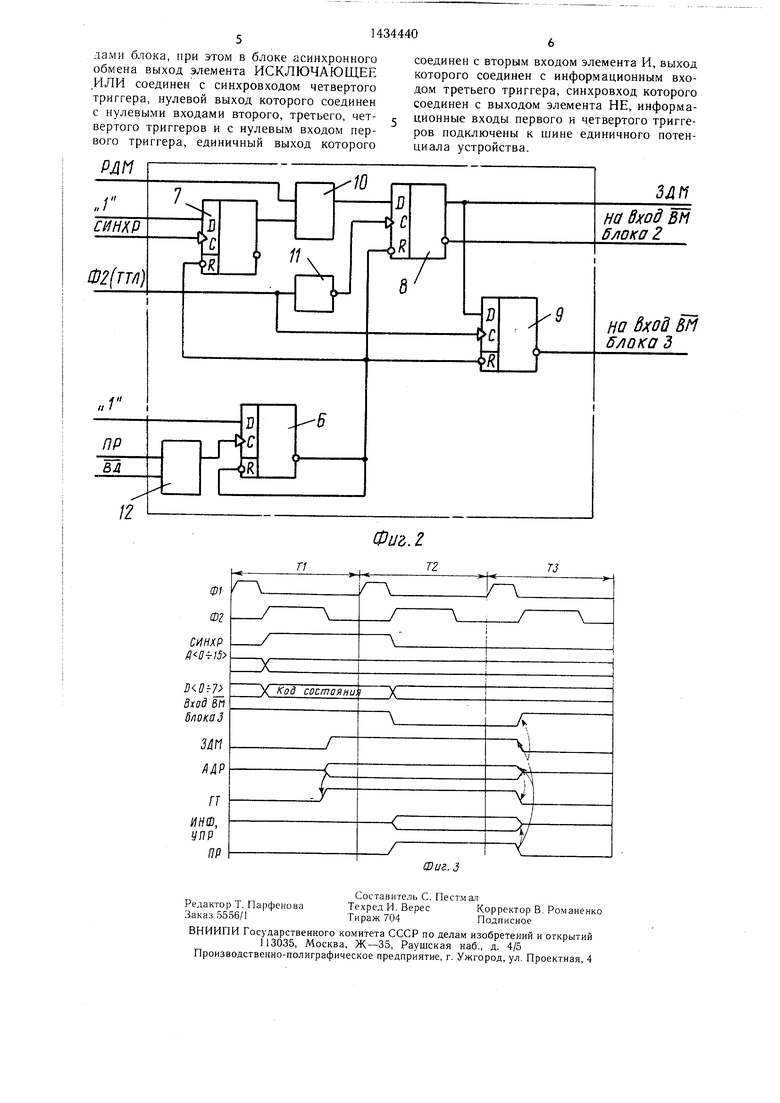

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - функциональная схема блока асинхронной связи; на фиг. 3 - временная диаграмма работы устройства.

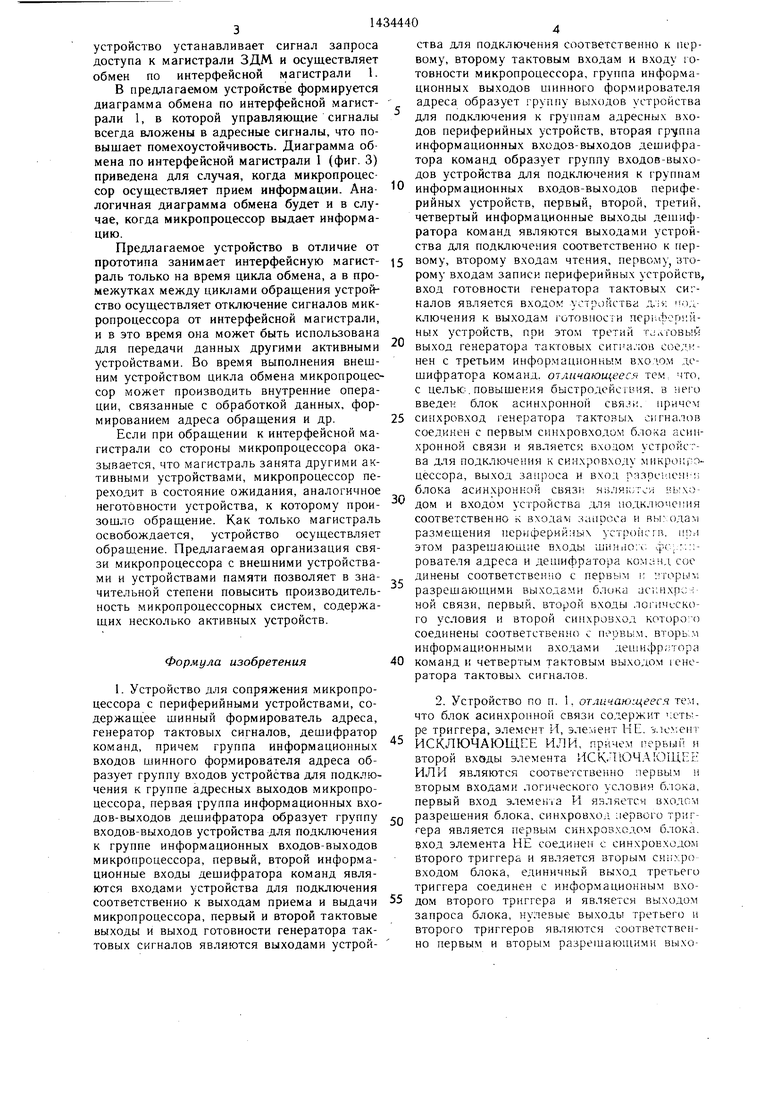

Устройство содержит (фиг. 1) интерфейсную магистраль 1, шинный формирователь 2 адреса, дешифратор 3 команд, генератор 4 тактовы.х сигналов. Блок 5 асинхронной связи содержит (фиг. 2) триггеры 6-9, элемент И 10, элемент НЕ 11 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12.

Устройство работает следующим образом.

.При инициировании работы микропроцес- о)ра на нулевом выходе триггера б устанав- .швается уровень логического нуля, что приводит к сбросу триггеров 6-9. Таким обра- u).vi vcтpoйcтвo устанаштивается в исходное состоя)ие.

В начале каждого машинного цикла обращения к памяти или периферийным устройствам в такте TI микропроцессор выра- ог1ТЕ)1вает сигнал синхронизации СИНХР, который поступает на вход генератора 4 тактовых сигналов. В этом же такте на шины дан- Hhi.x D О -7 микропроцессора выдается информация о состоянии микропроцессора (код слова состояния), а на шинах адреса Д-СО 15 устанавливается код адреса, по KOTopo.viy происходит обрашение (фиг. 3).

По си|-налу строба слова состояния СТРБ с вы.хода генератора 4 тактовых сигналов код слова состояния фиксируется в регистре состояния дешифратора 3 команд.

( игнал синхронизации СИНХР юступа- ет также на синхровход триггера 7, в результате чего сигнал логической единицы с единичного выхода триггера 7 поступает на вход элемента И 10. При наличии сигнала разрешения доступа к магистрали РДМ сигнал логической единицы с выхода элемента И 10 поступает на информационный вход TpHiTcpa 8. По спаду сигнала синхронизации Ф2 (ТТЛ) генератора 4 тактовых сигналов, поступающему через элемент НЕ 1 1 на синхровход триггера 8, на единичнс М выходе триггера 8 формируется активный С1пнал запроса доступа к магистрали ЗДМ, а с нулевого выхода триггера 8 сигнал логического нуля поступает на разрешающий вход шинного формирователя 2 адреса, в результате чего адресные сигналы 15 микропроцессора подключаются к адресным шинам АДР интерфейсной магистрали 1. Память или периферийное устройство, к которому произошло обрашение, в случае своей

0

5

0

5

0

5

0

5

0

5

готовности выставляет сигнал ответа ОТВ, который поступает на вход готовности генератора 4 тактовых сигналов, в результате чего с выхода генератора 4 тактовых сигналов сигнал готовности ГТ поступает на вход готовности микропроцессора. Поэтому микропроцессор не входит в режим ожидания. Сигнал логической единицы с единичного выхода триггера 8 поступает на информационный вход триггера 9 и по сигналу синхронизации Ф2(ТТЛ), поступаюш.ему с выхода генератора 4 тактовых сигналов на синхровход триггера 9, с нулевого выхода триггера 9 сигнал логического нуля поступает на разрешающий вход дешифратора 3 команд, коммутируя шину данных микропроцессора с информационными шинами ИНФ интерфейсной магистрали 1 и подключая один из управляющих сигналов, формирующихся по коду слова состояния и сигналам приема ПР и выдачи ВД, к интерфейсной магистрали 1. По окончании действия сигнала приема ПР или выдачи ВД с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 12 сигнал логической единицы поступает на синхровход триггера б, в результате чего сигнал логического нуля с нулевого выхода триггера 6 поступает на входы сброса триггеров 6-9, снимая сигнал запроса доступа к магистрали ЭДМ и отключая сигналы адреса данных и управления, сформированные микропроцессором от интерфейсной магистрали 1.

Микропроцессор анализирует сигнал готовности ГТ, поступаюший с выхода генератора 4 тактовых сигналов по заднему фронту сигнала синхронизации Ф2. Если к этому вре.мени на вход готовности генератора 4 тактовых сигналов не поступил сигнал ответа ОТВ от устройства памяти или периферийного устройства, к которому произошло обрашение, микропроцессор переходит в режим ожидания, в котором готовность анализируется в каждом последующем такте, до tex пор пока не будет получен сигнал ответа ОТВ. Вход микропроцессора в режи.м ожидания происходит при работе с медленно действуюшими устройствами, которые сигнал ответа ОТВ выдают после прохождения фазы Ф2 в такте Т2.

В случае, если микропроцессор производит обрашение к памяти или периферийному устройству, а интерфейсная магистраль занята други.ми активными устройствамя (отсутствует сигнал разрешения доступа к магистрали РДМ), то аналогично на вход генератора 4 тактовых сигналов не поступает сигнал ответа ОТВ и с выхода генератора 4 тактовых сигналов на вход готовности микропроцессора поступает сигнал неготовности. В этом случае .микропроцессор также входит в режим ожидания. Как только магистраль освобождается (сигнал РДМ-1),

устройство устанавливает сигнал запроса доступа к магистрали ЗДМ и осуществляет обмен по интерфейсной магистрали 1.

В предлагаемом устройстве формируется диаграмма обмена по интерфейсной магистрали 1, в которой управляющие сигналы всегда вложены в адресные сигналы, что по- выщает помехоустойчивость. Диаграмма об мена по интерфейсной магистрали 1 (фиг. 3) приведена для случая, когда микропроцессор осуществляет прием информации. Аналогичная диаграмма обмена будет и в случае, когда микропроцессор выдает информацию.

Предлагаемое устройство в отличие от прототипа занимает интерфейсную магистраль только на время цикла обмена, а в промежутках между циклами обращения устройство осуществляет отключение сигналов микропроцессора от интерфейсной магистрали, и в это время она может быть использована для передачи данных другими активными устройствами. Во время выполнения внешним устройством цикла обмена микропроцессор может производить внутренние операции, связанные с обработкой данных, формированием адреса обращения и др.

Если при обращении к интерфейсной магистрали со стороны микропроцессора оказывается, что магистраль занята другими активными устройствами, микропроцессор переходит в состояние ожидания, аналогичное неготовности устройства, к которому произошло обращение. Как только магистраль освобождается, устройство осуществляет обращение. Предлагаемая организация связи микропроцессора с внещними устройствами и устройствами памяти позволяет в значительной степени повысить производительность микропроцессорных систем, содержащих несколько активных устройств.

Формула изобретения

1. Устройство для сопряжения микропроцессора с периферийными устройствами, содержащее шинный формирователь адреса, генератор тактовых сигналов, дешифратор команд, причем группа информационных входов шинного формирователя адреса образует группу входов устройства для подключения к группе адресных выходов микропроцессора, первая группа информационных входов-выходов дешифратора образует группу входов-выходов устройства для подключения к группе информационных входов-выходов микропроцессора, первый, второй информационные входы дешифратора команд являются входами устройства для подключения соответственно к выходам приема и выдачи микропроцессора, первый и второй тактовые выходы и выход готовности генератора тактовых сигналов являются выходами устрой0

5

ства для подключения соответственно к первому, второму тактовым входам и входу готовности микропроцессора, группа информационных выходов шинного формирователя адреса образует группу выходов устройства для подключения к группам адресных входов периферийных устройств, вторая гр уппа информационных входов-выходов дешифратора команд образует группу входов-выходов устройства для подключения к группам

0 информационных входов-выходов периферийных устройств, первый, второй, третий, четвертый информационные выходы дешифратора команд являются выходами устройства для подключения соответственно к пер5 вому, второму входам чтения, первому, второму входам записи периферийных устройств, вход готовности генератора тактовых сигналов является входом устройства д. о,ч- ключения к выхода.м готовности пер.феп.чй- ных устройств, при этом третий т лтовый выход генератора тактовых сиг - алов соединен с третьим информационным вхо.чом дешифратора команд, отличающееся тем, что, с целью, повышения быстродействия, в него введен блок асинхронной связи, причем синхровход генератора тактовых сигналов соехП.кнен с первым синхровходом блока асинхронной связи и является tixonoM устроко ва для подключения к синхровходу микро ;ро- цессора, выход запроса и вход разрсьаен -;; блока асин.хронкой янляк;гсн дом и входом yci-ройства для подключения соответственно к входам ;-;aiipoca и .вы: одам размещения периферийных устройсгв. up.-i этом разрешающие входы iiiiiHiio .x- ф - рователя адреса и дешифратора команд сое динены соответственно с первым i; -п-оры-,-; разрешающими выходами блика ас;;ихрс-: ной связи, первый, второй входы логического условия и второй сипхровхол которо:-о соединены соответственно с первым, вторым информационными входами дешифр.-ггора

0 команд и четвертым тактовы.м выходом генератора тактовых сигналов.

2. Устройство по п. 1, отличающееся тем, что блок асинхронной связи содержит четыре триггера, элемент И, элемент НЕ. .

5 ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый и второй вхэды элемента ИСК. 1ЮЧАЮШ,ЕЕ ИЛИ являются соответственно первым и вторым входами логического условия блока, первый вход элемен 1а И является входом

Q разрешения блока, синхровхол :iepBoro триггера является первым синхровходом блока, вход элемента НЕ соединен с синхровходом второго триггера и является вторым сиихро входом блока, единичный выход третьего триггера соединен с информационным вхо5 дом второго триггера и является выходом запроса блока, нулевые выходы третьего и второго триггеров являются соответственно первым и вторым разрешающими выхо0

5

дами блока, при этом в блоке асинхронного обмена выход элемента ИСКЛЮЧАЮЩЕЕ .ИЛИ соединен с синхровходом четвертого триггера, нулевой выход которого соединен с нулевыми входами второго, третьего, четвертого триггеров и с нулевым входом первого триггера, единичный выход которого

соединен с вторым входом элемента И, выход которого соединен с информационным входом третьего триггера, синхровход которого соединен с выходом элемента НЕ, информационные входы первого и четвертого триггеров подключены к шине единичного потенциала устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| Устройство для сопряжения микропроцессорной системы с внешними устройствами с контролем | 1984 |

|

SU1242956A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для обмена данными | 1989 |

|

SU1700562A1 |

| Устройство микропроцессорной связи | 1986 |

|

SU1361568A2 |

| Устройство для сопряжения абонентов с каналом связи | 1987 |

|

SU1432537A1 |

| Устройство для сопряжения абонента с магистралью в микропроцессорной системе | 1987 |

|

SU1538173A1 |

| Микропроцессорная система с встроенным контролем | 1986 |

|

SU1417651A1 |

| Устройство для связи микропроцессора с внешними устройствами | 1986 |

|

SU1372330A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано в микропроцессорных система.х управления и обработки данных. Целью изобретения является повышение быстродействия. Устройство содержит шинный формирователь 2 адреса, дешифратор 3 команд, i-e- нератор 4 тактовых сигналов, блок 5 асинхронной связи. 1 з.п. ф-лы, 3 ил.

п

Фиг,, г

Т2

тз

| Устройство микропроцессорной связи | 1983 |

|

SU1124275A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Коффрон Дж | |||

| Технические средства микропроцессорных систем.Практический курс | |||

| М.; Мир, 1983, с | |||

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-13—Подача