(54) УСТРОЙСТВО ДЛЯ СУММИРОВАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1979 |

|

SU911514A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1979 |

|

SU922728A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Устройство для извлечения квадратного корня | 1976 |

|

SU661550A1 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

| Сумматор в коде "М из N | 1981 |

|

SU981992A1 |

| Устройство для сложения и вычитания | 1980 |

|

SU922730A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для извлечения квадратного корня | 1977 |

|

SU684540A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в электроприводах постоянного и переменного тока с цифровым управлением.

По основному авт.св. № 7,39530 известен одноразрядный сумматор, в котором используется квадратная- матрица размеро.ми п/2 х п/2, где входные .шины одного слагаемого соеди-няются с первыми входами элементов И квадратной матрицы через блок логического дешифрирования, а входные шины другого слагаемого соединяются со вторыми входами элементов И этой квадратной матрицы через блок сложения переноса (матрица сложения переноса) размерами 2 х п/2. Выходные шины квадратной матрицы соединены с выходными шинами устройства через блок инвертирования, управляющий вход которого соединен с входной шиной второго слагаемого.

Устройство.отличается высоким быстродействием, содержит меньше элементов, но обладает ограниченным применением, так как не формирует сигнал переноса в старший разряд.

Цель изобретения - расширение -функциональных возможностей за .

счет формирования сигнала переноса в старший разряд, что делает ным построение полного сумматора в многофазном коде.

Цель достигается тем, что в него введен блок формирования сигнала переноса в старший разряд, выполненный на, четырех элементах И, двух элементах ИЛИ и двух элементах НЕ,

0 причем выхо,цы всех элементов И подключены ко входу первого элемента ИЛИ, выход которого является выходом переноса в старший разряд устройства, выход второго элемента

5 ИЛИ подключен к третьему входу первого элемента И и через первый элемент НЕ - к первому входу четвертого элемента И, вторые входы третьего и четвертого элементов И подключены

0 к инверсному входу первого слагаемого устройства, третий вход четвертого элемента И подключен к первому выходу блока сложений переноса, к первому входу первого элемента И

5 и через второй элемент НЕ - к первому входу третьего элемента И и второму входу второго элемента И, первый вход которого подключен ко входу первого слагаемого устройст;ва, второй вход первого элемента И

0

подключен к входу переноси из младшего разряда устройства, а третий вход - к первому входу элемента И в первом столбце и второй строке .матрицы элементов И, входы второго элемента ИЛИ подключены к выходам элементов И матрицы первого столбца и i-и строки (i 2,,..,п/2, где п - основание системы счисления) .

Описание устройства и его работа поясняются на примере системы с осгнованием п 10.

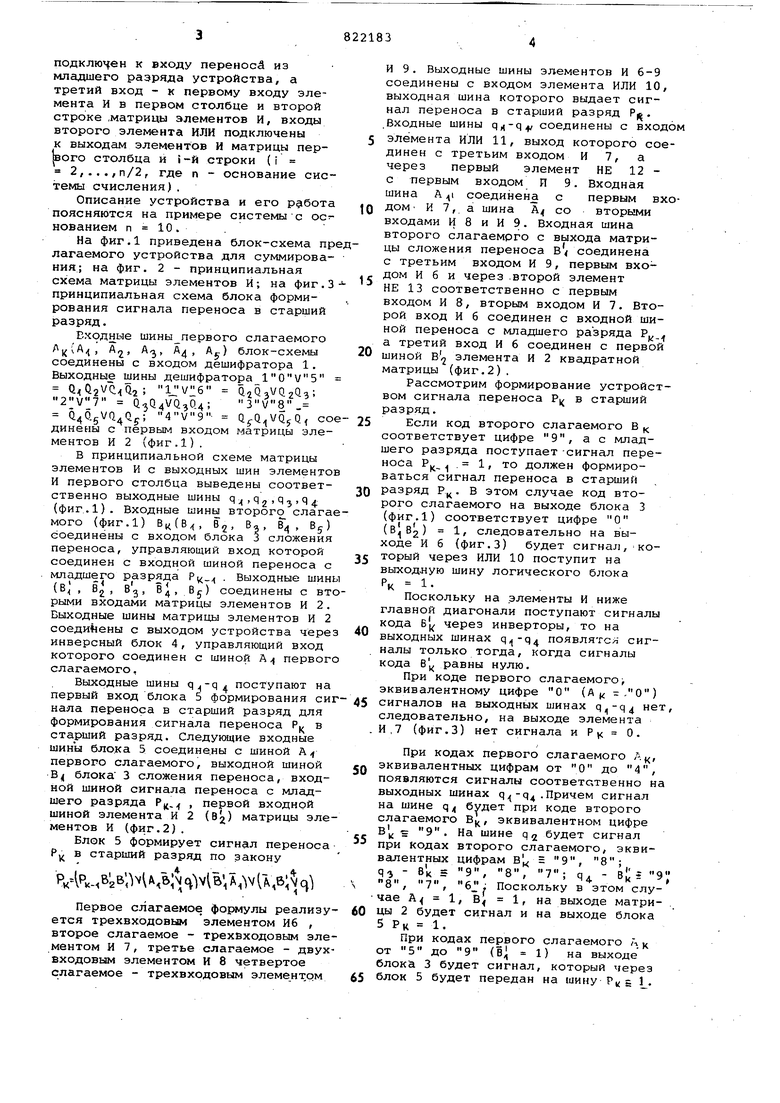

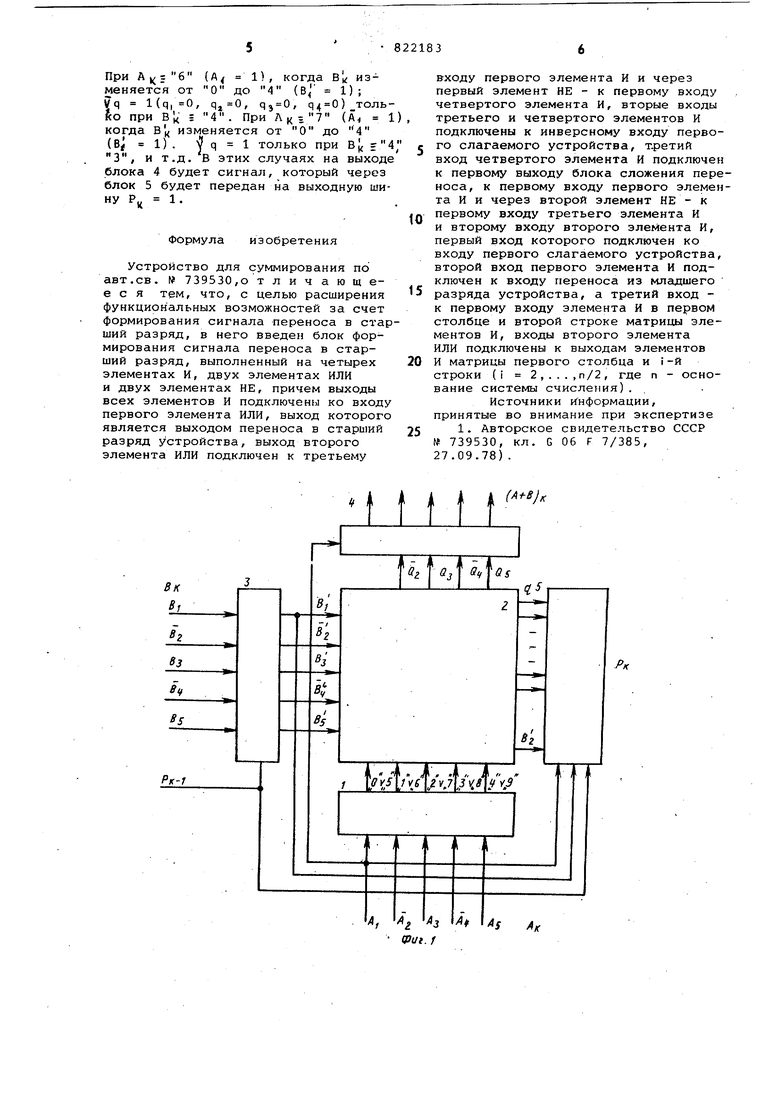

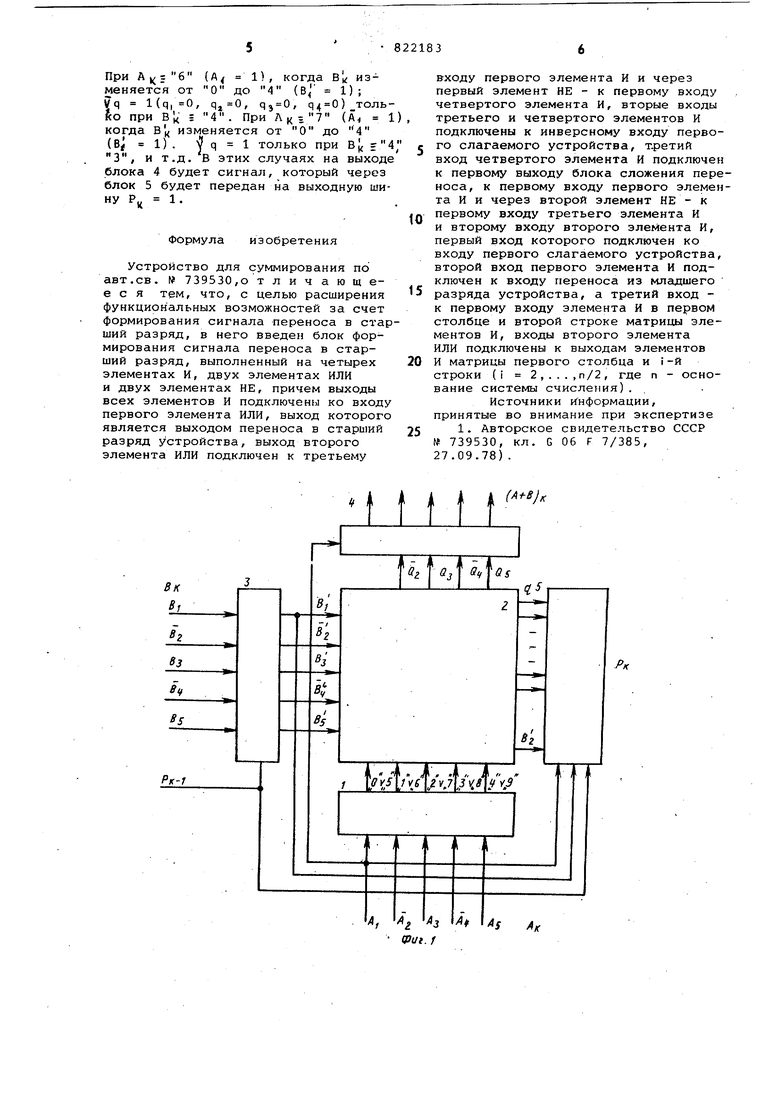

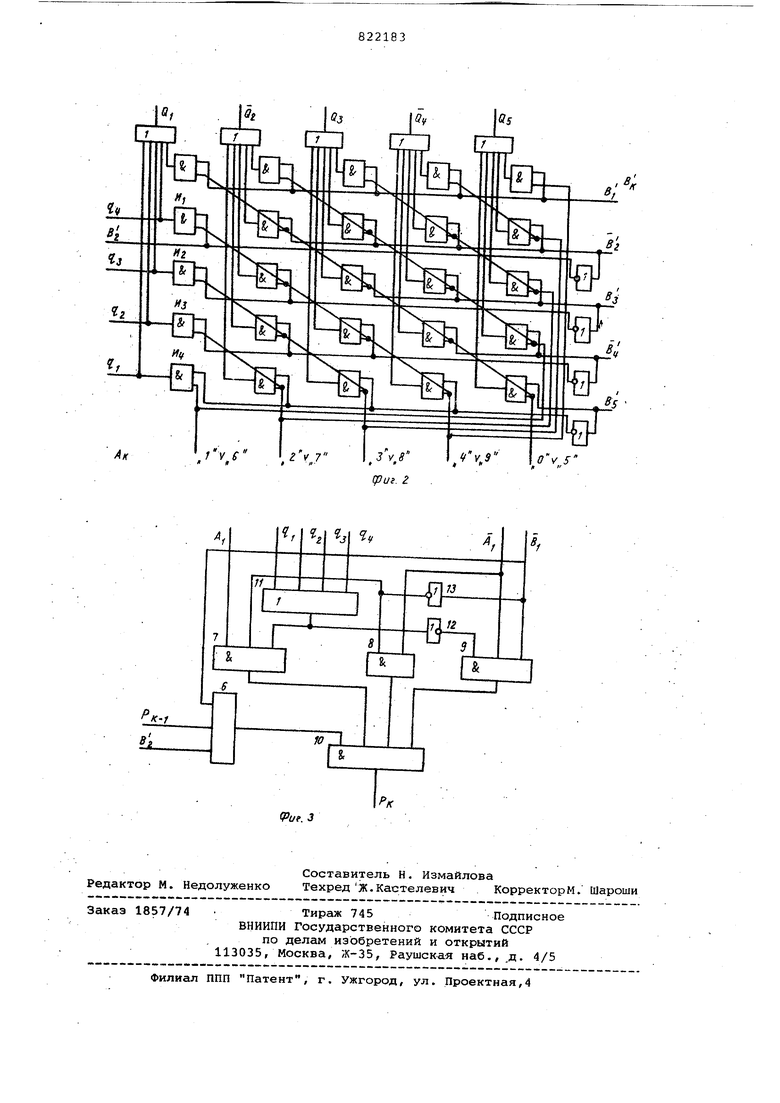

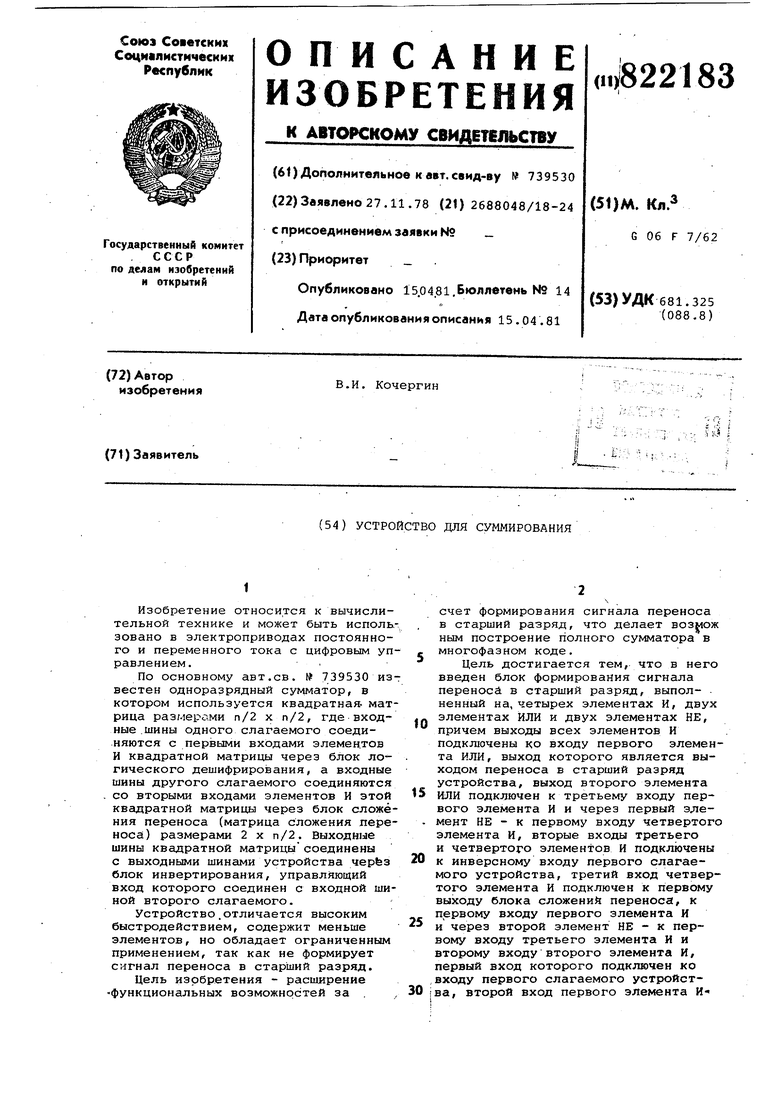

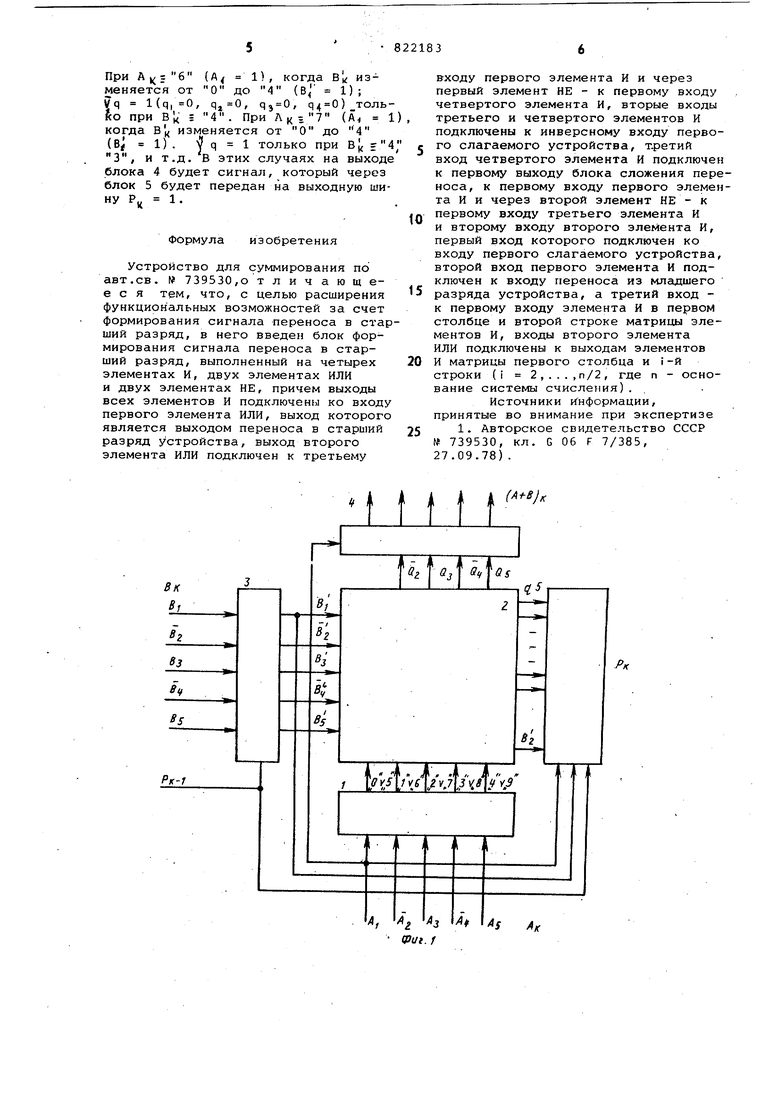

На фиг,1 приведена блок-схема прлагаемого устройства для суммирования; на фиг. 2 - принципиальная схема матрицы элементов И; на фиг . 3 принципиальная схема блока формирования сигнала переноса в старший разряд.

Входные шины первого слагаемого

АГ) блок-схемы

J 2, А,

Ах

соединены с входом дешифратора 1, Выходные шины дешифратора

Q..Q.2 i:v:i6 Q.Q4VQ,a4; . , , соединены с первьдм входом матрицы элементов И 2 (фиг.1).

В принципиальной схеме матрицы элементов И с выходных шин элементов И первого столбца выведены соответственно выходные шины Яц,д2,ЧзЧ4(фиг. 1). Входные шины второго слагаемого (фиг.1) В.(В, В 2, Вз, В , Bj) соединены с входом блока 3 сложения переноса, управляющий вход которой соединен с входной шиной переноса с младшего разряда P . Выходные шины (В , §2, вз, В, Bj) соединены с вторыми входами матрицы элементов И 2. Выходные шины матрицы элементов И 2 соеди41ены с выходом устройства через инверсный блок 4, управляющий вход которого соединен с шиной А первого слагаемого,

Выходные шины поступают на первый вход блока 5 формирования сигнала переноса в старший разряд для формирования сигнала переноса Р, в старший разряд. Следующие входные шины блока 5 соединены с шиной А первого слагаемого, выходной шиной B блока 3 сложения переноса, входной шиной сигнала переноса с младшего разряда Рц. , первой входной шиной элемента И 2 (Bj) матрицы элементов И (фиг.2) .

Блок 5 формирует сигнал переноса Р| в старший разряд по закону

рЛмВ2в; А.()у1в;А уи,в;)

Первое слагаемое формулы реализуется трехвходовым элементом И6 , второе слагаемое - трехвходовым элементом И 7, третье слагаемое - двухвходовым элементом И 8 четвертое слагаемое - трехвходовым элементрм

И 9. Выходные шины элементов И 6-9 соединены с входом элемента ИЛИ 10/ выходная шина которого выдает сигнал переноса в старший разряд Р. .Входные шины соединены с входом элемента ИЛИ 11, выход которого соединен с третьим входом И 7, а через первый элемент НЕ 12 с первым входом П 9. Входная шина А 1 соединена с первым вхоДОМ И 7,. а шина А со вторыми входами И 8 и И 9. Входная шина второго слагаемого с выхода матрицы сложения переноса В соединена с третьим входом И 9, первым входом И 6 и через .второй элемент НЕ 13 соответственно с первым входом И 8, вторым входом И 7. Второй вход И 6 соединен с входной шиной переноса с младшего разряда Р а третий вход И 6 соединен с первой

шиной в элемента И 2 квадратной матрицы (фиг.2).

Рассмотрим формирование устройством сигнала переноса PI в старший разряд.

Если код второго слагаемого В соответствует цифре 9, а с младшего разряда поступает -сигнал переноса Р . 1, то должен формироваться сигнал переноса в старший

разряд Р. в этом случае код второго слагаемого на выходе блока 3 (фиг.1) соответствует цифре О () 1, следовательно на выходе И б (фиг.З) будет сигнал,который через ИЛИ 10 поступит на выходлую шину логического блока

РК 1Поскольку на элементы И ниже

главной диагонали поступают сигналы кода В| через инверторы, то на

выходных шинах появлятся сигналы только тогда, когда сигналы кода В равны нулю.

При коде первого слагаемого эквивалентному цифре О (А « :;,0)

сигналов на выходных шинах q,-q4 нет,

следовательно, на выходе элемента И.7 (фиг.З) нет сигнала и Р | 0.

При кодах первого слагаемого /.ц,

эквивалентных цифрам от О до 4, появляются сигналы соответственно на выходных шинах .Причем сигнал на шине q будет при коде второго слагаемого В, эквивалентном цифре В - 9. На шине q2 будет сигнал

при кодах второго слагаемого, эквивалентных цифрам Вц; 9, q - Вк 5 9, 8, q -

8, 7, 6 Поскольку в этом случае А 1, В 1, на выходе матри- .

цы 2 будет сигнал и на выходе блока

5 РК 1.

При кодах первого слагаемого А от 5 до 9 (В 1) на выходе блока 3 будет сигнал, который через блок 5 будет передан на шину Р 1 . (А 1), когда в изПри А 1 6 меняется от О до 4 ( 1); Vq l(, , q5 0, q4 0)тoль fto при В к 4. При (А когда Вк изменяется от О до 4 (uf 1) . я 1 только при BJ г 3, и т.д. В этих случаях на выходе блока 4 будет сигнал, который через блок 5 будет передан на выходную шину Ру 1. Формула изобретения Устройство для суммирования по авт.св. № 739530,о тличающее с я тем, что, с целью расширения функциональных возможностей за счет формирования сигнала переноса в стар ший разряд, в него введен блок формирования сигнала переноса в старший разряд, выполненный на четырех элементах И, двух элементах ИЛИ и двух элементах НЕ, причем выходы всех элементов И подключенвл ко входу первого элемента ИЛИ, выход которого является выходом переноса в старший разряд Устройства, выход второго элемента ИЛИ подключен к третьему

Вк В,

В,

83

8V

85

Ss

Рк-1

(A1-BJK

ff

Ss

Зг

45

PK

;

t« I I л , л -, ууЛ чД71; а -,

At

5 AK

i 3

фаг. f входу первого элемента И и через первый элемент НЕ - к первому входу четвертого элемента И, вторые входы третьего и четвертого элементов И подключены к инверсному входу первого слагаемого устройства, т.ретий вход четвертого элемента И подключен к первому выходу блока сложения переноса, к первому входу первого элемента И и через второй элемент НЕ - к первому входу третьего элемента И и второму входу второго элемента И, первый вход которого подключен ко входу первого слагаемого устройства, второй вход первого элемента И подключен к входу переноса из млгщшего разряда устройства, а третий вход к первому входу элемента И в первом столбце и второй строке матрицы элементов И, входы второго элемента ИЛИ подключены к выходам элементов И матрицы первого столбца и i-и строки (i 2,...,п/2, где п - основание системы счисления). , Источники и нформации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 739530, кл. G 06 F 7/385, 27.09.78) .

Авторы

Даты

1981-04-15—Публикация

1978-11-27—Подача