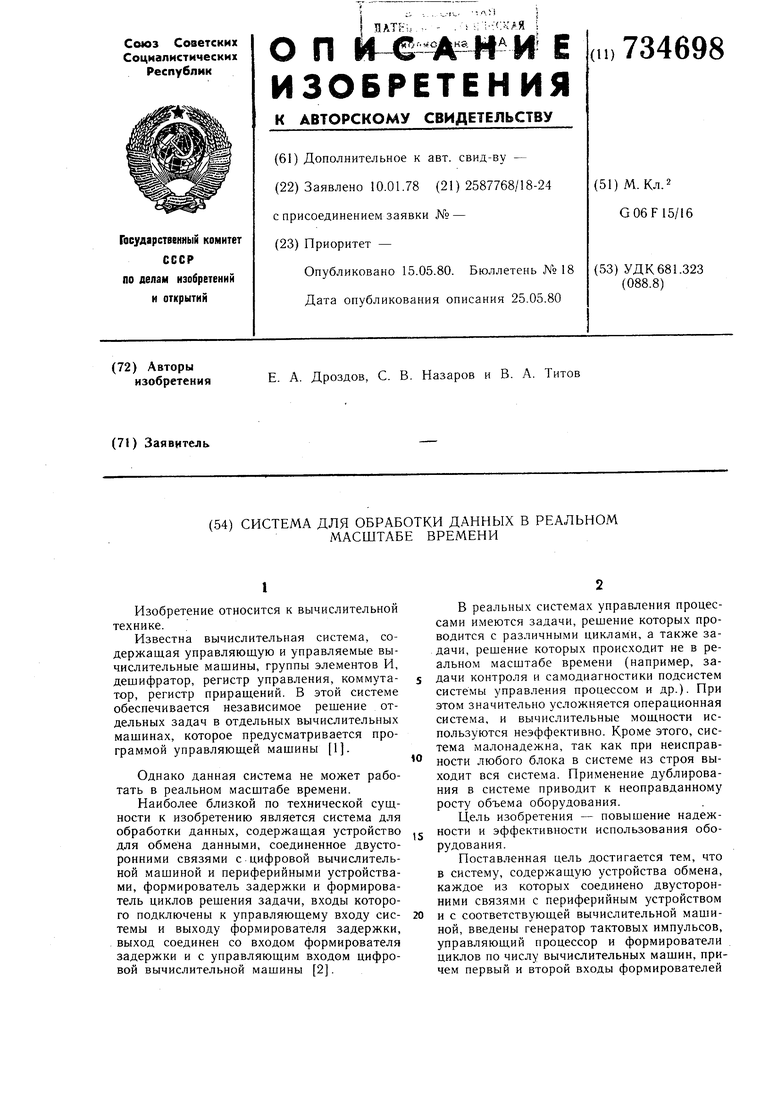

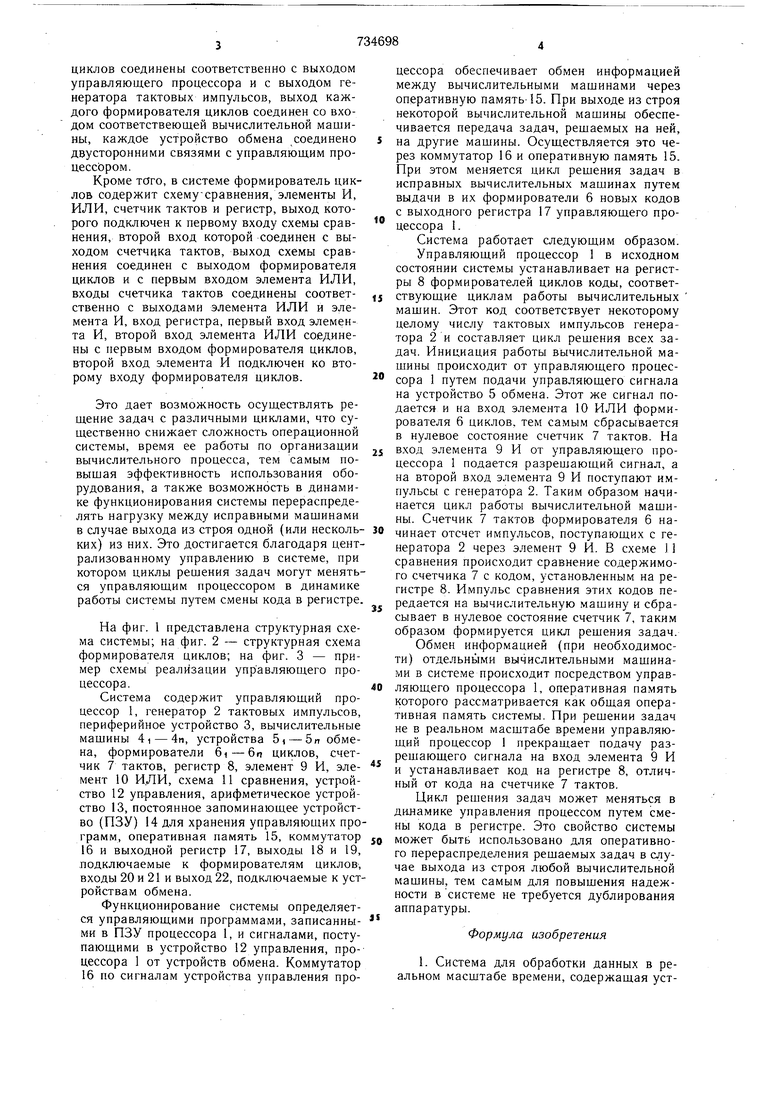

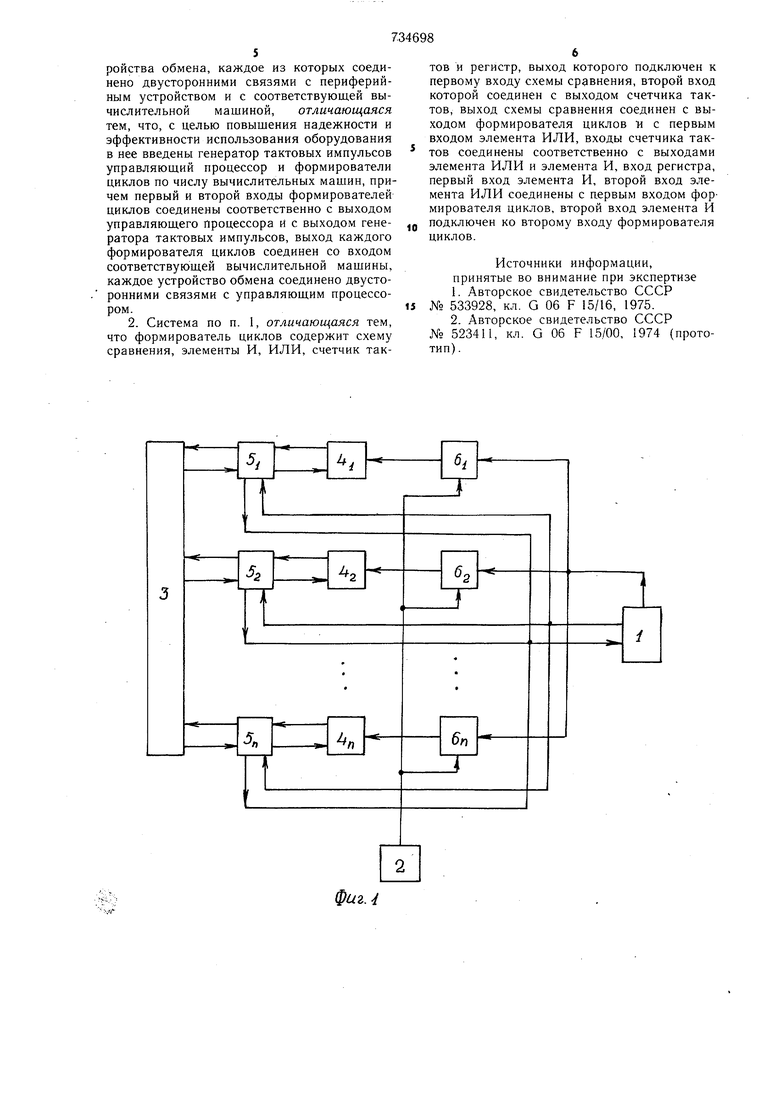

Изобретение относится к. вычислительной технике. Известна вычислительная система, содержащая управляющую и управляемые вычислительные мащины, группы элементов И, дещифратор, регистр управления, коммутатор, регистр приращений. В этой системе обеспечивается независимое рещение отдельных задач в отдельных вычислительных мащинах, которое предусматривается программой управляющей машины 1. Однако данная система не может работать в реальном масштабе времени. Наиболее близкой по технической сущности к изобретению является система для обработки данных, содержащая устройство для обмена данными, соединенное двусторонними связями с цифровой вычислительной машиной и периферийными устройствами, формирователь задержки и формирователь циклов решения задачи, входы которого подключены к. управляющему входу сиетемы и выходу формирователя задержки, выход соединен со входом формирователя задержки и с управляющим входом цифровой вычислительной машины 2. В реальных системах управления процессами имеются задачи, решение которых проводится с различными циклами, а также задачи, решение которых происходит не в реальном масштабе времени (например, задачи контроля и самодиагностики подсистем системы управления процессом и др.). При этом значительно усложняется операционная система, и вычислительные мощности используются неэффективно. Кроме этого, система малонадежна, так как при неисправности любого блока в системе из строя выходит вся система. Применение дублирования в системе приводит к неоправданному росту объема оборудования. Цель изобретения - повышение надежности и эффективности использования оборудования. Поставленная цель достигается тем, что в систему, содержащую устройства обмена, каждое из которых соединено двусторонними связями с периферийным устройством и с соответствующей вычислительной машиной, введены генератор тактовых импульсов, управляющий процессор и формирователи циклов по числу вычислительных мащин, причем первый и второй входы формирователей циклов соединены соответственно с выходом управляющего процессора и с выходом генератора тактовых импульсов, выход каждого формирователя циклов соединен со входом соответствеющей вычислительной машины, каждое устройство обмена соединено двусторонними связями с управляющим процессором. Кроме того, в системе формирователь циклов содержит схемусравнения, элементы И, ИЛИ, счетчик тактов и регистр, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом счетчнка тактов, выход схемы сравнения соединен с выходом формирователя циклов и с первым входом элемента ИЛИ, входы счетчика тактов соединены соответственно с выходами элемента ИЛИ и элемента И, вход регистра, первый вход элемента И, второй вход элемента ИЛИ соединены с первым входом формирователя циклов, второй вход элемента И подключен ко второму входу формирователя циклов. Это дает возможность осуществлять рещение задач с различными циклами, что существенно снижает сложность операционной системы, время ее работы по организации вычислительного процесса, тем самым повышая эффективность использования оборудования, а также возможность в динамике функционирования системы перераспределять нагрузку между исправными машинами в случае выхода из строя одной (или нескольких) из них. Это достигается благодаря централизованному управлению в системе, при котором циклы решения задач могут меняться управляющим процессором в динамике работы системы путем смены кода в регистре. На фиг. 1 представлена структурная схема системы; на фиг. 2 - структурная схема формирователя циклов; на фиг. 3 - пример схемы реализации управляющего процессора. Система содержит управляющий процессор 1, генератор 2 тактовых импульсов, периферийное устройство 3, вычислительные машины 4i - 4п, устройства 5i - 5л обмена, формирователи 6i - бгт циклов, счетчик 7 тактов, регистр 8, элемент 9 И, элемент 10 ИЛИ, схема 11 сравнения, устройство 12 управления, арифметическое устройство 13, постоянное запоминающее устройство (ПЗУ) 14 для хранения управляющих про грамм, оперативная память 15, коммутатор 16 и выходной регистр 17, выходы 18 и 19, подключаемые к формирователям циклов-, входы 20 и 21 и выход 22, подключаемые к уст ройствам обмена. Функционирование системы определяется управляющими программами, записанными в ПЗУ процессора 1, и сигналами, поступающими в устройство 12 управления, процессора 1 от устройств обмена. Коммутатор 16 по сигналам устройства управления процессора обеспечивает обмен информацией между вычислительными машинами через оперативную память-15. При выходе из строя некоторой вычислительной машины обеспечивается передача задач, рещаемых на ней, на другие машины. Осуществляется это через коммутатор 16 и оперативную память 15. При этом меняется цикл рещения задач в исправных вычислительных машинах путем выдачи в их формирователи 6 новых кодов с выходного регистра 17 управляюшего процессора 1. Система работает следующим образом. Управляющий процессор 1 в исходном состоянии системы устанавливает на регистры 8 формирователей циклов коды, соответствующие циклам работы вычислительных машин. Этот код соответствует некоторому целому числу тактовых импульсов генератора 2 и составляет цикл решения всех задач. Инициация работы вычислительной машины происходит от управляющего процессора 1 путем подачи управляющего сигнала на устройство 5 обмена. Этот же сигнал подается и на вход элемента 10 ИЛИ формирователя 6 циклов, тем самым сбрасывается в нулевое состояние счетчик 7 тактов. На вход элемента 9 И от управляющего процессора 1 подается разрешающий сигнал, а на второй вход элемента 9 И поступают импульсы с генератора 2. Таким образом начинается цикл работы вычислительной машины. Счетчик 7 тактов формирователя 6 начинает отсчет импульсов, поступающих с генератора 2 через элемент 9 И. В схе.ме 11 сравнения происходит сравнение содержимого счетчика 7 с кодом, установленным на регистре 8. Импульс сравнения этих кодов передается на вычислительную машину и сбрасывает в нулевое состояние счетчик 7, таким образом формируется цикл решения задач. Обмен информацией (при необходимости) отдельнь1ми вычислительными машинами Б системе происходит посредством управляющего процессора 1, оперативная память которого рассматривается как общая оперативная память системы. При рещении задач не в реальном масщтабе времени управляющий процессор 1 прекращает подачу разрешающего сигнала на вход элемента 9 И и устанавливает код на регистре 8, отличный от кода на счетчике 7 тактов. Цикл решения задач может меняться в диламике управления процессом путем смены кода в регистре. Это свойство системы может быть использовано для оперативного перераспределения решаемых задач в случае выхода из строя любой вычислительной машины, тем самым для повышения надежности в системе не требуется дублирования аппаратуры. Формула изобретения 1. Система для обработки данных в реальном масщтабе времени, содержашая устройства обмена, каждое из которых соединено двусторонними связями с периферийным устройством и с соответствующей вычислительной машиной, отличающаяся тем, что, с целью повышения надежности и эффективности использования оборудования в нее введены генератор тактовых импульсов управляющий процессор и формирователи циклов по числу вычислительных машин, причем первый и второй входы формирователей циклов соединены соответственно с выходом управляющего процессора и с выходом генератора тактовых импульсов, выход каждого формирователя циклов соединен со входом соответствующей вычислительной машины, каждое устройство обмена соединено двусторонними связями с управляющим процессором.

2. Система по п. 1, отличающаяся тем, что формирователь циклов содержит схему сравнения, элементы И, ИЛИ, счетчик тактов и регистр, выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом счетчика тактов, выход схемы сравнения соединен с выходом формирователя циклов и с первым входом элемента ИЛИ, входы счетчика тактов соединены соответственно с выходами элемента ИЛИ и элемента И, вход регистра, первый вход элемента И, второй вход элемента ИЛИ соединены с первым входом формирователя циклов, второй вход элемента И подключен ко второму входу формирователя циклов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 533928, кл. G 06 F 15/16, 1975.

2.Авторское свидетельство СССР

№ 523411, кл. G 06 F 15/00, 1974 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для вывода информации | 1979 |

|

SU773613A1 |

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для сбора данных о загрузке узлов электронной вычислительной машины | 1975 |

|

SU532102A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ РЕГЕНЕРАЦИЕЙ В ПОЛУПРОВОДНИКОВОМ ДИНАМИЧЕСКОМ ЗАПОМИНАЮЩЕМ УСТРОЙСТВЕ | 1994 |

|

RU2040808C1 |

| Устройство для централизованного управления вычислительной системой | 1985 |

|

SU1259261A1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

фиг. 4

Авторы

Даты

1980-05-15—Публикация

1978-01-10—Подача