1

Изобретение относится к вычисли- тельной технике и может быть использовано при построении устройств обмена управлякяцих вычислительных систем с периферийными устройствами, j

Для согласованной работы системы с периферийными устройствами канал обмена должен обеспечивать необходимые частоты передачи и определенные (разовые соотнесения между передавае- Q 1/1ЫМИ сигналами, которые зависят от ;длины канала связи и параметров периферийных устройств.

Известно вычислительное устройство j обеспечивающее передачу данных на нескольких частотах и содержащее в каждом канале интерфейсный адаптер, снабженный преобразователем параллельного, кода в последовательный, регистром выбора часто- 20 .ты, генератором синхроимпульсов и мультиплексором.

Устройство передает информацию на частоте, код которой установлен Е регистре выбора частоты центральным 25 обрабатывающим устройством II

Недостатком известных устройств является фиксированный набор нескольких частот передачи и.жесткие фазовые соотношения между передаваемы- JQ

ми сигналами, что ограничивает об,-. ;ласть применения устройств.

Наиболее близким по технической сущности к предложенному является устройство для вывода данных из процессора, содержащее блоки сопряжения, управления, согласованияJ регистр обмена, генератор тактовой частоты, блок задания режима вывода, причем входы устройства связаны с первыми входами блока управления и регистра обмена, выход которого подключен ко входам блоков сопряжения и первенцу входу блока задания режима вывода, выход генератора тактовой частоты соединен со вторым входом блока управления, выход которого подключен ко вторым входам регистра обмена и блоку задания режима вывода, выход блока режима вывода соединен с третьим входом блока управления , выходы блоков сопряжения подключены ко входам блока согласования, выходы которого являются выходами устройства 2.

Недостатком этого устройства являются большие аппаратурныезатраты, требуемые при использовании его для работы с различными типами периферийных устройств.

Цель изобретения - сокращение ап.паратурных затрат.

Поставленная цель достигается тем что в устройство, содержащее буферную память, информационный вход которой является, входом устройства, а .информационные выходы соединены с соответствующими информационными входами сдвигового регистра,формирователь синхроимпульсов и узел сопряжения, выход которого является выходо устройства, введены память управления, три элемента И и группа элементов И, причем первые выходы форми рователя синхроимпульсов и памяти управления подключены к соответствующим входам первого элемента И, выходом соединенного с управляющим входом буферной памяти, вторые выходы - к соответствующим входам второго элемента И, выходом соединенного с управляющим входом памяти управления, а третьи выходы к соответствующим входам третьего элемента И, выходом срединенного с первым управляющим входом сдвигового регистра, выходы которого- подключены к первым входам соответствующих элементов И групп, а второй управляющий вход - к четвертому выходу памяти управления, информационный вход которой соединен с входом устройства, пятый выход - со вторыми входами элементов И группы, а группа входов - с группой входов узла сопряжения, соответствующие входы которого подключены к выходам элементов И группы.

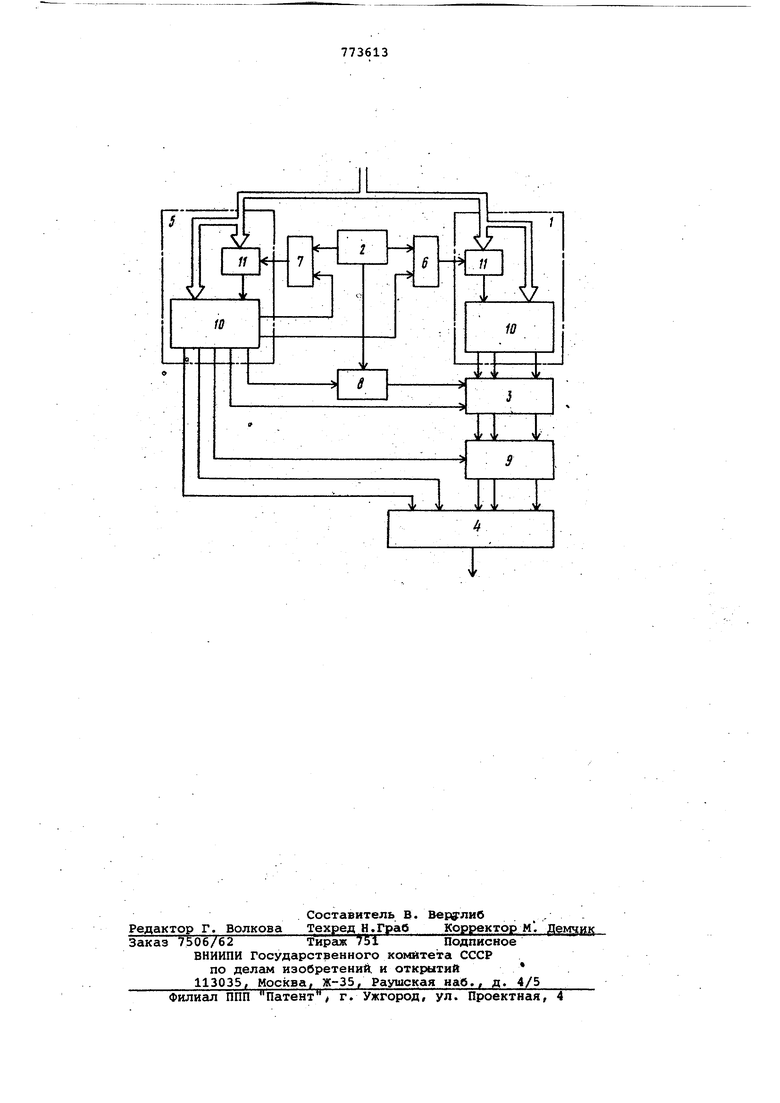

На чертеже представлена блоксхема устройства.

Устройство содержит буферную память (БЗУ-) 1, формирователь 2 синхроимпульсов , сдвиговый регистр 3, узел 4 сопряжения,память 5 управления (ЗУУ), первый 6, второй 7 и тре тий 8 элементы И и группу элементов И 9.

Буферна, память и память управления содержат запоминающий модуль 10 и счетчик 11 адреса, причем в памяти управления в качестве тако го модуля может быть использован модуль с оперативной сменой информации.

Устройство работает следующим образом.

Перед началом работы устройства производится его предварительная настройка, которая осуществляется по информации, поступающей на вход устройства. .

По сигналам, поступающим на вход устройства, производится запрет приема внутренних управляющих сигналов , поступающих на управляющие входы БЗУ 1 и ЗУУ 5, после чего ЗУУ 5 (и БЗУ 1, если БЗУ - оперативная память) загружается информацией, необходимой для передачи. По оконча

НИИ загрузки счетчики 11 адресов ЗУУ 5 и БЗУ 1 устанавливаются в исходное состояние, соответствующее сщресам первых слов, которые должны быть считаны.

5 Б конце загрузки ЗУУ 5 и БЗУ 1 переводятся в режим .Чтение, после чего снимается запрет приема внутренних управляющих сигналов.

При наличии нужной для передачи

Q информации в ЗУУ 5 настройка заключается только в установке начальных адресов, передаваемых с магистральной линии.

Временные положения передаваемых сигналов в устройстве изменяются с дискретом, равным циклу работы. ЗУУ 5. Передача данных происходит под действием управляющих сигналов, поступающих с ЗУУ. При установлении БЗУ 1 и ЗУУ 5 в режим Чтение

0 на выходе БЗУ 1 появляется первое передаваемое слово, на выходе ЗУУ 5 первое слово управления передачей. Первое слово, считываемое из ЗУУ, содержит 1 на втором, третьем

выходах и О на первом, четвертом, пятом выходах.

Наличие 1 на втором выходе ЗУУ 5 обеспечивает увеличение содержимого счетчика 11 ЗУУ 5 на единицу для формирования управляющего слова

следующего такта работы устройства.

Нулевой сигнал на четвертом выходе ЗУУ 5 переводит сдвиговыйрегистр 3 в режим приема параллельного кода из БЗУ 1, который записывается в сдвиговый регистр 3 по импульсу, посупающему от формирователя 2, Разрешение на поступление импульса определяется 1 на

третьем выходе ЗУУ 5.

Нулевые сигналы на пятом и первом выходах ЗУУ 5 запрещают прохождение информации из сдвигового регистра 3 на входы узла 4 сопряжения, а также изменение адреса БЗУ 1.

На втором такте работы устройства на выходах ЗУУ 5 появляется

код 01001, Этот код запрещает изме.нение адреса БЗУ 1 (О на первом выходе) , разрешает изменение адреса ЗУУ 5 (1 на втором выходе)запрещает изменение информации на сдвиговом регистре 3 (О на третьем выходе) , сохраняет режим сдвигового регистра 3 (О на четвертом выходе)и разрешает прохождение информации из сдвигового регистра 3 на узел 4 сопряженц. Если требуется передать

информационный импульс заданной,длины, то из ЗУУ 5 последовательно считывается последовательность управляющих слов, содержащих в разрядах с первого по пятый вышеописанный

код 01001. После .окончания передачи.

ймпульса идет передача паузы, которая формируется выдачей управляющих слов с кодом 01000, Этот код отличается от предыдущего нулем на пятом выходе ЗУУ 5,по; которому происходит запрет выдачи на узел 4 сопряжения информации сдвигового регистра 3. Длительность паузы, так же как и длительность импульса, определяется числом считываемых из ЗУУ 5 слов, имеющих код 01000.

В течение паузы, в зависимости от того идет передача параллельным кодом или последовательным, возможно принять новую- информацию в сдвиговый регистр 3 или сдвинуть старую.

Прием информации в сдвиговый регистр 3 во время паузы обеспечи-вается кодом 11000, отличающимся от предыдущего наличием 1 в первом выходе ЗУУ 5, что обеспечивает увеличение содержимого счетчика 11 на БЗУ 1 на единицу и выдачу в начале следующего такта нового информационного слова, которое записывается в сдвиговый регистр 3 по коду 01100.

Сдвиг информации в течение паузы обеспечивается кодом 01110.

Передача последующих разрядов или слов из БЗУ 1 происходит аналогично.

Параллельно с передачей информационных сигналов возможна передача служебных сигналов по группе ЗУУ 5, длительности которых также определяются числом последовательно считываемых из ЗУУ слов, содержащих 1 в соответствунйдих разрядах.

Конец передачи инициируется появлением на выходах ЗУУ 5 кода 00000, по которому запрещается изменение счетчиков 11 ЗУУ и БЗУ, .запись в сдвиговый регистр 3 и передача информации из него на входы узла 4 сопряжения.

Запрет изменения счетчика 11 ЗУУ 5 обеспечивает циклическое повторение этого режима, до тех пор пока процессор не произведет новую настройку.

Группа выходов ЗУУ 5 во время циклической вьщачи кода конца fiepeдачи может быть обнулена или содержать какой-нибудь код, сигнализиру,н:щий о том, что передача данных око.чена.

Таким образом, устройство обеспечивает передачу информации с произвольным временным расположением передаваемых сигналов, что позволяет исключить необходимость использования блоков временного

преобразования передаваемых сигналов для периферийных устройств разных типов и этим сокращается объем оборудования устройства, Дискрет изменения временных параметров передаваемых сигналов определяется циклом работы памяти управления. При реализации этой памяти на больших интеграшьных схемах, например серии 500, этот дискрет не превышает 50 не,

0 ,что обеспечивает формирование сигналов с требуемыми временными параметрами и фазовыми соотношениями при подключении новых периферийных устройств без переделки аппаратуры.

5

Формула изобретения

Устройство для вывода информации, содержащее буферную память,

0 информационный вход которой является входом устройства, а информационные выходы соединены с соответствующими информационными входами сдвигового регистра, формирователь-синхро5импульсов и узел сопряжения, выход которого является выходом устройства, отличающееся тем, что, с целью сокращения аппаратурных затрат, в него введены па0мять управления, три элемента И и группа элементов И, причем первые выходы формирователя синхроимпуль.сов и памяти управления подключены к соответствующим входам первого

5 элемента И, выходом соединенного с управляющим входом буферной памяти, вторые выходы - к соответствующим входам второго элемента И, выходом соединенного с управляющим входом памяти управления, а третьи выходы 0к соответствующим входам третьего элемента И, выходом соединенного с первым управляющим входом сдвигового регистра, выходы которого подключены к первым входам соответствую5щих элементов И группы, а второй управляющий вход - к четвертому выходу памяти управления, информационный вход которой соединен с входом устройства, пятый выход - со вторыми

0 входами элементов И группы, а группа выходов - с группой входов узла сопряжения, соответствующие входы которого подключены к выходам элементов И группы.

Источники информации,

5 принятые во внимание при экспертизе

1.Патент США № 4052702, кл. 364-200, 1977.

2.Авторское свидетельство СССР № 526880, кл. G Об F 3/04, 1976

0 (прототип).

7 1

1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для контроля цифровых интегральных схем | 1978 |

|

SU943747A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Буферное запоминающее устройство | 1988 |

|

SU1583938A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1987 |

|

SU1451707A1 |

| Система для обмена данными между информационными процессорами | 1980 |

|

SU1001070A1 |

| Устройство для вывода информации | 1983 |

|

SU1094040A1 |

| Устройство для сопряжения электронных вычислительных машин | 1984 |

|

SU1257653A2 |

| Устройство для сопряжения ЭВМ с каналом связи | 1988 |

|

SU1656544A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

Авторы

Даты

1980-10-23—Публикация

1979-04-11—Подача