нйя записью и считыванием, при этом информационные входы первого и второго блоков памяти соединены между собой, первый выход блока управления записью и сЧйтаванием подключен к управляющему входу первого блока памяти, второй выход управления записью и считыванием сйедийен, с управляющим входом второго блока памяти, а третий выход блока управления записью и считыванием подключен к входу блока считывания информации, причем выход второго блока памяти соединен с третьим входом распределителя, при этом блок считывания информации состоит

из первого, второго и третьего триггеров, причем вь1ход первого триггера подключен к первому входу третьего триггера, второй вход которого соединен с первым входом первого триггера, второй вход которого подключен к первому входу второго и третьему входу третьего триггеров, а второй вход

Stopdro триггера соединен свыходом третьего триггера, при этомпервый вход второго триггера является входом блока считывания,

8 выход третьего триггера является выходом блока считывания.

В способе приема информации в многоканальных системах связи с ИКМ производят запись информационного сигнала одного канального интервала из тракта с ИКМ в первый блок памяти, последующего канального интервала - во второй блок памяти, с та.ктовой частотой группового сигнала, а считывание информационных сигналов производят поочередно из каждого блока памяти отдельЕго в середине времени записи информации в другой блок памяти,

Прй этом одновременно производят последбвательно-параллельное преобразование информационных сигналов.

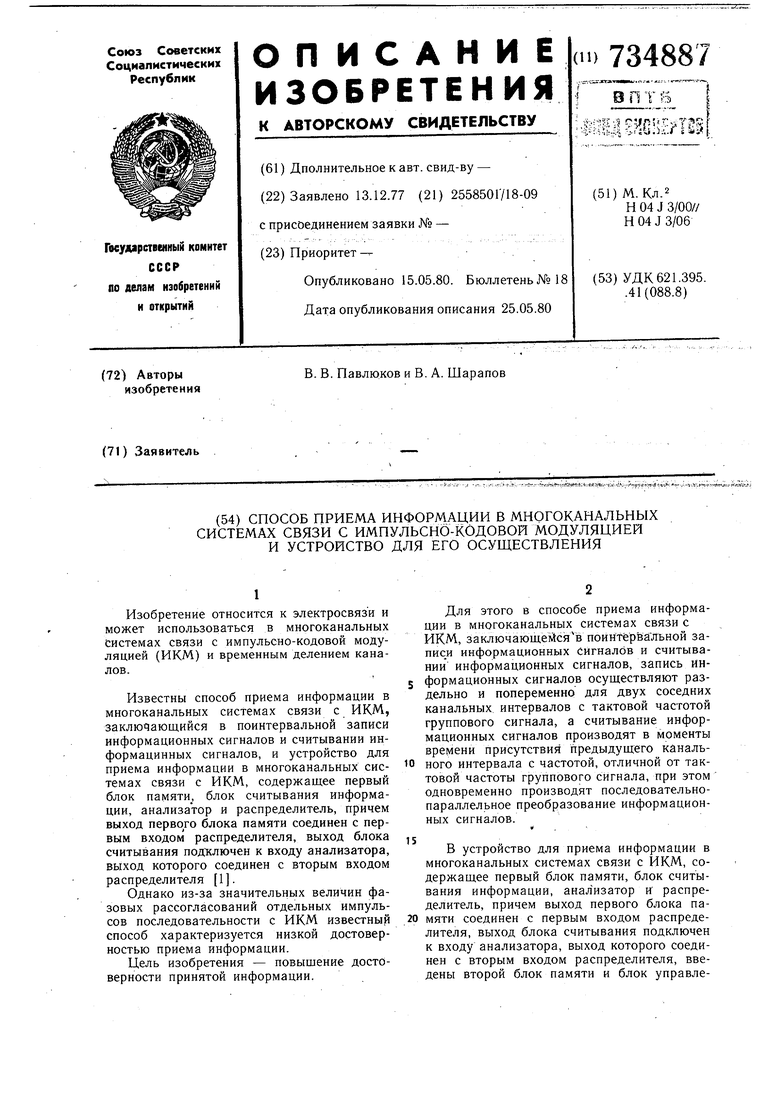

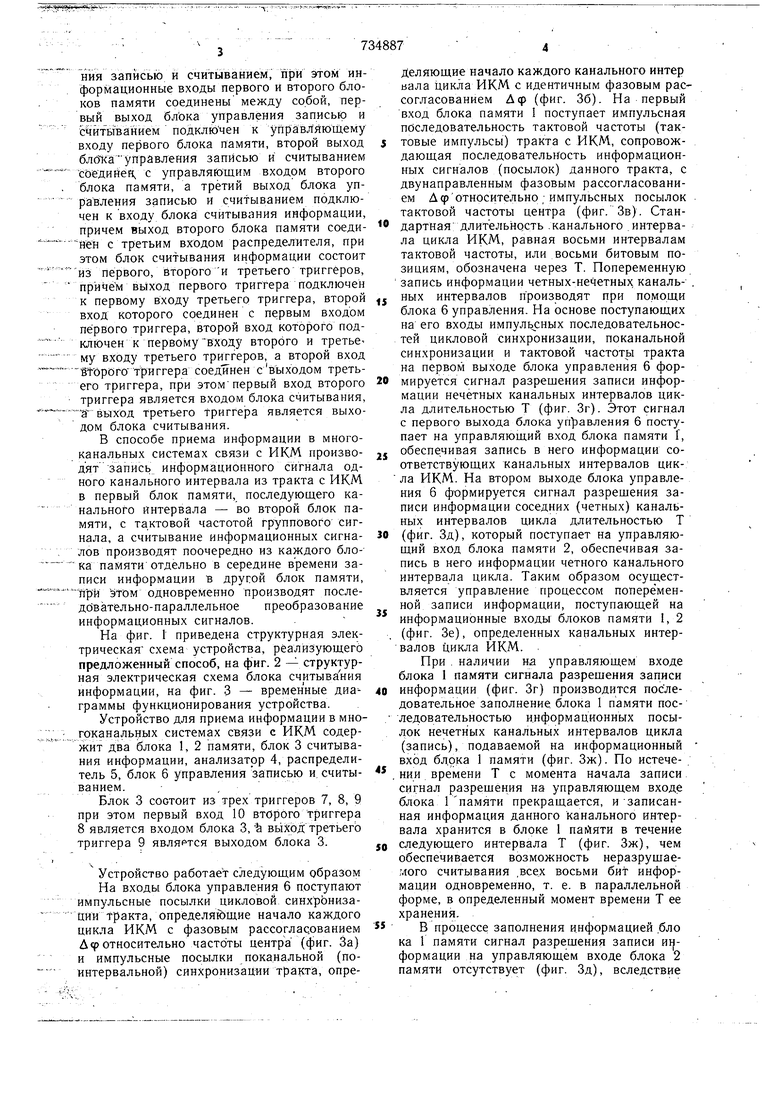

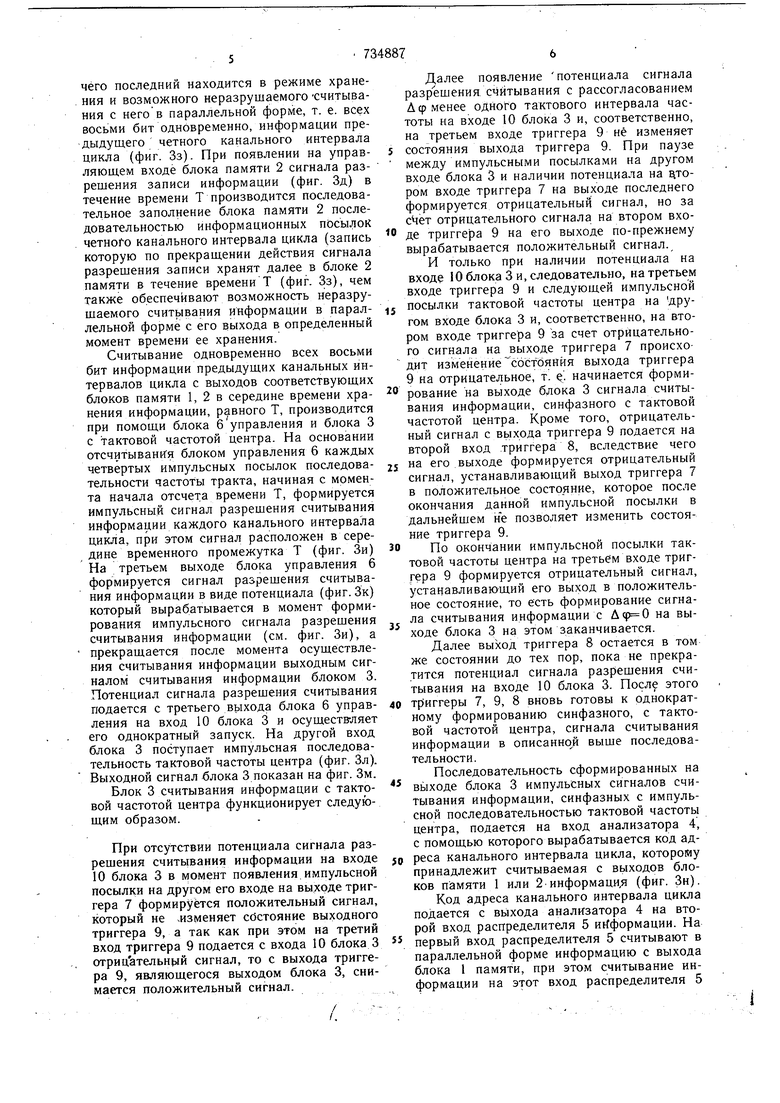

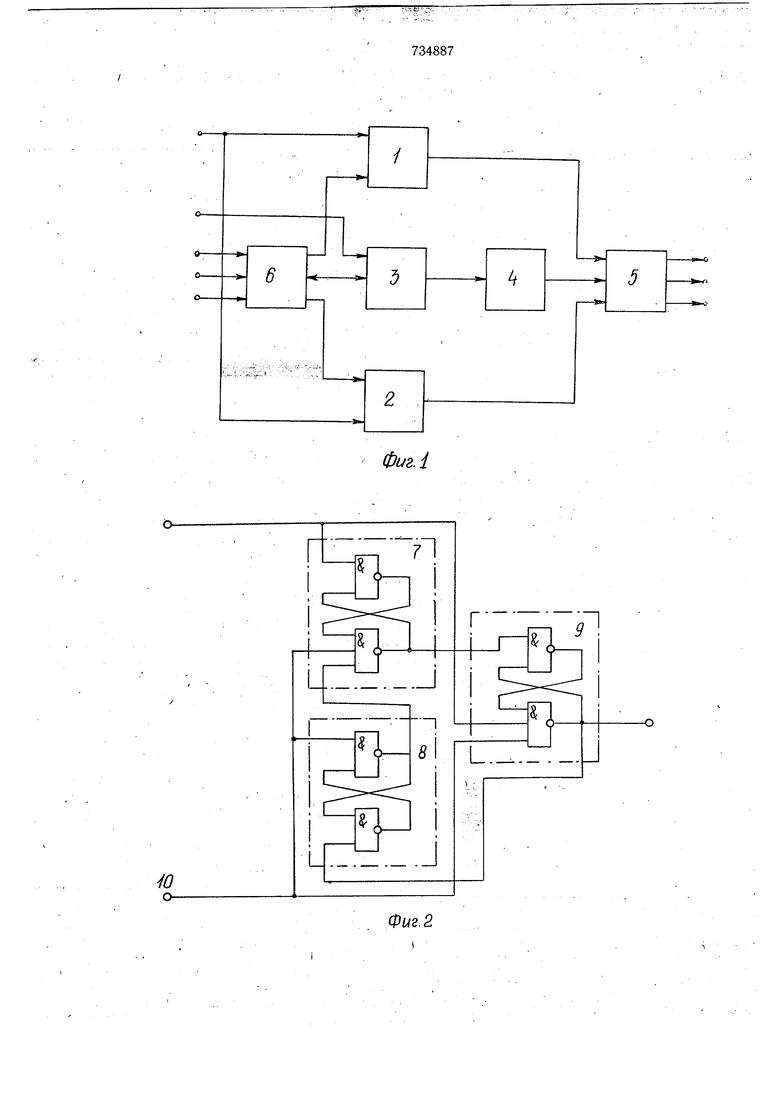

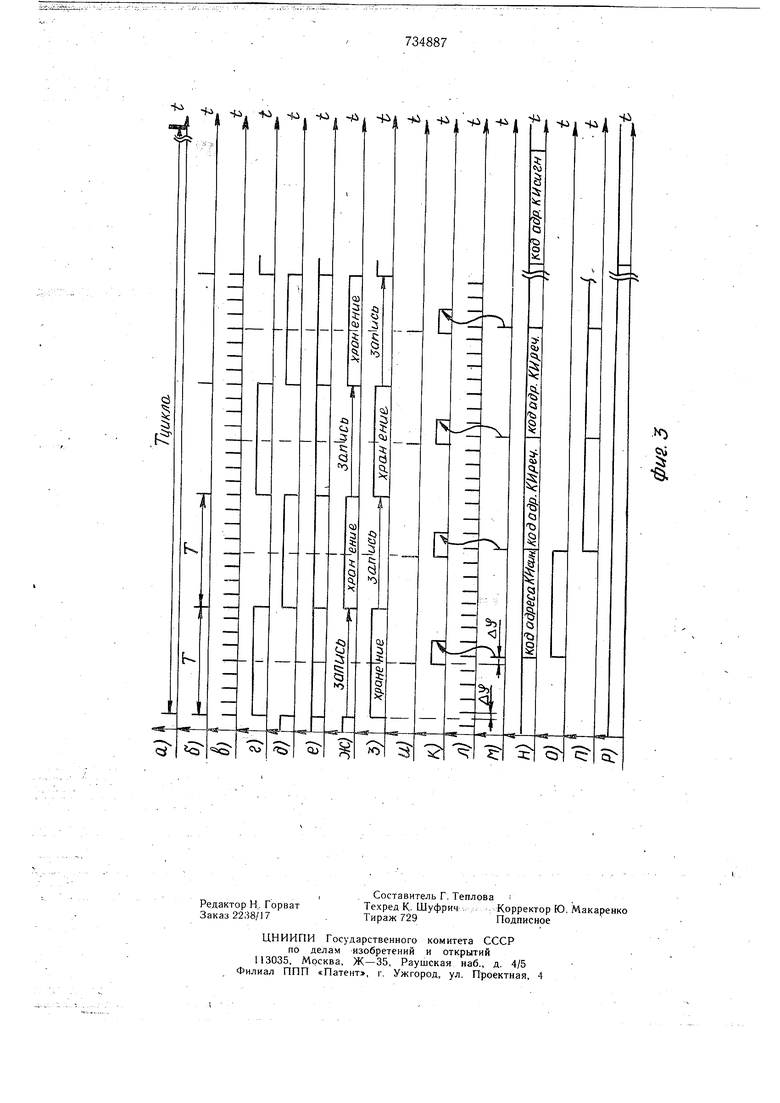

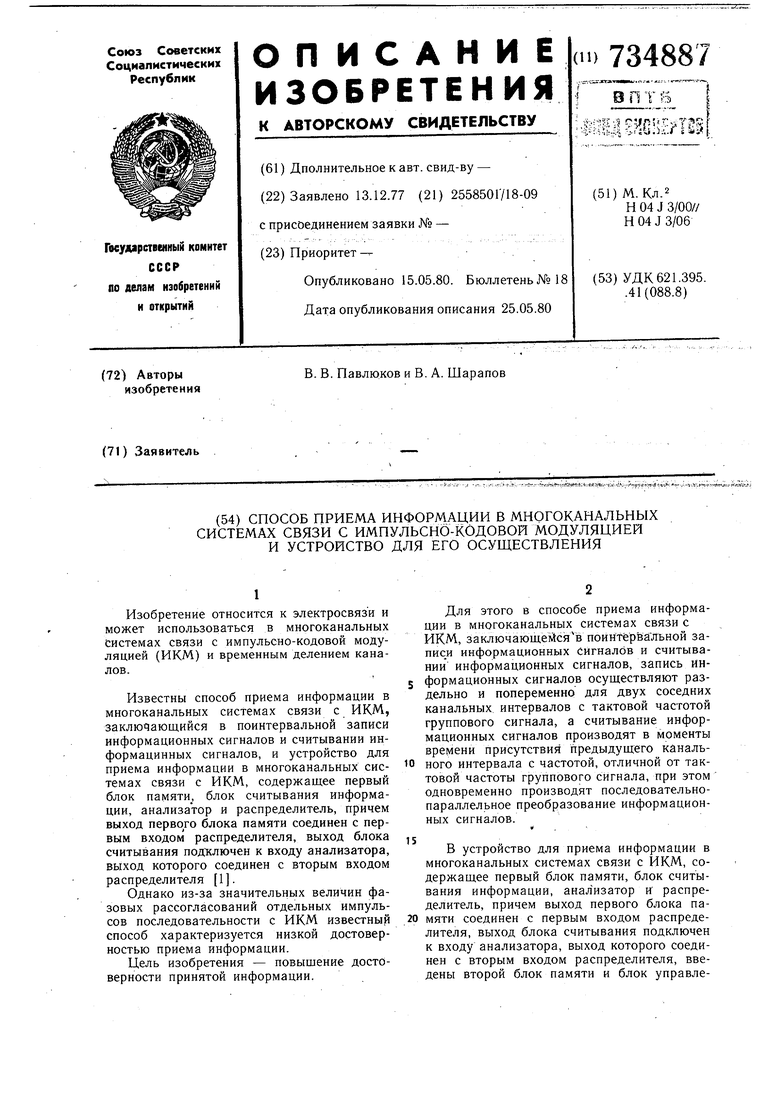

На фиг. 1 приведена структурная электрическая схема устройства, реализующего предложенный способ, на фиг. 2 - структурная электрическая схема блока считывания информации, на фиг. 3 - временные диа граммы функционирования устройства.

Устройство для приема информации в многоканальных системах связи с ИКМ содержит два блока 1, 2 памяти, блок 3 считывания информации, анализатор 4, распределитель 5, блок 6 управления записью и считыванием.

Блок 3 состоит из трех триггеров 7, 8, 9 ри этом первый вход 10 второго триггера является входом блока 3, % вйхЬд третьего риггера 9 является выходом блока 3.

Устройство работает следующим образом На входы блока управления б поступают мпульсные посылки цикловой синхрЪнизаии Тракта, определя бщие начало каждого икла ИКМ с фазовым рассогласованием Д 9 относительно частоты центра (фиг. За) импульсные посылки поканальной (понтервальной) синхронизации тракта, определяющие начало каждого канального интер вала цикла ИКМ с идентичным фазовым рассогласованием Дф (фиг. 36). На первый вход блока памяти I поступает импульсная последовательность тактовой частоты (так5 товые импульсы) тракта с ИКМ, сопровождающая последовательность информационных сигналов (посылок) данного тракта, с двунаправленным фазовым рассогласованием Аф относительно ; импульсных посылок тактовой частоты центра (фиг. Зв). Стан дартная; длительность.канального интервала цикла ИКМ, равная восьми интервалам тактовой частоты, или восьми битовым позициям, обозначена через Т. Попеременную запись информации четных-нечетных канальj ных интервалов производят при помощи блока 6 управления. На основе поступающих на его входы импуль гных последовательностей цикловой синхронизации, поканальной синхронизации и тактовой частоты тракта на первом выходе блока управления 6 фор0 мируется сигнал разрещения записи информации нечетных канальных интервалов цикла длительностью Т (фиг. Зг). Этот сигнал с первого выхода блока управления 6 поступает на управляющий вход блока памяти Г, JJ обеспечивая запись в него информации соответствующих канальных интервалов цикла ИКМ. На втором выходе блока управления 6 формируется сигнал разрещения записи информации соседних (четных) канальных интервалов цикла длительностью Т 0 (фиг. Зд), который поступает на управляющий вход блока памяти 2, обеспечивая запись в него информации четного канального интервала цикла. Таким образом осуществляется управление процессом попеременной записи информации, поступающей на информационные входы блоков памяти 1, 2 (фиг. Зе), определенных канальных интервалов цикла ИКМ. .

При . наличии на управляющем входе блока 1 памяти сигнала разрещения записи 0 информации (фиг. Зг) производится последовательное заполнение, блока 1 памяти последовательностью информационных посылок нечетных канальных интервалов цикла (запись), подаваемой на информационный вход бл.ока 1 памяти (фиг. Зж). По истече .НИИ времени Т с момента начала записи сигнал разрещения на управляющем входе блока 1памяти прекращается, изаписанная информация данного канального интервала хранится в блоке 1 пайяти в течение 0 следующего интервала Т (фиг. Зж), чем обеспечивается возможность неразрущаемого считывания .всех восьми бит информации одновременно, т. е. в параллельной форме, в определенный момент времени Т ее хранения.

В процессе заполнения инфор.мацией бло ка 1 памяти сигнал разрещения записи И1|формации на управляющем входе блока 2 памяти отсутствует (фиг. Зд), вследствие

чего последний находится в режиме хранения и возможного неразрушаемого считывания с него в параллельной форме, т. е. всех восьми бит одновременно, информации предыдущего четного канального интервала цикла (фиг. Зз). При появлении на управляющем входе блока памяти 2 сигнала разрешения записи информации (фиг. Зд) в течение времени Т производится последовательное заполнение блока памяти 2 последовательностью информационных посылок четного канального интервала цикла (запись которую по прекращении действия сигнала разрешения записи хранят далее в блоке 2 памяти в течение времени Т (фиг. Зз), чем также обеспечивают возможность неразрушаемого считьшания информации в параллельной форме с его выхода в определенный момент времени ее хранения.

Считывание одновременно всех восьми бит информации предыдущих канальных интервалов цикла с выходов соответствующих блоков памяти 1, 2 в середине времени хранения информации, равного Т, производится при помощи блока 6 управления и блока 3 с тактовой частотой центра. На основании отсчитывания блоком управления 6 каждых четвертых импульсных посылок последовательности частоты тракта, начиная с момента начала отсчета времени Т, формируется импульсный сигнал разрешения считывания информации каждого канального интервала цикла, при этом сигнал расположен в середине временного промежутка Т (фиг. Зи) На третьем выходе блока управления 6 формируется сигнал разрешения считывания информации в виде потенциала (фиг.Зк) который вырабатывается в момент формирования импульсного сигнала разрешения считывания информации (см. фиг. Зи), а прекращается после момента осуществления считывания информации выходным сигналом считывания информации блоком 3. Потенциал сигнала разрешения считывания подается с третьего вь1хода блока 6 управления на вход 10 блока 3 и осуществляет его однократный запуск. На другой вход блока 3 поступает импульсная последовательность тактовой частоты центра (фиг. 3л). Выходной сигнал блока 3 показан на фиг. 3м. Блок 3 считывания информации с тактовой частотой центра функционирует следующим образом.

При отсутствии потенциала сигнала разрешения считывания информации на входе 10 блока 3 в момент появления.импульсной посылки на другом его входе на выходе триггера 7 формируется положительный сигнал, который не измeняeт состояние выходного триггера 9, а так как при этом на третий вход триггера 9 подается с входа 10 блока 3 отрицательный сигнал, то с выхода триггера 9, являющегося выходом блока 3, снимается положительный сигнал.

Далее появление потенциала сигнала разрешения считывания с рассогласованием Дф менее одного тактового интервала частоты на входе 10 блока 3 и, соответственно, на третьем входе триггера 9 не изменяет 5 состояния выхода триггера 9. При паузе

между импульсными посылками на другом входе блока 3 и наличии потенциала на цтором входе триггера 7 на выходе последнего формируется отрицательный сигнал, но за отрицательного сигнала на втором входе триггера 9 на его выходе по-прежнему вырабатывается положительный сигнал.

И только при наличии потенциала на входе 10 блока 3 и, следовательно, на третьем входе триггера 9 и следующей импульсной

,j посылки тактовой частоты центра на другом входе блока 3 и, соответственно, на втором входе триггера 9 за счет отрицательного сигнала на выходе триггера 7 происходит изменение с6стЪянйя выхода триггера 9 на отрицательное, т. е . начинается формирование на выходе блока 3 сигнала считывания информации, синфазного с тактовой частотой центра. Кроме того, отрицательный сигнал с выхода триггера 9 подается на второй вход триггера 8, вследствие чего

J на его выходе формируется отрицательный сигнал, устанавливающий выход триггера 7 в положительное состояние, которое после окончания данной импульсной посылки в дальнейшем не позволяет изменить состояние триггера 9.

0 По окончании импульсной посылки тактовой частоты центра на третьем входе триггера 9 формируется отрицательный сигнал, устанавливающий его выход в положительное состояние, то есть формирование сигнала считывания информации с на выходе блока 3 на этом заканчивается.

Далее выход триггера 8 остается в том же состоянии до тех пор, пока не прекратится потенциал сигнала разрешения считывания на входе 10 блока 3. После этого

0 триггеры 7, 9, 8 вновь готовы к однократному формированию синфазного, с тактовой частотой центра, сигнала считывания информации в описанно 1 выше последовательности.

Последовательность сформированных на

вь1ходе блока 3 импульсных сигналов считывания информации, синфазных с импульсной последовательностью тактовой частоть центра, подается на вход анализатора 4, с помощью которого вырабатывается код адQ реса канального интервала цикла, которому принадлежит считываемая с выходов блоков памяти 1 или 2 информация (фиг. Зн). Код адреса канального интервала цикла подается с вь1хода анализатора 4 на второй вход распределителя 5 информации. На

первый вход распределителя 5 считывают в параллельной форме информацию с выхода блока 1 памяти, при этом считывание информации на этот вход распределителя 5

(см. фиг. 2ж) производят при условии отсутствия сигнала разрешения записи информации (см. фиг. 2г) на втором входе блока 1 памяти в момент времени, соответствующий половине времени Т хранения информации нечетных канальных интервалов в блоке 1 памяти. Считывание информации в параллельной форме с выхода блока 2 памяти на третий вход распределителя 5 (см. фиг. 2з) производят при условии отсутствия сигнала разрешения записи информации (см. фиг. 2д) на втором входе блока памяти 2, т. е. в течение времени хранения Т в блоке памяти 2 информации четных канальных интервалов.

Как и в случае считывания информации с выхода блока 1 памяти здесь также время хранения информации предыдущего канального, интервала определяют равным Т, а момент считывания хранимой информации выбирают соответствующим половине времени Т хранения информации, или середине канального интервала, равного четырем импульсным посылкам последовательности тактовой частоты (четырем битовым позициям). Таким образом, .вследствие того, что попеременно на первый вход распределителя 5 считывают в параллельной форме информация нечетных канальных интервалов цикла, на третий вход распределителя 5 считывают в параллельной форме информацию четных канальнь1Х интервалов цикла, а на второй вход распределителя 5 в обоих случаях подают код адреса канального интервала, которому принадлежит считываемая информация, формируемый синфазно с импульсной последовательностью тактовой частоты центра в середине времени хранения информации каждого канального интервала цикла, и осуществляют компенсацию двунаправленных фазовых рассогласований между импульсными последовательностями тактовых частот тракта и центра в максимально широких пределах - до четырех тактовых интервалов частоты (битовых позиций) для синхронизируемых сетей связи.

На выходе распределителя 5 формируют информационные посылки определенного канального интервала цикла ИКМ, которые в параллельной форме подаются в различные системы приемного коммутационного центра сети связи в зависимости от функционального назначения информации.

При наличии на втором входе распределителя 5 кода адреса канального интервала синхронизации или кода адреса канальных интервалов речевой информации, или кода адреса канального интервала сигнализации на выходах распределителя 5 соответственно формируется информация синхронизации цикла ИКМ, выдача которой производится в течени времени Т (см. фиг. 2н,о), или речевая информация цикла ИКМ с адресом канального интервала в течение времени Т (см. фиг. Зн, п), или информация сигнализации цикла ИКМ в течение длительности цикла (см. фиг. 3 и , р).

Формула изобретения . Способ приема информации в многоканальных системах связи с импульсно-кодовой модуляцией, заключающийся в поинтервальной записи информационных сигналов и считывании информационных сигна.лов, отличающийся тем, что, с целью по0 выщения достоверности принятой информации, запись информационных сигналов осуществляют раздельно и попеременно дяя двух соседних канальных интервалов с тактовой частотой группового.сигнала, а считывание информационных сигналов произ5водят в моменты времени присутствия пред|з1дущего канального интервала с частотой, отличной от тактовой частоты группового сигнала, при этом одновременно производят последовательно-параллельное преQ образование информационных сигналов.

2.Устройство для приема информации в многоканальных системах связи с импульсно-кодовой модуляцией, для осуществления способа по п. 1, содержащее первый блок памяти, блок считывания информации, анаS лизатор и распределитель, причем выход первого блока памяти соединен с первым входом распределителя, выход блока считывания подключен к входу анализатора, выход которого соединен с вторым входом расJ. пределителя, отличающееся тем, что в.ведены второй блок памяти и блок управления записью и считыванием, при этом информационные входы первого и второго блоков памяти соединены между собой, первый выход блока управления записью и считываJ нием.подключен к управляющему входу первого блока памяти, второй выход блока управления записью и считыванием соединен с управляющим входом второго блока памяти, а третий выход блока управления записью и считыванием подключен к входу

блока считывания информации, причем в.ыход второго блока памяти соединен с третьим входом распределителя.

3.Устройство по п. 2, отличающееся тем, что блок считывания информации состоит из

5 первого, второго и третьего триггеров, причем выход первого триггера подключен к первому входу третьего триггера, второй вход которого соединен с первым входом первого триггера, второй вход которого подключен к первому входу второго и третьему входу третьего триггеров, а второй вход второго триггера соединен с выходом третьего триггера, при этом первый вход второго триггера является входом блока считывания, а выход третьего триггера является

J выходом блока считывания.

Источники информации, принятые во внимание при экспертизе 1. Патент США № 3839599, кл. 179-69.5, опублик. 1976 (прототип).

.i

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| Устройство коммутации с эластичной памятью | 1988 |

|

SU1647921A1 |

| АДАПТИВНЫЙ ЦИФРОВОЙ ГРУППОВОЙ ПРИЕМНИК СИГНАЛОВ УПРАВЛЕНИЯ И ВЗАИМОДЕЙСТВИЯ С НЕЛИНЕЙНОЙ ИМПУЛЬСНО-КОДОВОЙ МОДУЛЯЦИЕЙ (ИКМ) | 1998 |

|

RU2143790C1 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Устройство передачи цифровых сигналов | 1980 |

|

SU919129A1 |

| Устройство для статистического уплотнения линии передачи | 1984 |

|

SU1228292A1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Коммутационное устройство | 1987 |

|

SU1478371A1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| СПОСОБ ВЕДЕНИЯ ДВУХСТОРОННЕЙ ВЫСОКОСКОРОСТНОЙ РАДИОСВЯЗИ С ЭФФЕКТИВНЫМ ИСПОЛЬЗОВАНИЕМ РАДИОЧАСТОТНОГО СПЕКТРА В ВЕДОМСТВЕННОЙ СИСТЕМЕ СВЯЗИ | 2016 |

|

RU2663200C2 |

I

j

Ю оЛ

8

|

U

5

L..r:.

Ф«г.2

Авторы

Даты

1980-05-15—Публикация

1977-12-13—Подача