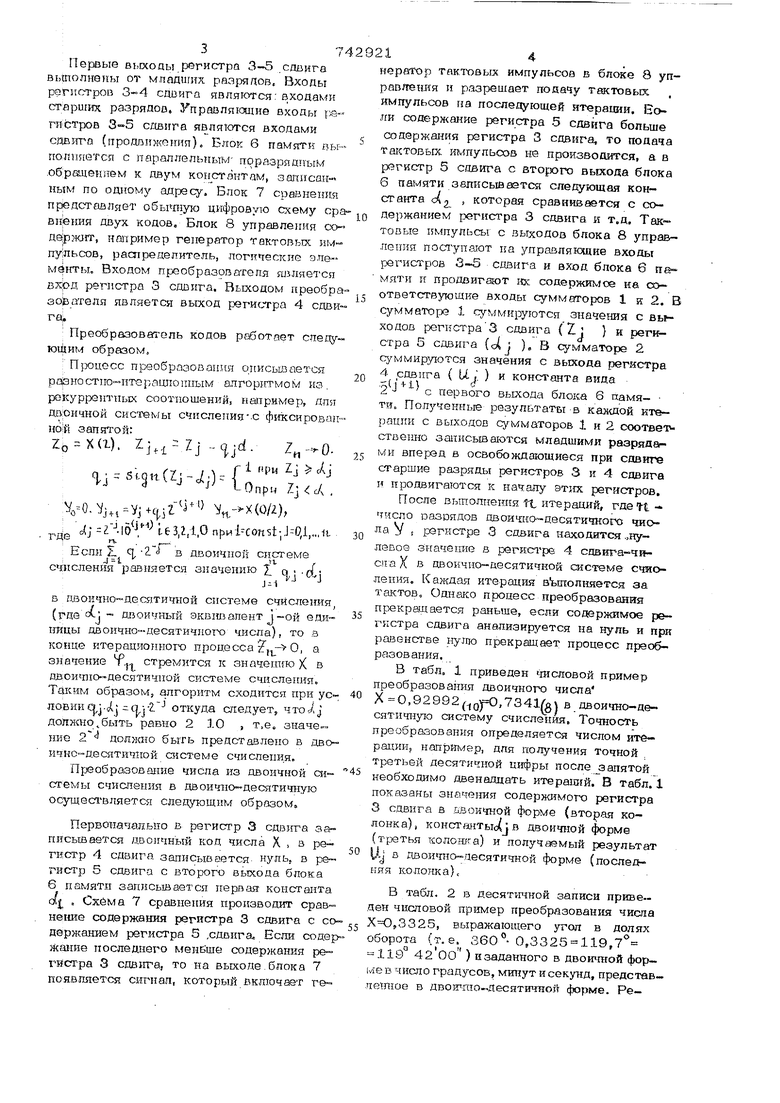

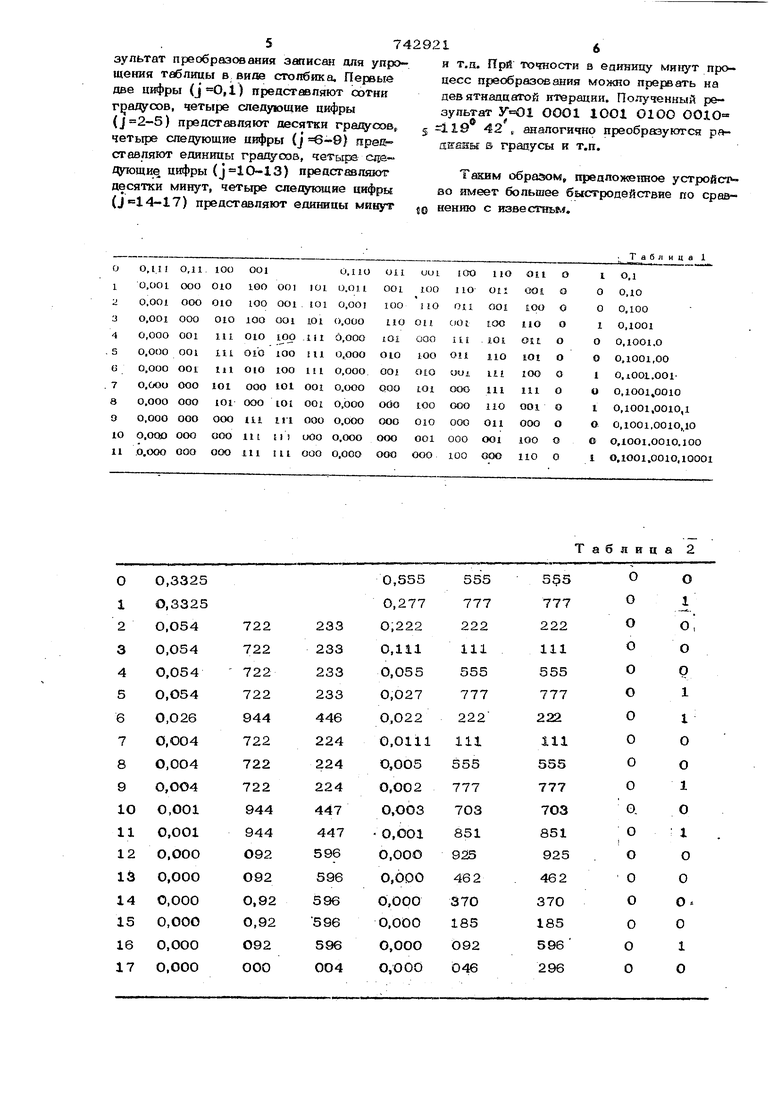

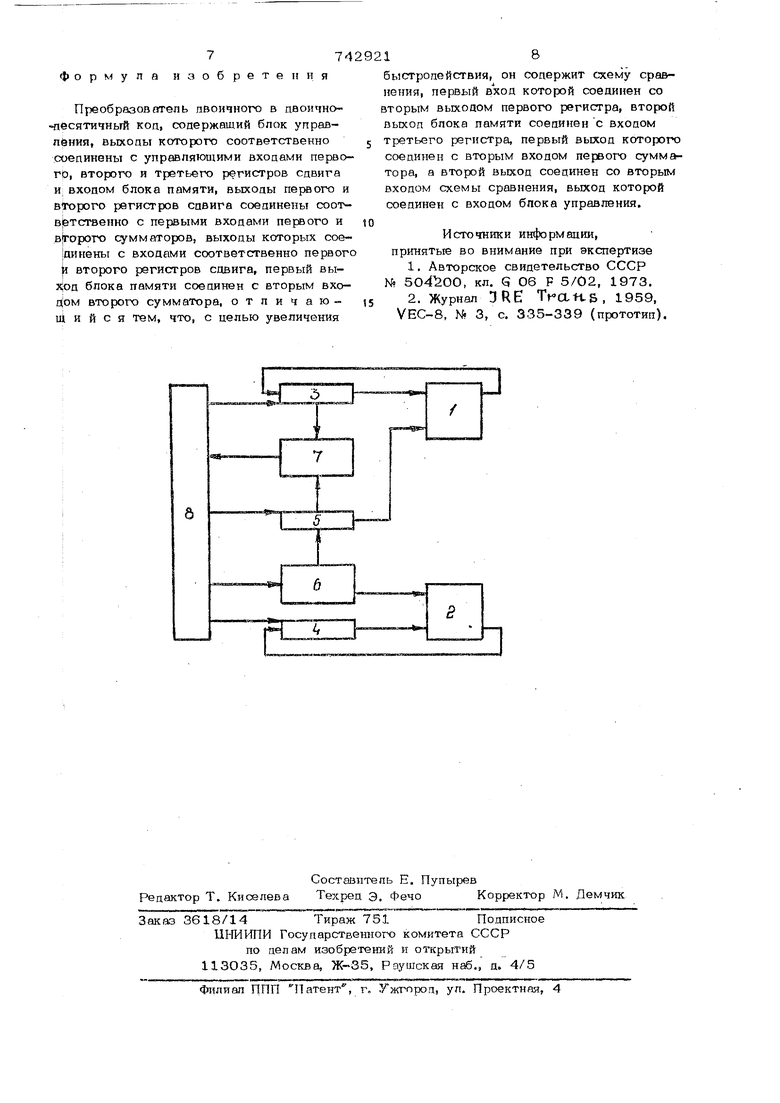

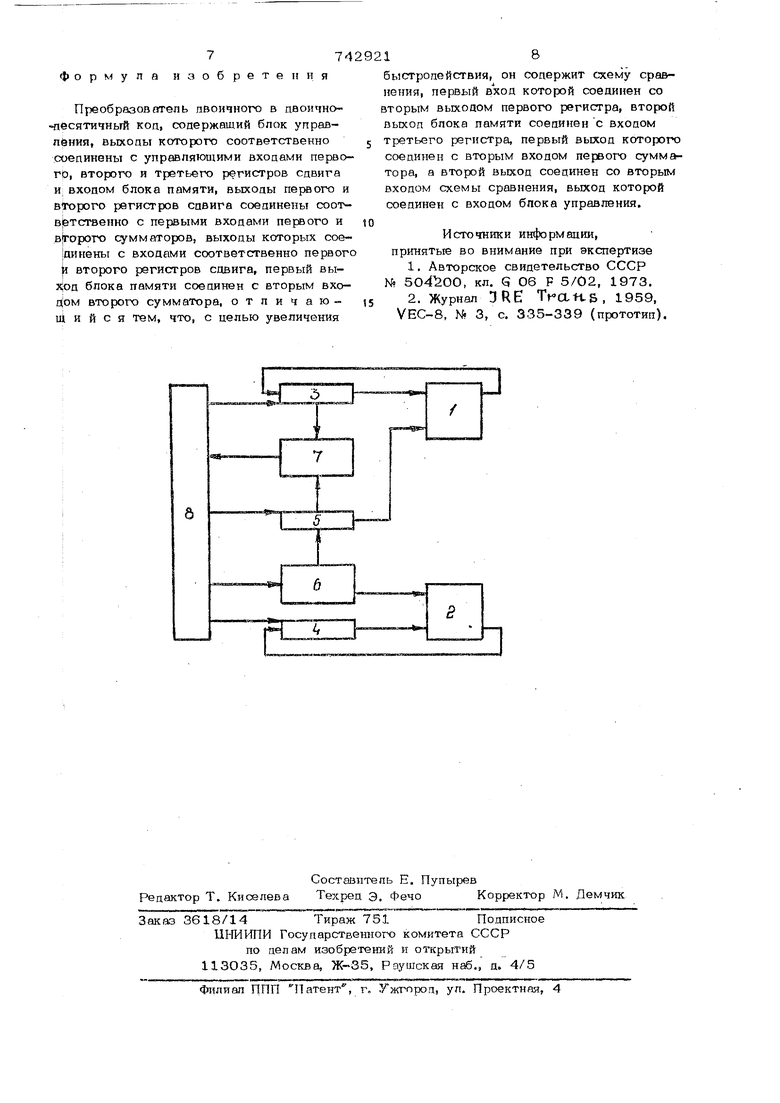

Изобретение относится к цифровой вычислительной технике и быть использовано для аппаратной реализации опе рации преобразования чисел, в том числе и угловых значений, из двоичной системы счисления в двоично-десятичную. Известен преобразовеггепь кодов, содержащий регистры, блок управления, лог№ ческие элементы .ll Недостатком его является низкое быст родействие. Наиболее близким -техническим решением к изобретению йвляется преобразова тель двоичнотх в двоично-десятичный код, содержащий блок управления, выходы которого соответственно соединены с управляющими входами первого, второго и третьего регистров сдвига и входом блока памяти, выходы первого и второго регистров сдвига соединены соответственно с первыми входами первого и второго сумматоров, выходы которых соединены с входами соответственно первого и второго регистров сдвига, первый выход блока памяти соединен с вторым входом второго сумматора 21 . Преобразователь кодов содержит также сумматор-вычитатель. Недостатком его является низкое быст родействие. Цель изобретения - увеличение быстродействия .преобразователя кодов. Цель достигается тем, что он содержит схему сравнения, первый вход которой со- единен со вторым выходом первого регистрра, второй выход блока памяти соединен с входом третьего регистра, первый выход которого соегданен с вторым входом первого сумматора, а второй выход соединен со вторым входом схемы сравнения, выход которой соединен с входом блока улравления. На чертеже схематически изображен преобразователь двоичного в двоично-десятичный код. Устройство содержит сумматор 1 к 2, регистр 3-5 сдвига, блок 6 памяти, схему 7 сравнения, блок 8 управления. Первые вьссоды регистра 3-5 .сдБига выполнены от мпадигнх разрядов. Входы рог С-тров 3-°4 сдоигга являются: входами старших рэзряяоо. Управляющие входы г rjfCTpoB сгшнга являются входами сдвгггя (проддпжеиип). Блок 6 памяти вьгполяпется с параплепьт1ым- порйэряапъгм .сбрещекнем к. двум кон стантам, записан- ным по ошгому адресу. Блок 7 сравнента представляет обытаую цифровую схему ера вфкия двух кодов. Блок 8 управления содфж1 Т, например ге юратор тактовых импу;льсов, распределитель, логические элементы. Входом преобразователя является вхрд регистра 3 сдвига. Выходом преобра зователя является выход регистра 4 сдвига;, Преобразователь кодов р ответ следующим образом, Пртцосс преобразования описьшаеч-ся роэностпо-итерашюипым алгоргггмом из, рокур{эеитпых соотношений, например, для дооичной системы счисления .с фиксированноЩ запятой: Zo-X(l). Zj. . Z.0. f-, , Г -РИ J ,-s.3nCZj-)f,/./ ,,-у;.( (o/2), j.j гЧю-, 1ез,г,1.о npHl4onst;J--o,i,.,,it Еспн Е. Я, 2- двоичной системе счисления равняется значению 2 п . .(j,J-1в шбоично-дссятичной снстеме счисления, (где ™ плоичный 9кв1юалент J-ой единицы двоично-десятичнотч) числа), то з конце итерационного процесса ij,- О, а З1гачение Т., стремится к значентгю )( в ввои«п1О™десятиЧ Юй снстеме счисления. Таким образом, алгоритм сходится нри условии q,j.c(j-(j-Z- откуда следует, что, должно,быть равно 2 10 , т.е. значе-лие 2 должно быть представлено в даоично-десятичной системе счисления. Преобразование числа из двоичной си- сгемы счисления в двоично-десятичную осущес1вляется следующим образом Первоиачаяьпо в регистр 3 сдвига за письшее7ся двоичный код числа X , в регистр 4 сдвига записывается нуль, в регистр 5 сдвига с второг-о выхода блока 6 памяти записывается пергкая- константа с , Схема 7 сравнения нроизводит сравнегше содержания регистра 3 сдвига с со держанием регистра 5 ,сдвига. Если соде 5кгшие последнего к ен6ше содержания регистра 3 сдвига, то на выходе, блок а 7 появляется сигнал, который включат ге 4 14 ератор тактовьи импульсов в блоке 8 упавяе шя и разрешает подачу тактовых мпульсов гш последующей итерации. Вои со/к-ржшше регистра 5 сдвига больше содержания регистра 3 сдвига, то подача Tai-стоБьгх етлпупьсов не производится, а в регистр 5 сдвига с второго выхода блока б памяти зеписываэтся следующая константа , которая сравнивается с содержанием регистра 3 сдвига и т.д. Так тойые импульсы с выходов блока 8 управ- лепия поступают на управляющие входы регистров 3--S сдвига и вход блока 6 памяти к продвигает IK coдepжи oe на соответствующие входы сумматоров 1 к 2. В сумматоре 1 суммируются значе{шя с вьгходов регистра3 сдвига ( Z : } и регистра 5 сдвига (с( ; ). В сумматоре 2 суммируются значения с выхода регистра 4 сдвига ( Ц , ) и константа вида 2J с первого выхода блока 6 памя- ти. Полученные результаты в каждой итерации с выходов сумматоров 1 и 2 соответ ственно занисьшаются младшими разряявгми вперед в освобождающиеся при сдвиге старшие разряды регистров 3 и 4 сдвига и продвигаются к начачу этих регистров, После выполнения tL итераций, где Н тиспо оаврядов двоично-десятичного чиола У , регистре 3 сдвига находится .,нулевое значегою в регистре 4 сдвига-чиc ia X в двоично-десятичной системе счиоления. Каждая итерация в шолняется за тактов. Однако процесс преобразования прекращается раньше, если содержимое регистра сдвига анализируется на нуль и при равенстве нугао прекращает процесс праоб разования. В табл. 1 приведен тасловой пример преобразования двоичного числа ,92992 Q, в двоично-десятичную систему счисления. Точность преобразования определяется числом итерации, например, для получения точной третьей десятичной цифры после запятой необходимо двенадцать итерашгй. В табл. 1 показаны значения содержимого регистра 3сдвига в .овоичной форме (вторая колонка), конста«тый(1 в двоичной форме (третья колошга) и получогмый результат |J.j в двоично-десятичной форме (последняя в:олонка). В табл. 2 в десятичной записи приведен числовой пример преобразования числа ,,3325, выражающего угол в оборота (т.е. 360 0,3325 119,7 119 42 00 ) пзаданного в фор- i-ле в число градусов, минут и секунд, представ.летюе в двокппю-десятичной форме. Ре.зультат преобразования записан для упрощения таблицы в. виле столбика. Первые две цифры (j О, 1) представпяют сотни Г1эадусов, четыре следующие цифры () представляют десятки градусов четыре следующие (J 6-9) fipeffiставляют единицы градус в, четыре еде- /дующие цифры (J 1O-13) преаставлдаот десятки минут, четыре спеаующяе цифры (J 14-17) представляют единицы минут

я т.н. При точности в единицу минут процесс преобразования можно прервать на девятнадцатой ит ерации. Полученный результат УО1 ООО1 1ОО1 О1ОО О010« 119 42 , аналогично преобразуются радгганы в градусы и т.п.

Таким образом, предложенное устройсво имеет большее быстродействие по сравнению с известньм.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный код | 1977 |

|

SU664167A1 |

| Преобразователь двоичного кода в двоично-десятичный (двоичнодесятично-шестидесятичный) код | 1976 |

|

SU616627A1 |

| Вычислительное устройство | 1988 |

|

SU1508208A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1978 |

|

SU742924A1 |

| Преобразователь двоично-десятичногоКОдА B дВОичНый КОд | 1979 |

|

SU809151A1 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОЙ ДРОБИ В ДВОИЧНУЮ ДРОБЬ | 1979 |

|

SU826335A1 |

| Преобразователь двоично-десятичных чисел в двоичные | 1981 |

|

SU1003068A1 |

| Устройство для преобразования двоичных чисел в двоично-десятичные и обратно | 1983 |

|

SU1142826A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Преобразователь двоичного кода | 1984 |

|

SU1208607A1 |

Таблица 1

формула изобретения

Преобразов отель пвоичного в пвоично-пёсятичный коП| сопержащий блок управления, выходы которого соответственно соепинены с управляющими вхоцами первого, второго и третьего регистров сдвига и вхопом блока памяти, выходы первого и в горого регистров спвига соединены соотBieTCTBenHO с первыми входами первого и BJroporo сумматоров, выходы которых сое цииены с входами соответственно первог ц второго регистров сдвига, первый выКоа блока памяти соединен с вторым входом второго сумматора, отличаюuj и и с я тем, что, с целью увеличения

быстродействия, он содержит схему сравнения, первый вход которой соединен со вторым выходом первого регистра, второй выхоп блока памяти соединен с входом третьего регистра, первый выход которого соединен с вторым входом первого сумматора, а второй выход соединен со вторым входом схемы сравнения, выход которой соединен с входом блока управления.

Источники информации, принятые во внимание при экспертизе

1,Авторское свидетельство СССР № , кл. Q 06 F 5/02, 1973.

Авторы

Даты

1980-06-25—Публикация

1977-12-12—Подача