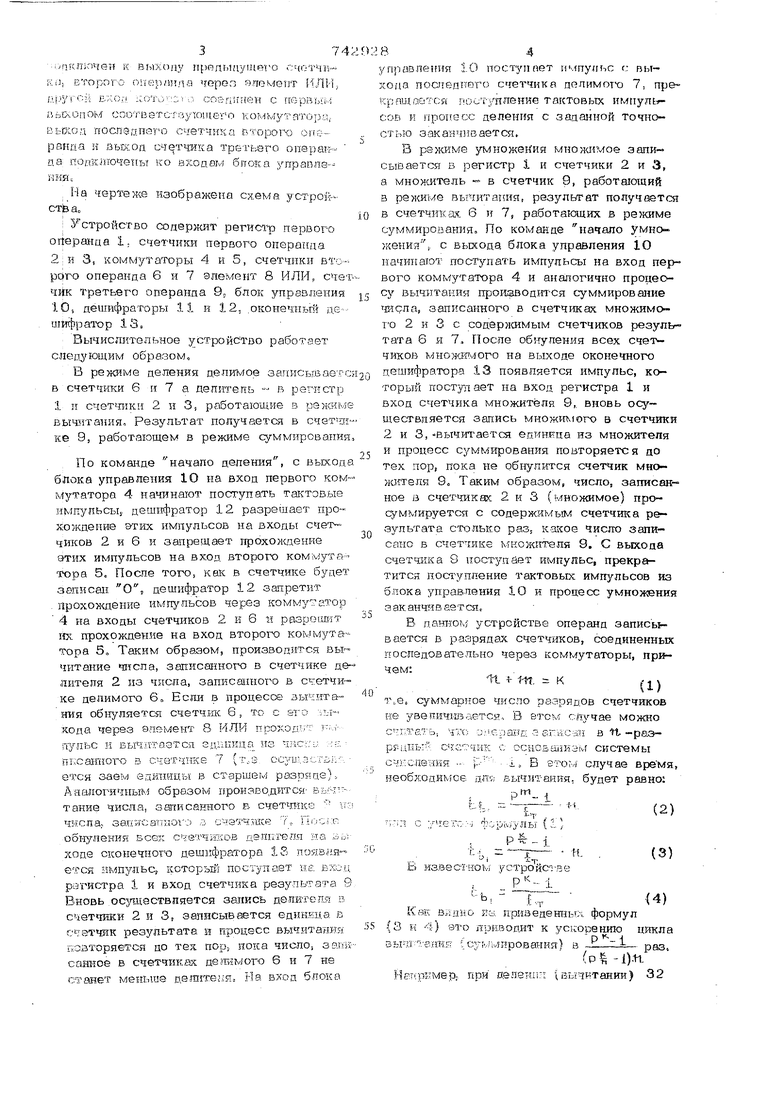

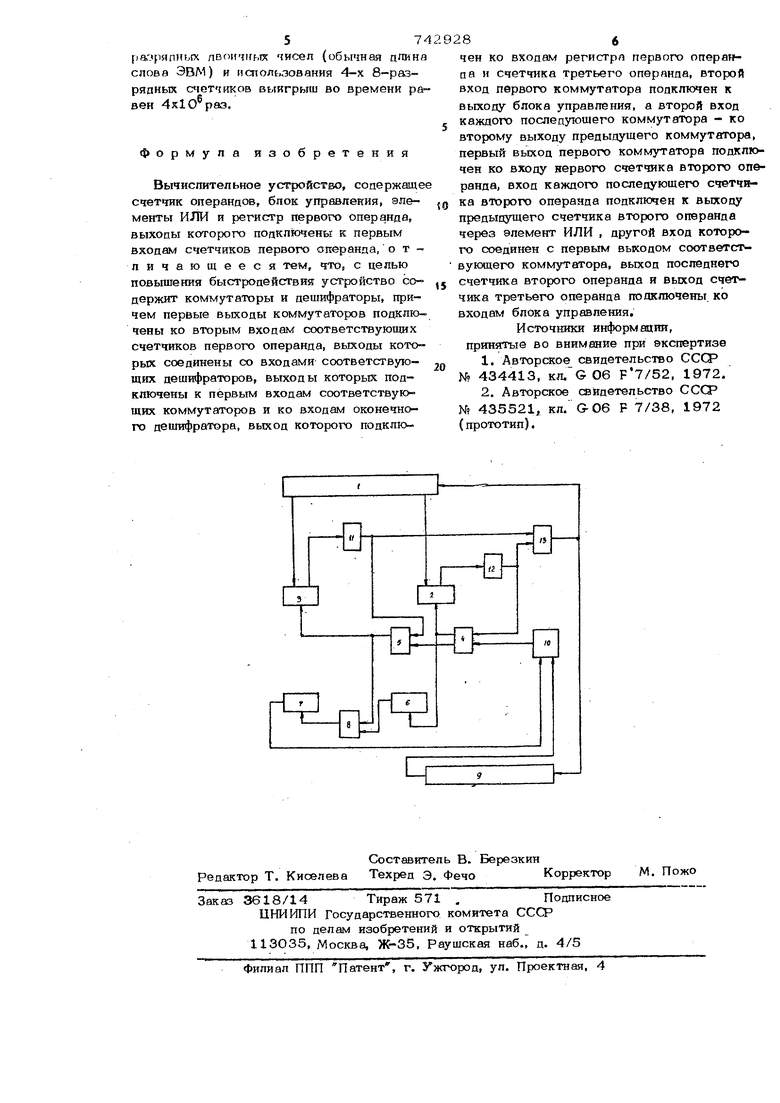

Изобретение относится к области Bbtчислительной техники и может,быть испол зовано, в частности в измерительных приборах дискретного типа, и автоматизированных устройствах обработки числовой информации. Известно вычислительное устройство, содержащее счетчики операндов, схемы ввода, устройство управления. Процесс вы числения в этом устройстве представляет собой последовательности циклов вычитания (сложения) операндов 1} . Недостарком известного устройства является низкое быстродействие. Наиболее близким по технической сущности является вычислительное устройство, содержащее счетчик операндов, блок управления, элементы ИЛИ и регистр пер вого операнда выходы-которого ПОДКЛЮЧ&ны к первым входам счетчиков первого операнда. Известное устройство содержит такие элементы И и делитель числа поопадоветельных импульсов 2j . Недостатком такого устройства является низкое быстродействие. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что устройство содержит коммутаторы и дешифраторы, причем первые выходы коммутаторов подключены ко вторым входам соответствующих счетчиков первого операнда, выходы которых соединены со входами соответствующих дешифраторов, аыходы которых подключены к первым входа л соответствующих коммутаторов и ко входам оконечного дешифратора, выход которого подключен ко входам регистра первого операнда и счетчика третьего операнда, второй вход первого коммутатора подключен к выходу блока управления, а второй вход каждого последующего коммутатора - ко второму выходу предыдущего коммутатора, первый выход первого коммутатора подключен ко входу первотхз счетчика второго операнда, вход каждого последующего счетчика второго операнда 37 4 onTaii-пчен к выхопу ирепыцушего счотчккп; второго оперллла «ломент 1ЛИ, Е.;-:оа ;;оЮ ::.- ,i со&пипен с первьи-; аькопом соотвстстауощего комыутатоЭ;.к BfcDtoa поспеппаго счетчика второго операнпа н йыход счетчика третьего операкпа попкнючеяы ко аходак бпока упраппе-i-iifflt , I-ia чертеже каображепа схема устройства. : Устройство содержит pernaip первого oriepaHaa 1. счет-чики первого операнда 2; и 3, комк-(утаторы 4 и 5, счетчики второго операнда 6 и 7 элемент 8 ИЛИ, сче чик третьего операнда 9„ блок управления lOi дешифраторы 11 и 3.2, .оконечный де шифраахзр 13, Вычислительное устройство работает слеи ующим образом, В режиме деления делимое записываетс Б счетчики 6 и 7 а депгггепь -- в регистр 1 п счетчики 2 и 3, работающие в резюм вычз ггаэшя. Результат получается в ке 9, работающем в режиме суммирования По команде начало деления, с выход блока управления 10 на вход первого ком мутатора 4 начинают поступать тактовые имяупьсы дешифратор 12 разрешает прохождение э-тих импульсов на входы счетчиков 2 и 6 и запрещает прохождение этих импульсов на вход второго коммута -jpopa 5. После того, как в счетчике будет записан О, дешифратор 12 запретит , прохождение импульсов через коммутатор 4 на входы счетчиков 2 и 6 н разресшлт их прохождение на вход второго коммутатора 5. Таким образом, производится вычитание числа, записанного в счетчике де лителя 2 из числа, записанного в сс:етчи ке делимого 6, Если в процессе зычитання обнуляется счетчгяс 6, то с лугхода через элемент 8 ИЛИ прохоптгг т- ;пульс и вычитается эцппица из iHcr;;; г- nncainsor-o в с гетчнке 7 (т.,з осуи,лст -;:-. ется заем единицы в старшегч.) разряце). Аналогичным образом производится- .вь:-г такие числа, затисаетюго в счетЩ1ке - т чяспа, aaiiHcaviHoro л с-гатчшсе f, Иггспл обнуления всех счетчжков делпгепя на з ходе оконечного дешифратора IS появаяется импульср который поступает не. вхоц р-этистра 1 и вход счетчика результата 9 Вновь осуществпяется запись делитспя в счетчЕКИ 2 и 3, записывигтся единица в счетчик результата и процесс вычитания коаторяется по тех пор. пока числО; закк санкое в счетчикгя деш-тыого 6 и 7 не станет меньше депитеая. На вхоп блока 84 правления iO поступает г)мпульс с выода посгтепггего счетчика делимотх) 7, пре рдадгются поступление тактовых импульсов к процесс деления с заданной точностью заканчивается. В режиме умножения множимое записывается в регистр i и счетчики 2 и 3, а множлтель - в счетчик 9, работшощий 3 режиме (ия, результат получсется в счетчикак; 6 и 7, работающих в режиме суммирования. По команде начало умножения,, с Выхода блока управления 1О начинают поступать импульсы на вход первого коммутатора 4 и аналогично процессу вычитания производится суммирование йсла, записанного в счетчиках мнондамото 2 и 3 с соаврлшмым счетчиков результата 6 я 7. После обнуления всех счетчиков множлмого на выходе оконечного дешифратора 13 появляется импульс, который TiOCTyri ает на вход регистра 1 и вход счетчика множителя 9,. вновь осуществляется запись множимого в счетчики 2 и 3, -вычитается одиняца из мнонштеля и процесс суммирования повторяется цо тех пор, пока не обнупится счетчик мно- жи-теля 9« Таким образом, число, записанное в счетшках: 2 и 3 (множимое) просуммируется с содержимьаи счетчшса результата Сголько раз, к-акое число записано в счетчике множителя 9. С выхопа счетчика 9 импульс, прекрг тится пос1-уппение тактовых импульсов из блока управления 10 и процесс умножения заканчивается, В- паяном устройстве операнд записывается в разрядах счетчиков, соединеннык последовательно через коглмутаторы, причем:tl - ftt. : Кц ч т.е суммарное число разрядов счетчиков не увепичшзается, В этом спучае можно с-ГлТЕТь, 41X5 o ifipavTc а ЕГйсаг в tt -раэР цнь:- счетчик с сснсашшэкГ системы счЕспения - j;-- i В этом случае время, необходимее дЛ;; вычитания, будет равно: 1 ф.) I i / извесг-ноы устройс :-бе . . i-;- (4) к8К Вйпно |;а приведенньтх формул (3 к 4) это приводит к ускорению цикла зыш :ени;::- t суьгыирования) в Н-гА pgg. ().H HaripKiviepf при 0йлен1Г; вычитании) 32 57 ра.ряпиьгх лвонпгьп чисел (обычная плин слова ЭВМ) и использования 4-х 8-разряпных счетчиков выигрыш во времени р вен 4x10 раз. формула изобретения Вычислительное устройство, сопержащ счетчяк операндов, блок управления, элементы ИЛИ и регистр первого операнда, выхопы которого подключены к первым входам счетчиков первого операнда, отличающееся тем, что, с целью повьпиения быстродействия устройство содержит коммутаторы и дешифраторы, причем первые выходы коммутаторов подклю чены ко вторым входам соответствующих счетчиков первого операнда, выходы которьк соединены со входами соответствующих дешифраторов, выходы которых подключены к первым входам соответствующих коммутаторов и ко входам оконечного дешифратора, выход которого подклю8чей ко входам регистра первого операн па и счетчика третьего операнда, второй вход первого коммутатора подключен к выходу блока управления, а второй вход каждого последующего коммутатора - ко второму выходу предыдущего коммутатора, первый выход первого коммутатора подклкучен ко входу первого счетчика второго операнда, вход каждого последующего счетчика второго операнда подключен к выходу предыдущего счетчика второго операнда через элемент ИЛИ , другой вход которого соединен с первым вькодом соответствующего коммутатора, выход последнего счетчика второго операнда и выход счетчика третьего операнда подключены, ко входам блока управления. Источники информации, принятые во внимшие при экспертизе 1.Авторское свидетельство СССР № 434413, кп.&06 F7/52, 1972. 2.Авторское свидетельство СССР № 435521, кл. G-06 F 7/38, 1972 (прототип),

| название | год | авторы | номер документа |

|---|---|---|---|

| ЭЛЕКТРОННАЯ КЛАВИШНАЯ ВЫЧИСЛИТЕЛЬНАЯ МАШИНА | 1973 |

|

SU395837A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения | 1975 |

|

SU640292A1 |

| Устройство для вычисления функций | 1990 |

|

SU1709304A1 |

| Число-импульсное арифметическое устройство | 1980 |

|

SU951303A1 |

| Вычислительное устройство | 1978 |

|

SU742930A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

Авторы

Даты

1980-06-25—Публикация

1976-03-03—Подача