Поставленная цель достигается тем, что в цифровое множительно-делительное устройство дополнительно введены ячейки памяти, блоки вычитания, семь групп элементов И, регистр сдвига, элемент ИЛИ, блок суммирования, причем выходы блоков вычитания с перйого по пятый соединены со входами соответствующих ячеек памяти, выходы которых соединена со входами вычитаемого блоков i вычитания, а входы уменьшаемого С , первого по четвертый блоков вычитания являются входами устройства. Входы уменьшаемого пятого блока вычит ния соединены с выходами блока суммирования, первая группа входов котЬрого .соединена с выходом второго Ьчетчика импульсов, вторая группа входов - с выходами четвертого вычитания, а третья группа входов с выходами пятой ячейки памят{и и входами уменьшаемого шестого блс(ка вычитания, входы вычитаемого которого соединены с выходами четвертой ячейки памяти, выходы первого,: второго и третьего блоков вычитайия соединены соответственно через элементы И первой, четвертой и Цестой группы со входами регистра со{4ножителя, выходы первой ячейки пайяти, шестого блока вычитания, вхс|ды уменьшаемого второго блока вычитания соединены соответственно элементы И второй, третьей и седьмой групп соединены с первой гpJ|ппoй входов двухканального преобразователя код-частота, вторая группа входов которого соединена через пяфую группу элементов И со входами уменьшаемого третьего блока вычитаний, первый выход регистра сдвига соединен с управляющими входами первого и третьего элементов И и с первым входом элемента ИЛИ, второй выход - с управляющими входами элементов И второй и четвертой групп и со вторым входом элемента ИЛИ, а третий выход с управляющими входами элементов И шестой и седьмой групп и третьим входом элемента ИЛИ, выход которого соединен с управляющими входами элементов И пятой группы, выход схемы сравнения подключен к управляющему входу регистра сдвига.

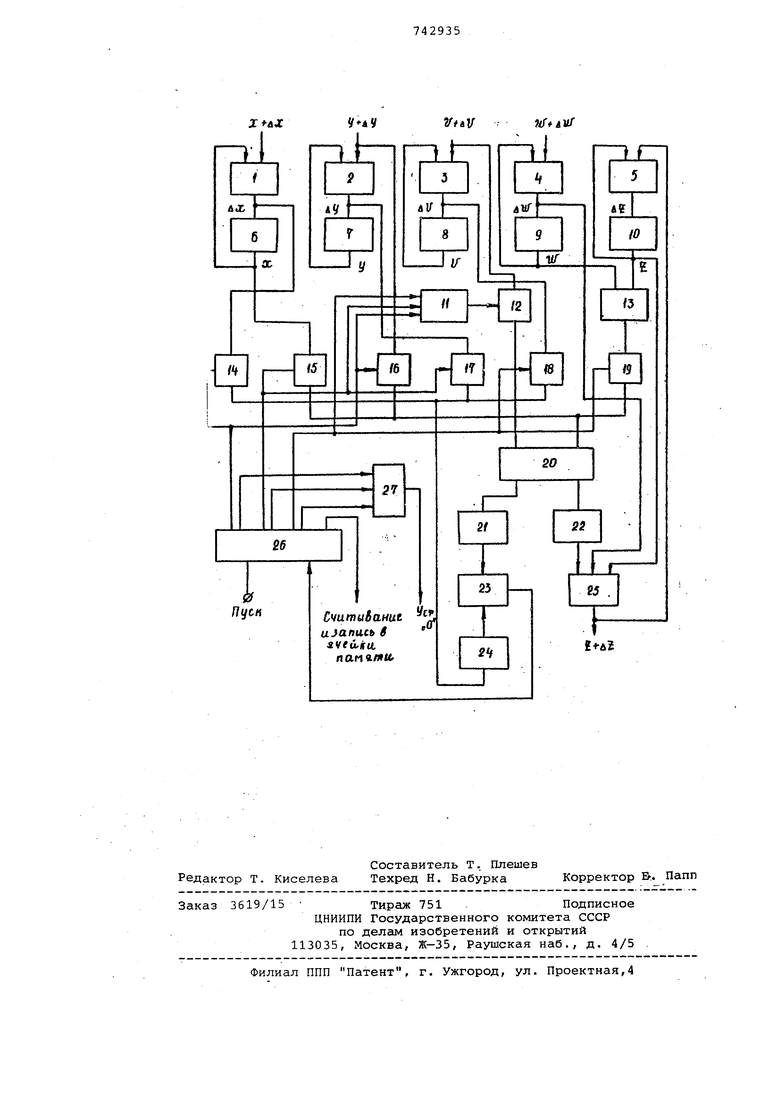

На чертеже представлена блок-схема цифрового множительно-делительного устройства.

Устройство содержит блоки 1-5. вычитания и ячейки 6-10 памяти, служайие для запоминания входных величин и их приращений, причем выход ячеек памяти соединены со входами блоков вычитания, элемент 11 ИЛИ и элемент 12 и пятой группы, блок 13 вычитания, ко входам которого поключены выходы ячеек памяти 9 и 10, элементы 14-19 И первой, второй, третьей и четвертой, шестой и седьм

групп,двухканальный преобразователь 20 код-частота, служащий для преобразования двух кодов в две частоты, к одному из входов которого через элементы 15, 16 и 19 И совтветственно подключен выход ячейки 6 памяти вход .блока 13 вычитания и выход блока 13 вычитания, а ко второму входу - вход блока 3 вычитания через элемент 12 И; два счетчика 21 и 22 импульсов, входы которых соединены с выходами преобразователя 20, схему 23 сравнения, определяющую равенство кодов, регистр 24 сомножителя для хранения одного из сомножителей, причем выход счетчика импульсов 21 соединен со входом схемы 23 сравнения, со вторым входом которой соединен выход регистра 24,вход регистра 24 соединен с выходами блоков 1-3 вычитания через элементы 14, 17 и 18 И соответственно, блок

25суммирования, ко входу которого подсоединен выход счетчика 22 импульсов, а выход его является выходом устройства и он же соединен со входом блока 5 вычитания, регистр 26 сдвига, служащий для управления функционированием устройства: элемент 27 ИЛИ, причем вход регистра

26сдвига соединен с выходом схемы 23 сравнения, а выходы - с управляющими входами элементов 12, 14-19 И и со входами элемента 27 ИЛИ.

Устройство осуществляет множительно-делительную операцию вида с использованием принципа слежения эа изменением входных величин, т.е. устройство производит вычислительные операции не с самими входными величинами, а с их приращениями.

Алгоритм функционирования устройства определен при помоци вычисления для приведенного выше выражения конечноразностного уравнения вида:

j-Vj jу.NW-Z

,,

rriv

где , V+A.V

- текущие значения входных величин; - прсдьщущиё

X , W , z значения входных величин jsz , АХ , лу , fiiV , aW , - приращения

входных величин .

Реализация данного выражения производится с помощью трех доразверток осуществляемых последовательно по величинам лх, лу идУ.

Величины х+д.х,у+гху, V+aV, , являющиеся текущими входными величинами, поступают на входы блоков 1-5 вычитания на вторые входы которых поступают предыдущие значения входны величин, записанные ранее в ячейки 6-10 памяти. Таким образом, на выходах блоков 1-5 вычитания образуются приращения входных величин , лу, CkV, . Выходы ячеёй 9 и 10 памяти подключены к блоку 13 вычитания, на выходе которого образуется разность W-Z. Множительно-делительная операция осуществляется за 4 такта. В первом такте сигнал с первого потенциального выхода регистра 26 сдвига пост пает на управляющие входы элементов 14 и 16 И и через элемент 11 ИЛИ на управлягаций.вход элемента 12 И и от крывает их. Одновременно с первого импульсного регистра 26 сдвига через элемент 27 ИЛИ формируется сигнал на установку счетчиков 21 и 22 в нулевое положение. Таким образом, через элемент 16 И на один из входо преобразователя 20 поступает сигнал V+uV со входа блока 2 вычитания.На второе вход преобразователя 20 поступает сигнал у+ду со входа блок 3 вычитания через элемент 12 И. Сче чик 21 заполняется импульсами, пост пающими с одного из выходов преобра зователя 20 с частотой f K()j. К - коэффициент пропорционал ности; V+4kV - код числа, поступающий на один из входов преобразователя 20. Одновременно счетчик 22 заполняется импульсами, поступаквдими со. вто рого выхода преобразователя 20 с час тотой, , ч fj К (У+Л.У) , где у+лу - код числа, поступающий на второй вход преобразователя 20. Как только число, накопленное счетчиком 21, станет равным числу АХ, хранящемуся в регистре 24, схем 23 равнозначности формирует импульс который установит регистр 26 сдвига в следующее положение. Это вызывает закрывание элементов 14 и 16 И и закрывание элемента 12 И на период переключения. Время &, в течение которого записывалась информация в счетчики, опр деляется выражением -е- , Л-JS -КСМ- лМ) . По истечении этого времени счетчик 22 зафиксирует число N --C--M.-.) -, .)Т.е. первое слагаемое в выражении алгоритма вычислений. Это слагаемое в блоке 25 суммирования суммируется с величиной ikW и величиной z, поступающими в блок суммирования в начале функционирования. При установке регистра 26 сдвига во второе положение со второго импульсного выхода регистра сдвига через элемент 27 ИЛИ формируется импульс на установку счетчиков 21 и 22 в нулевое положение. Со второго потенциального выхода регистра 26 сдвига сигнал поступает на управляющие входы элементов 15 и 17 И, а через элемент 11 ИЛИ - на управляющий вход элемента 12 И и открывает их. Через элемент 15 И на один из входов преобразователя 20 поступает величина х с выхода ячейки 6 памяти , через элемент.17 И в регистр 24 поступа т величина лу, на второй вход преобразователя 20 поступает величина V+iV через элемент 12 И. В устройстве происходят процессы, аналогичные описанным выше, и на выходе счетчика 22 форми&) руется второе слагаемое N,j.- которое суммируется с числом, уже имеющимся в блоке суммирования 25. В третьем такте открываются элементы 12, 18 и 19 И, на один вход преобразователя 20 поступает величина W-Z, на второй его вход поступает величина V+uV, на вход регистра 24 - величина V. На выходе счетчика 22 формируется третье слагаемое суммируется в блоке 25 суммирования с имеющимся там числом. В четвертом такте с четвертого импульсного выхода регистра 26 сдвига формируется сигнал на считывание результата вычислений 2+Л.2 с выхода блока 25 суммирования и на разрешение записи имеющихся входных величин в .ячейки 6-10 памяти.Таким образом, входные величины, выполняв,шие в вычислении роль текущих вели1чин, записываясь в ячейки памяти, становятся предыдущими, величины, поступающие на входы блоков 1-5 вычитания от внешних источников, становятся текущи, а на выходах этих блоков вычитания формируются новые приращения входных величин. Операции считывания, установки улей и разрешений записи в ячейки амяти осуществляются устройствами, ходящими непосредственно в вычисительный или управляющий кo «Iлeкc на чертеже не показаны). При поступлении результата выислений в вьлчислительную машину на посылает импульс на вход реистра 26 сдвига, разрешёиовдий послеующую работу устройства. Быстродействие устройства определяется следующим образом ьЛ| .-.-- 2-V-N N N-vcs-V M-t-b-V Сравнительные испытания на цифровой модели данного следящего цифрового мно)|сительно-делительного устройства с известным показали, что при текущих i значениях входных величин: ;+й., у+лу 100, V+U.V 100, предыдущих значениях X i 90, у 90, V - 90, т.е. измен нии входных параметров до 10%, при которых дх 10, лу 10, A.V 10, вреМя решения 0,3 ед, времени, т.е. вре мя решения в сравнении с имеющимся мно ительно-делительным устройством сокращено более чем в 3 раза. Формула изобретения Цифровое множительно-делительное ус1)ройство, содержащее двухканальны пре|образователь код-частота, два счетчика импульсов, регистр сомножи теля и схему сравнения, причем счет ны входы счетчиков импульсов соеди нейы с выходами двухканального прео ра ователя код-частота, выходы первоз о счетчика импульсов соединены с Первой группой входов схемы сравн ния, вторая группа входов которой соединена с выходом регистра сомножителя, отличающееся теф, что, с целью повышения быстроде ствия, в него дополнительно введены ячейки памяти, блоки вычита ний, семь групп элементов И, регист сдвига, элемент ИЛИ, блок суммирования, причем выходы блоков вычитания с первого по пятый соединены со входами соответствукядих ячеек памяти, выходы которых соединены со входами вычитаемого блоков вычитания, а входы уменьшаемого с первого по четвертый блоков вычитания являются входами устройства, входы уменьшаемого пятого блока вычитания соединены с выходами блока суммирования, первая группа входов которого соединена с выходом второго счетчика импульсов, вторая группа входов - с выходами четвертого блока вычитания, а третья группа входов с выходами пятой ячейки памяти и входами уменьшаемого шестого блока вычитания, входы вычитаемого которого соединены с выходами четвертой ячейки памяти, выходы первого, второго и третьего блоков вычитания соединены соответственно через элементы И первой, четвертой и шестой группы со входами регистра сомножителя, выходы первой ячейки памяти, шестого блока вычитания, входы уменьшаемого второго блока вычитания соответственно через элементы И второй, третьей и седьмой групп соединены с первой группой входов двукканального преобразователя код-частота, вторая группа входов которого соединена через пятую группу элементов И со входами уменьшаемого третьего блока вычитания, первый выход регистра сдвига соединен с управлятадими входами первого и третьего элементов И и с первым входом элемента ИЛИ, второй вход - с управляющими входами элементов И второй и четвертой групп и со вторым входом элемента ИЛИ,, а третий выход с управляющими входами элементов И шестой и седьмой групп и третьим входом элемента ИЛИ, выход которого соединен с управляющим входом элементов И пятой группы, выход схемы сравнения подключен к управляющему входу регистра сдвига. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР W 165584, кл. G 06 F 7/30, 1963. 2.Авторское свидетельство СССР № 310257, кл. G 06 G 7/16, 1970 (прототип). VfiV HftiVf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поворота вектора (его варианты) | 1982 |

|

SU1078431A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для сжатия и восстановления информации | 1983 |

|

SU1149295A1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Арифметическое устройство процессора для Фурье-преобразования сигналов | 1986 |

|

SU1387011A1 |

| Сенсорный переключатель | 1982 |

|

SU1051720A1 |

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Функциональный преобразователь | 1983 |

|

SU1136154A1 |

| Экстраполирующий умножитель частоты | 1987 |

|

SU1497706A1 |

| Псевдостохастический анализатор спектра | 1985 |

|

SU1278885A1 |

Авторы

Даты

1980-06-25—Публикация

1978-04-11—Подача