1

Изобретение относится к аналого-, вой вычислительной технике и может быть использовано в качестве специализированного аналогового процессора гибридной вычг слительной систек-и для моделирования разнообразных динамических систем и объектов, а также в системах автоматической обработки результатов наблюдений, работающих в реальном масштабе времени ,

Известны устройства, предназначеннгле для моделирования линейных систем и объектов по их динамическим характеристикам,, которые могут быть получены экспериментальным или расчетным путем 1.

Известное устройство лредставляет собой динамический линейный преобразователь, содержащий решающие блоки на операционных усилителях, с помощью которых моделируется известная динак-мческая или передаточная функция системы, и который по заданному входному воздействию позволяет определить выходной сигнал системы.

Наиболее близким по технической сущности к предлагаемому является .моделирующее устройство, содержащее генератор импульсов, блок памяти, блок резисторов, моделирующих весовую функцию, и блок сумматоров, который по зЕщанной динамической характеристике линейного стационарного объекта и входному сигналу Z(t) позволяет находить выходной сигнал U(t), который в общем случае может быть представлен в виде:

10

/K(t-t)2Ct)dt-U(t,

-где K() - импульсная переходная

функция, короче;импульсная функция объекта 2.

15 Однако на практике весьма часто приходится решать задачу в обратной постановке, когда для объекта известна функция K(t) и известен выходной сигнал U(t), а требуется определить

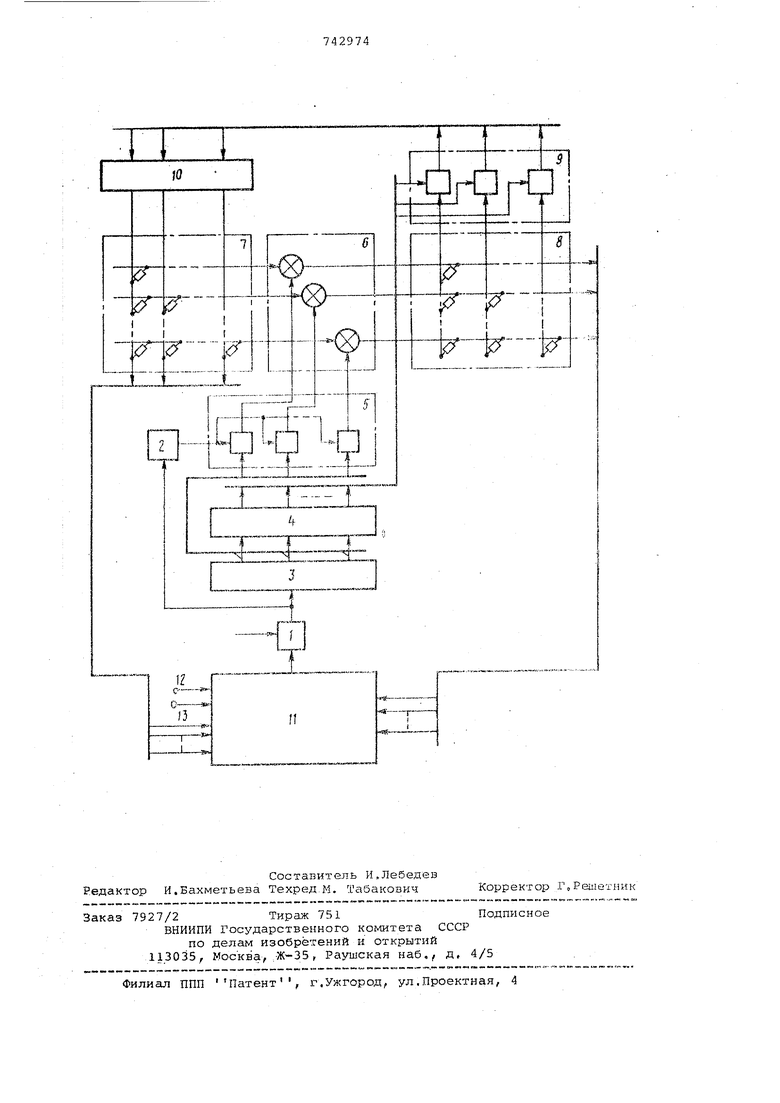

20 соответствующее входное воздействие Z(t), Такая задача является существенно более сложной,и не может быть решена с помощью известного устройства, Цель изобретения - расширение функ25циональных возможностей устройства. Для достижения цели в устройство для моделирования линейных динамических систем, содержавшее генератор импульсов, выход которого соединен с переключающим входом распределителя иМпульсов, выходы которого соединены соответственно с управляющими входами блока памяти, выходы котог Р0ГО соединены соответственно с первс1й группой .входов блока сумматоров в-Сорая группа входов которого подклю соответственно к горизонтальнЦм шинам резисторной -сетки, и коммутатор, дополнительно введены управ лйющий регистр, функциональный преоб ра;зователь, дополнительная резисторна;я сетка, блок интеграторов и блок с внения, причем выходы распределиTdnH импульсов через управляющий реги стр соединены соответственно с упра|вляюи1ими входами коммутатора, инфс рмационные входы которого соединимы соответственно с вертикальными шинами дополнительной резисторнрй сетки, а выходы коммутатора сое;: инены соответственно со входами 6jioKa интегратора, выходы которого пс(дключены соответственно к вертик льным ши:нам резисторной сетки, соответственно соединенным с первой группой входов блока сравнения, ко Вйорой грушше входов которого подклю соответственно горизонтальные шИ;Ны дополмштельной резисторной сетки;, соединенные соответственно с вы хсздами блока сумматоров, причем первь й и второй информационные входы сравнения являются входами устройства, а выход блока сравнения соединен с первым управляющим входом ге:нератора импульсов, второй управл Ю14ИЙ вход которого является запускаюи им входом устройства, и выход гене ратора импульсов соединен со входом фу нкционального преобразователя, вы ход которого связан с объединенными информационным - входами блока памяти Изобретение поясняется чертежом, Устройство содержит генератор им пульсов 1, функциональный преобразователь 2, распределитель импульсов 3, управляющий регистр 4, блок памяти 5, блок сумматора 6, резисторная сетка 7, дополнительная резисторная сетка 8, коммутатор 9, блок интеграторов 10, блок сравнения 11, первый и второй входы устройства 12 и 13, Связи блоков в устройстве осуществляются системами шин-магистралями, Входы устройства 12 и 13 служат для задания известных уровней погреш ности импульсной функции К(t) и выходного сигнала U(t), Резисторная сетка 7 моделирует заданную импульс ную функцию K(t), дополнительная ре зисторная сетка 8 реализована анало гично основной, с тем.отличием, что выходы ОСНОВНОЙ резисториой сетки служат входами дополнительной и наоборот. Число ячеек в каждом блоке устройства определяется з-аданным уравнением дис;кр тизации- временной . переменной t, t- 1дС, ,2,,,.п. Без ограничения обшности- полагаем K(t) на всем интервале изменения независимой переменной t. Устройство работает следующим образом, В исходном состоянии ячейки распределителя 3, регистра 4, блока памяти 5 хранят нулевую информацию, конденсаторы в цепях обратной связи интеграторов 10 заряжены до напряжений, уровни которых определяются некоторым начальным приближением к искомому решению Z(t} (в частности, это может быть нулевой вектор), Ключи коммутатора 9 разомкнуты и связь между дополнительной резисторной сеткой 8 и блоком интеграторов 10отсутствует. Работа устройства начинается приходом сигнала Пуск, по которому генератор 1 вырабатывает импульс,по.ступсиощий на вход распределителя 3 и вход функционального преобразователя 2 , При этом на выходе первого канала распределителя 3 появляется , которая устанавливает в состояние 1 первый разряд регистра 4, Импульс с выхода распределителя 3 поступает также на управляющий вход первой ячейки памяти блока 5, обеспечивая тем самым запоминание значения сигнала U(t), вырабатываемого функциональным преобразователем 2, С выхода первой ячейки памяти значение U(t-f) поступает на вход первого сумматора блока б, Одновременно с этим i на выходе первого разряда регистра 4 замыкает первый ключ коммутатора 9, что приводит к началу переходного процесса в устройстве, цель которого найти такое приближенное значение Z (t) , которое позволяло бы восстановить известное значение U(t) с заранее заданной погрешностью. Назначение блока сравнения 11 в переходном процессе - согласовать точность образуемого на выходах интеграторов 10 решения Z(©) с уровнем погрешности исходной информации. Для этого на входы блока сравнения помимо уровней погрешностей поступают значения решений 2(9) и сигналы рассогласования, образуемые на выходах сумматоров блока 6, Когда требуемый.уровень точности получаемого решения оказывается достигнутым, блок сравнения 11 формирует сигнал окончания интегрирования на данном такте. С выхода блока 11на первый управляющий вход генератора 1 поступает импульс, который по своему действию аналогичен сигналу Пуск, Генератор 1 вырабатывает очередной импульс, поступающий на входы функционального преобразователя 2 и переключающий вход распределителя 3, При этом появляется импульс на втором канале распределителя 3, что приводит к установке в состояние I Второго разряда регистра 4, и разрешает запись текутего значения сигнала U (tg) функционсшьного преобразователя 2 во вторую ячейку блока памяти 5. Одновременно с этим 1 на выходе второго разряда регистра 4 замыкает второй ключ коммутатора 9, что приводи ,к началу нового цикла интегрирова.ния. При этом начальными условиями для первого интегратора блока 10 служит значение искомой переменной 2(ti) , полученное в конце предыдущего цикла.

Процесс решения заканчивается после завершения п циклов работы устройства. При этом на выходах интеграторов блока 10 фиксируются значения вектора Z(t), согласованные с заданным уровнем погрешности исходной информации.

Далее, при необходимости процесс решения можно организовать с заданной частотой периодизации.

Таким образом,, выполнение устройства в соответствии с изобретением позволяет расширить функциональные возможности известных устройств и может быть использовано в автоматических системах обработки экспериментальной информации, работающих в реальном масштабе времени,

Формула изобретения

Устройство для моделирования линейных динамических систем, содержащее генератор импульсов выход которого соединен с переключающим входом распределителя импульсов, выходы которого соединены соответственно с управляющими входами блока памяти, выходы которого соединены соответственно с первой группой входов блока сумматоров, вторая группа которого подключена соответственно к горизонтальным шинам резисторной сетки, и коммутатор, отличающееся тем, что, с цепью расширения функциональных возможностей реше.ния обратной задачи, в него дополни. тельно введены управляющий регистр, функциональный преобразователь, дополнительная резисторная сетка, блок интеграторов и блок сравнения, причем выходы распределителя импульсов через управляющий регистр соединены соответственно с управляющими входами коммутатора, информационные входы которого соединены соответственно с вертикальными шинами дополнительной резисторной сетки, а выходы ком5 мутатора соединены соответственно со входами блока интегратора, выходы которого подключены соответственно к вертикальным шинам резисторной сетки, соответственно соединенным с первой

0 группой входов блока сравнения, ко второй группе входов которого подключены соответственно горизонтальные шины дополнительной резисторной сетки, соединенные соответственно с выхо5 дами блока сумматоров, причем первый и второй информационные входы блока сравнения являются входами устройст- ва, а выход блока сравнения соединен с первым управляющим входом генератора импульсов, второй управляющий вход - которого является запускающим входом устройства, а выход генератора, импульсов соединен со входом функционального преобразователя, выход которого связан с объединенными информа ционными входами блока памяти.

Источники информации, принятые во внимание при экспертизе

1.Кириллов В.В., Моисеев B.C.

0 Аналоговое моделирование динамических систем,. Л., Машиностроение, 1977, с,117-129,

2.Авторское свидетельство СССР 384108, кл. G 06 G 7/48, 1971 г, (прототип)..

:

-Т™

««..ем-та™

Е

-КН

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь среднего значения напряжения | 1982 |

|

SU1114964A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Устройство для кодирования аналоговых сигналов | 1989 |

|

SU1624696A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Устройство для контроля аналоговых объектов | 1989 |

|

SU1718189A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Функциональный преобразователь | 1983 |

|

SU1109765A1 |

Авторы

Даты

1980-06-25—Публикация

1978-04-17—Подача