(54) УСТРОЙСТВО ДЛИ ВЫБОРКИ КОМАНД

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования команд | 1978 |

|

SU734686A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Вычислительная система | 1989 |

|

SU1777148A1 |

| Устройство центрального управления процессора | 1983 |

|

SU1136177A1 |

| Устройство для адресации буферной памяти | 1978 |

|

SU717771A1 |

| Центральный процессор | 1991 |

|

SU1804645A3 |

| Устройство управления буферной памятью | 1978 |

|

SU737952A1 |

| Вычислительная система | 1977 |

|

SU692400A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

Изобретение может быть использовано в области вычислительной техники, в частности в KOMaHfltioM блоке центрально го процессора, который осуществляет под готовку команд для выполнения RX испоп- нительными устройствами. Известно устройство для выборки команд yij , содержащее регистр состояния программы, счетчик адреса программы, регистр адреса программы, c.oeдинeн ные между собой соответствующим сбра- зом для выработки исполнительного адреса команд, который поступает с выхода регистра адреса программы на первый адресный выход устройства, два регистра команд, которые предназначен ы ;для приема командных слов из оперативной, памяти через информационньй вход устройства и вьщачи И.Х на узел распаковки который управляется счетчиком адресов . команд и дешифратором распаковки, регистр смещения, регистры общего назначе1Л1я, адресный сумматор, предназначенный для суммирования смещения с баЗОЙ,. считанной аз соответствующего гистра общего назначения с целью формирования исполнительного адреса для команд считьшания, записи или ветвления, который с выхода адресного сумматора поступает на аход регистра состояния nporpaivtMu и второй адресный выход устройства. Устройство нэ-за малой буферизации командных слов имеет ограниченные возможности .при работе с оперативной памятью, быстродействие которой меньще бьгстродействия центрального процессора. Кроме того, команды ветвления вызывают значительные перерьшы в потоке дещифрируемьк команд, связанные с вызовом из памяти первой команды новой ветви. Увеличение степени буферизации командных слов за счет введения буферной памяти команд, а также многократного использования команд, ранее вызванных в буферную память, позволяет сформировать командный поток с плотностью, „одна комаида за такт процессора гтри работе с памятью меньшего быстродействия, чем Ттроцессор, и сократить, во многих слу- «laffic Ttep pi,tBbi в потоке команд, связанные с ветвлениями. Наиболее близким по технической сущ ности к изобретению является устройство для выборки команд 2}, содержащее буфер команд из восьми адресуемых рШ рбв; деаддпойнительных адресуе-, . йых регистра, которые используются при обработке команд условного,перехода, регистр верхней границы со схемой при ращения, определяющий вместе с регистром верхней границы количество командньтх слоев в буфере Команд и их. расположение оперативной памяти, регистр считьшания со схемой приращения для считывания командных слов из буфера команд на регистр операций, узел вьщепь;тия команды -выделяющий команду из регистра операций для последующих ее дешифра дни и вьвдачи в исполнительные устройст ва, адресный сумматор для формирования адреса обращения к оперативной памяти из базового адреса и смещения, причём базовый адрес поступает на сумматор из одного из шестнадцати регистров общего назначения, которые как и устройство для выборки команд входят в сос fae центрального процессора,а смещени задано в дешифрируемой команде, рабо.чий адреснь1йрегистр, вход Кбтбрбго сое Hvitfea с Выходом адресного cyi№ifitopa, а выход подключен к адресной шине устройства, к регистрам считывания верхней и нйжнёй гранш1 дпя йх с:тЖн(5ЁКи .1гбдё вЁтсэтиения команд ветвления, а taKSce К узлуанализа перехода на локал ность в буфере команд, с помощью кото рШ Ш|Геда Гяёт15яГ-нихЩйГсйpax буфере команд команда, на которую передается управление командой ветвле- Hffart tip5tHWt вх6да1Й уШа ШШ11 зГ пере хода на локальность в буфере команд подключены выходы регистров верхнейTi нижней границ. Введение буферГкШхайИ й Э Вста.йй слов, а также указателей верхней и ниж ней границ, позволяет обеспечить при . ветвлениях быстрый доступ к командам, расположенным внутри буфера команд Однако перерывы в потоке дешифрируемых команд все же имеют место. Для , команд условного перехода пёрерьшы связаны с отменой условнд расшифрованных команд. При обработке команд без рЙШШ Г1Ш1 МШГ1ЙЙйт Е1ва.в деш фрации складывается из двух величин. Первая обусловлена временем формирования адреса перехода. Вторая зависит от условий, находится ли команда, на которую производится переход, в буфере команд. Если ответ положителен, комавда считьгаается из буфера команд без обращения в оперативную память, если отрицателен - очередная команда считывается из оперативной памяти. Для ветвлений на команды, расположенные внутри буфера команд, время формирования адреса перехода составляет 75% от полного времени выполнения команды безусловного перехода, что замедляет выполнение ветвления. Целью изобретения является повышение, быстродействия за счет уменьшения времени выполнения ветвлений командами бузусловного пере.хода. Пеставлейнай цель достигается тем, что в известное устройство для вьгборки команд, содержащее блок буферных регистров команд, информационный и адресный входы которого являются первым и вторым входами устройства, выходы ,блока буферных рёТйстрШ команд соединены с группой вхЬдов первого коммутатора, вькод которого соединен с входом регистра команд и через дешифратор длины Команды с первым кходом второго коммутатора, &&КЩ которого соединён с управляющим В.ХОДОМ первого коммутатора, выхоД регистра Команд является первым выходом устройства и соединен через регистр индекса с первым входом первого сумматора адреса, второй аход и выход которого являются третьим ьходом и вторым выходом устройства соот ветственно, регистры верхней и нижней границы введены регистр базы текущей процедуры, второй сумматор адреса, узел анализа перехода на локальность в буфере команд. Вход регистра базы текущей процедуре йвп11ёТСячетверть1М входом устройства, второй входвторого коммутатора и пё|звь1ё вчЬды регистров вер.хней и нижней границ объединены и являются пятым В.ХОДОМ устройства. Вьгход регистра верхней Границы является третьим выходом устройства и соединен с первыми входами узла анализа перехода на локальность в буфере КбМайД и второго сумматора адреса, второй вход которого соеди ней с выходом регистра базы текущей процедуры. Выход второго сумматора адреса является четвертым выходом устройства.

Выход регистра команды соединен с третьим входом второго ; коммутатора и

вторыми входами регистров верхней и нижней границ. Выход регистра нижней границы соединен с третьим входом узла анализа перехода на локальность в буфере команд, выход которого является пятым выходом устройства и узел анализа перехода на локальность в буфере команд содержит два сумматора и

, элемент ИЛИ. Первые входы сумматоров соединены с первым и третьим -входами узла, вторые входы. - со вторым входом узла, а выходы через элемент ИЛИ - с выходом узла.

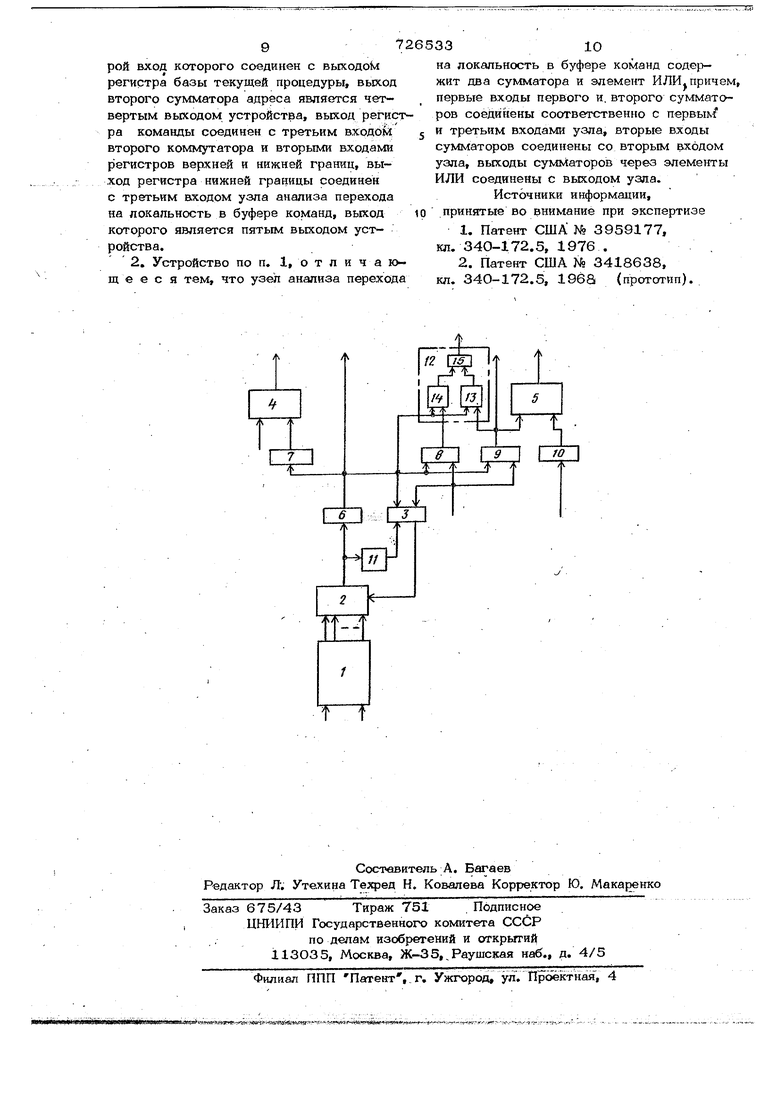

Структурная схема устройства приведена на чертеже.

Устройство содержит блок 1 буферных регистров, коммутатор 2, регистр 3 считывания, сумматоры 4,5 адреса, регистр б команды, регистр 7- индекса, регистр 8 нижней границы, регистр 9 верхней границы, регистр Ю базы текущей процедуры, дешифратор 11 длины

команды, узел 12 анализа перехода на локальность в буфере команд.

Узел 12 содержит сумматоры 13,14 и емент ИЛИ 15.

Устройство работает следующим образом..

Программы пользователя и опера- ционной системы представляют собой совокупность процедур, каждая из которых обладает свойством повторной аходимости Доступ к командам и данным процедур осуществляется через таблицы управляющах опоев - дескрипторов, каждый из которых описывает некоторую логическую область памяти произвольной длины. В общем случае дескриптор содержит базу адрес начала массива некоторой процедуры, и количество-величину, определяк щую размер массива.

Доступ к слову, расположенному внутри массива, осуществляется путем индексирования соответствующего дескриптора. Сущность этой операции состоит в следующам. Команды считьшания, записи и ленив включают в себя информацию о расположении дескриптора и смещение-индекс Из дескриптора выделяется база и сумШруется с индексом.

Полученный таким образом исполнительный адрес идентифицирует расположение требуемого слова в оперативной памяти.

Выполнению процедуры предшествуют анализметки процедуры и занесение соответствующих дескрипторов в базовые регистры, чтобы обеспечить последующим операциям считьюания и записи доступ к параметрам процедуры, .которые определены контекстом. Дескриптор ко- ,. 5 мандного сегмента запускаемой процедуры выбирается из таблицы дескрипторов командных сегментов, а выделенная из него база поступает на регистр 10, После первой команды вьзделяется из

0 метки процедуры и поступает в регистры 3, 8 и 9.

Комавды ветвления делятся на два типа - Непосредственные и дйна,гаческие. Непосредственные комавды передают

5 управление на другие команды текущей процедуры. Динамические команды ветвления передают управление на. команды другах процедур, что равнозначно входу в новую пройедуру. Динамические команды

0 ветвления встречаются в потоке команд намного .реже непосредственных команд и в описании не рассматриваются, В

связи с этим, команда непосредственного ветвления включает в себя код операции

и индекс - смещение относительно базы текущей процедуры. .

После входа в процедуру начинается подкачка командных слов из оперативной , памяти в буфзрные регистры команд бло0ка 1. Содержимое регистра 9 суммируется с базой текущей процедуры на сумматоре 5,

Выработанньсй таким образом адрес является адресом первого командного

0 содержимое регистра 9 увеличивается нг единицу, и формируется адрес очередногс командного слова. Когда разница между содержимым регистра 9 и регистра 8 достигнет восьми, содержимое регистра

3 начинает увеличиваться на eflimimy С1шхронно с содержимым рагистра 9.

Вызванное из оперативной памяти командное слово и номер регистра блока ; поступают на соответствующие входы уст0ройства, Дещифратор адреса регистра блока 1 выбирает регистр, в которЬгй необходимо произвести запись командного слова. Посла записи командного слова в блок 1 начинаэтся формирование потока команд для ; . их дешифрации w выполнапип. Все команды имеют длину кратную байту, и расположены в командном массиве вплотную друг за другом. Длина командного слова восемь байтов. .7. 7 Содержимое регистра 3 представляет собой шестиразрядное число. Три старших разряда обозначают номер регистра блока .1у в котором расположено начало команды, а три младши-х разряда - номер байта, с котОрого-начинается команда. Коммутатор 2 вьщеляет четыре смежных байта, на чиная с определяемого регистром 3, так что код операции команды оказьюается влево Бопыййнстбо команд имеют длину от одного до четырех байтов, -Кема щы с большей длиной обрабатываются за несколько тактов. Дешифратор 11 в зависи Ыости .от кода операции вырабатывает дпйну команды, достигаюшую на вход приращения регистра 3, вследствие чего указатель увеличивается на соответствующую величину, переходя, таким образом, к вьщелению следующей коман,ды. Разность между соДёржийьтШЁ-регист ров 3 и 9 определяет необходимость вы™ дмй очерёдного запроса в оперативную память, создавая необходимьй запас нерасщифрованньге команд. Информация с выхода коммутатора 2 поступает на регистр 6, с которого команды поступают на дешифрацию и вьшол нение. При дешифрации команд считьюаиия или записи исполнительный адрес формируется следующим образом. Из регистра 6 поле, означающее номер базового регистра, поступает для считьюания соответствующей базы, кот рая затем поступает на сумматор 4. По ле регистра 6 означающее,смещение тре буемой информации относительно базы, подается на регистр 7, с выхода которо го после необходимой задержки оно поступает на .сумматор 4. В результате суммирования вырабаты вается исполнительный адрес, который . передается на соответствующий выход устройства. При дешифрации команды ветвления (в частности, команды непосредственног перехода) поле регистра 6, означающее индекс перехода, псютуп&ет в сумматоры 13, 14 узла 12, где проверяется условие ВГ ИП НГ. (ВГ - значение регистра 9, ИП - индекс перехода, НГ - знач ние регистра 8). Результаты анализа ч рез элемент ИЛИ 15 передаются на соо ветствующий выход устройства. Если неравенство выполняется, соот-вйтйтвующйе шесть младших разрядов индекса перехода с выхода регистра 6 3 ,8 поступают на регистр 3 н ориентируют го на начало ветви. Если неравенство не выполняется, регистры блока. 1 обнуяются, а индекс перехода передается с вых-ода регистра 6 дополнительно на регистры 8,9, Подкачка в регистры блока 1 начинается с комавдного слова, в котором находится первая команда ветви. Таким образом, в предлонсенное устройство при выполнении безусловного перехода на команды, расположенные внртри блока буферных регистров 5соманд, отсутствует этап формирования адреса перехода, а все ветвление сводится лишь к передаче соответ.ствующах разрядов регистра команд на регистр считьюания. При этом время выполнения ветвления сокращается в два раза. Устройство входит в состав центральных процессоров многопроцессорного вычислительного комплекса. Формула изобретения 1. Устройство для выборки команд, содержащее блок буферных регистров .команд, информационный и адресный входы которого ЯВЛ.ЯЮТСЯ первым и вторым входами устройства, выходы блока буферных регистров команд соединены с груп- пой входов первого коммутатора, выход Которого соединен с входом регистра команд и через дешифратор длины команды с первым входом второго коммутатора, выход которого соединен с управлгполцим входом первого коммутатора, выход регистра команд является первым выходом устройства и соединен через регистр индекса с nepBbnvi входом первого сумматора адреса, второй вход и выход которого являются третьим в.ходом и вторым Bbt ходом устройства соответственно, регистры верхней и нижней границ, отличающееся тем, что, с целью повышения быстродействия, в него введены регистр базы текущей процедуры, второй 9умматор адреса, узел анализа перехода на локальность в буфере команд. Вход pejTHCTpa басзы текущей процедуры является четвертым Б.ХОДОМ устройства, второй вход второго коммутатора и первые входы регистров верхней и нижней границ объединены и являются пятым входом устройства, выход регистра верхней границы является третьим выходом устройства и соединен с nepBbnvra входами узла анализа перехода на локальность в буфере команд и второго сумматора адреса, второй вход которого соединен с выходоК регистра базы текущей процедуры, выход второго сумматора адреса является четвертым выходом устройства, выход регист ра команды соединен с третьим входой второго коммутатора и вторыми входами регистров верхней и нижней границ, выход регистра нижней границы соединён с третьим входом узла анализа перехода на локальность в буфере команд, выход которого является иятым выходом устройства. 2. Устройство по п. 1, о т л и ч а ющ е ее я тем, что узел анализа перехода 7 3310 на локальность в буфере команд содержит два сумматора и элемент ИЛИ причем, первые входы первого и, второго сумматоров соединены соответственно с nepBbiN-f и третьим входами узла, вторые входы сумматоров соединены со вторым входом узла, выходы сумматоров через элеме1ггы ИЛИ соединены с выходом узла. Источники информации, принятые во внимание при экспертизе 1.Патент США№ 3959177, кл. 340-172.5, 1976 . 2.Патент США № 3418638, кл. 340-172.5, 1968 (прсхготип).

Авторы

Даты

1980-04-05—Публикация

1978-01-18—Подача