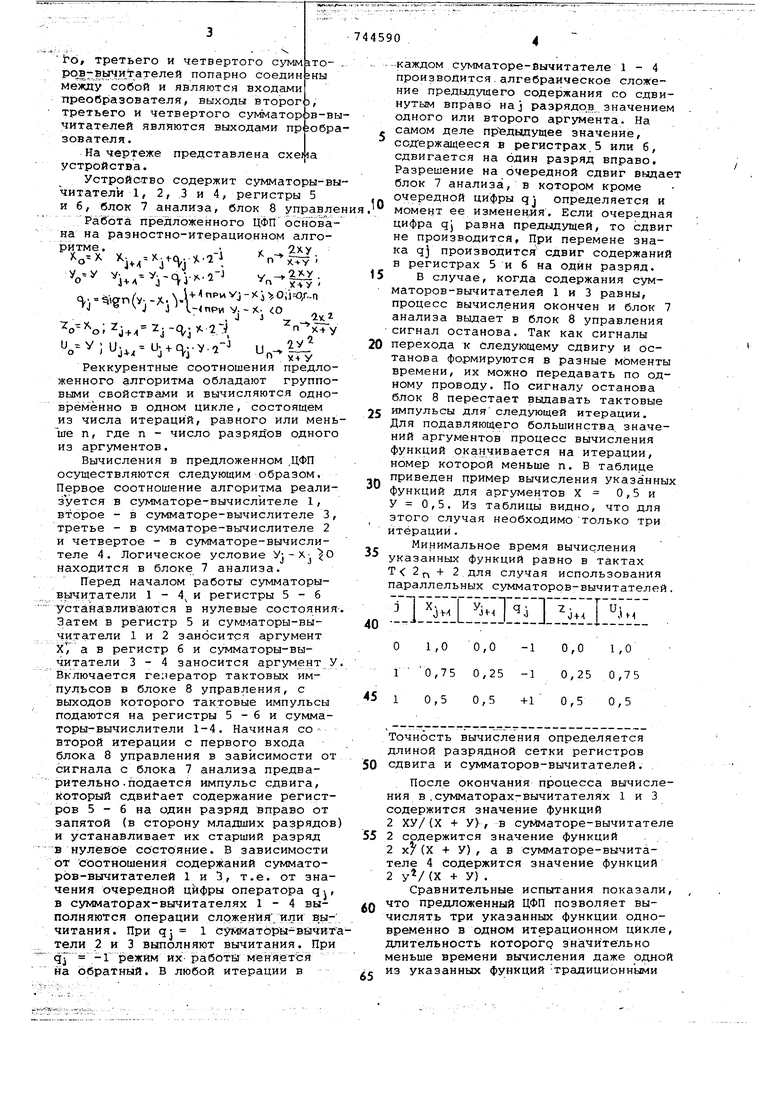

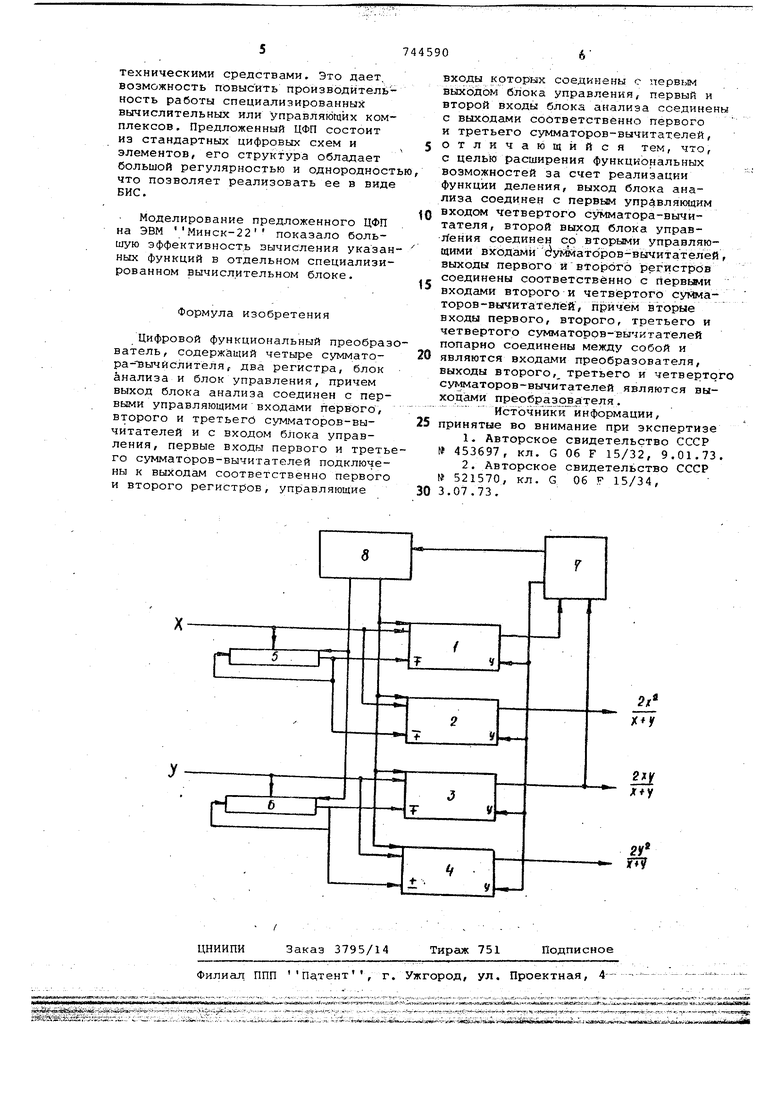

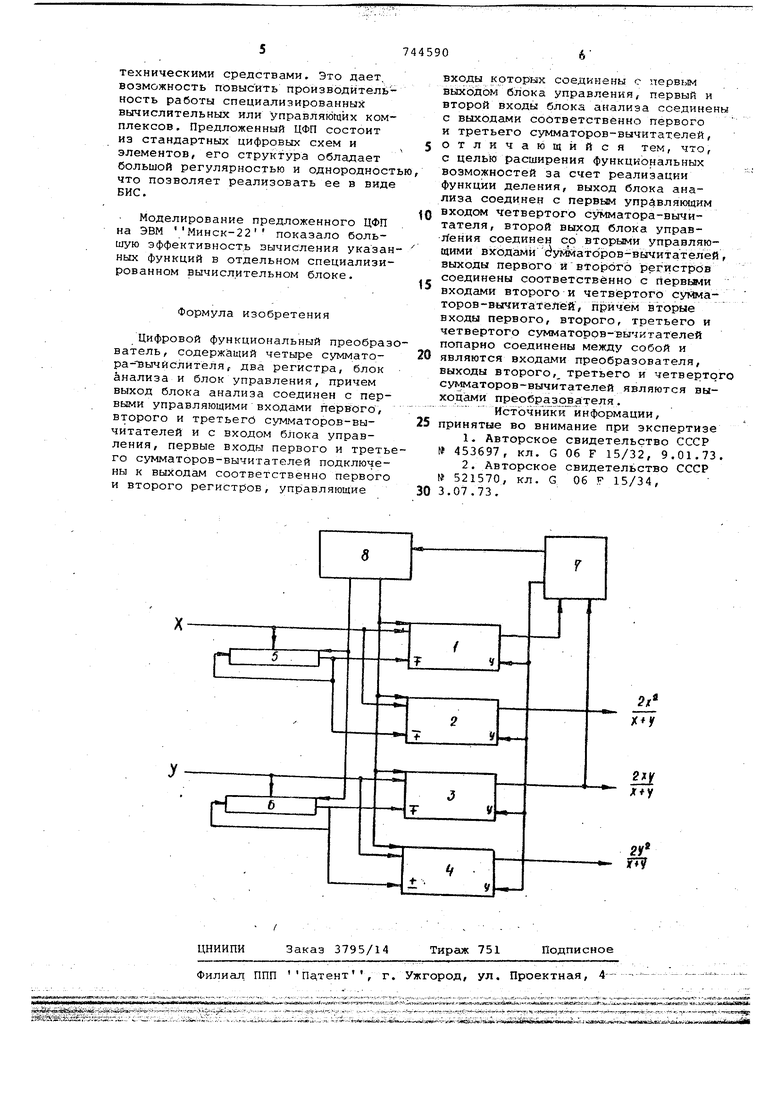

Изобретение относится к цифровой вычислительной технике и может найт применение для аппаратной реализации вычисления частного от.произведения на сумму двух аргументов. Известен цифровой функциональный преобразователь, содержащий счетчик -(регистр), сумматор, схемы сравнения, блок управления, дешифратор, узел объединения, схемы И и ИЛИ, триггеры. Выход счетчика подключен ко входу сумматора, выходы блока управления соединены суправляющим входом сумматора и входом счетчика 1 . Недостатком известного устройств является то, что оно не предназначено для вычисления функции частног от произведения на сум.му двух аргументов.. Наиболее близким техническим ре шением к предлагаемому является циф ровой функциональный преобразователь, содержащий четыре сумматоравычислителя, два регистра, блок анализа и блок управления, причем выход блока анализа соединен с первыми управляющими входами первого, второго и третьего сумматоров-вычитателей и с входом блока управления, первые входы первого и третьего сумматоров-вычитателей подключены к выходам соответственно первого и второго регистров, управляющие входы которых соединены с первым выходом блока управления, первый и второй входы блока анализа соединены с выходами соответственно первого и третьего сумматоров-вычитателей 2. Преобразователь содержит, кроме того, четыре регистра. Недостатком преобразователя является невозможность вычисления частного. цель изобретения расширение функциональных возможностей за счет реализации функций деления. Поставленная цель достигается тем, что выход блока, анализа соединен с первым управляющим входом четвертого сумматора-вычитателя, второй выход блока управления соединен со вторыми управляющими входами сумматоров-вычитателей, выходы первого и второго регистров соединены соответственно с первыми входами второго и четвертого сумматоров-вычитателей, причем вторые входы первого, второг6, третьего и четвертого сумм1торов-вычитателей попарно соедин гны между собой и являются входами преобразователя, выходы второг третьего и четвертого сукп аторЬв-в читателей являются выходами npi;o6p зователя. На чертеже представлена cxeffia устройства. Устройство содержит сумматоры-вы читатели 1, 2, 3 и 4, регистры 5 и б, блок 7 анализа, блок 8 управл Работа, предложенного ЦФПоснова на на разностно-итерационном алгоритме.. 2ху о- iM- j j .4./ vy I. j -1 j..- r4J- -2 Vn С -,дп(у.-Л.ЛД ° - J ® М J 1-4 ПРИ у.-X.. 0 , 2j-q,j,2 vy;uj,,-u.c..v.7 Реккурентные соотношения предложенного алгоритма обладают групповыми свойствами и вычисляются одновременно в одном цикле, состоящем из числа итераций, равного или мень Ъте п, где п - число разрядов одного из аргументов. Вычисления в предложенном ДФП осуществляются следующим образом. Первое соотношение алгоритма реализуется в cyivnviaTope-вычислителе 1, второе - в сумматоре-вычислителе 3 третье - в сумматоре-вычислителе 2 и четвертое - в сумматоре-вычислителе 4. Логическое условие находится в блоке 7 анализа. Перед началом работы сумматорывычитатели 1 - 4 и регистры 5-6 устаНавливаются в нулевые состояния Затем в регистр 5 и сумг аторы-вычитатели 1 и 2 заносится аргумент х , а в регистр б и сумматоры-вычитатели 3-4 заносится аргумент У Включается генератор тактовыэс импульсов в блоке 8 управления, с выходов которого тактовые импульсы подаются на регистры 5 - б и сумматоры-вычислители 1-4. Начиная со второй итерации с первого входа блока 8 управления в зависимости от сигнала с блока 7 анализа предварительно -подается импульс сдвига, который сдвигает содержание регистров 5 - б на один разряд вправо от запятой (в сторону младших разрядов и устанавливает их старший разряд в нулевое состояние. В зависимости от соотношения содержаний сумматоров-вычитателей 1 и 3, т.е. от значения очередной оператора qj в сумматорах-вычитателях 1-4 выполняются операции сложения или вычитания. При qj 1 сумМатЬры-вач:ит тели 2 и 3 выполняют вычитания. При режим их- работа меняется на обратный. В любой итерации в -каждом сумматоре-вычитателе 1 - 4 производится.алгебраическое сложение предыдущего содержания со сдвинутым вправо Haj разрядо в значением одного или второго аргумента. На самом деле предыдущее значение, содержащееся в регистрах.5 или б, сдвигается на один разряд вправо. Разрешение на очередной сдвиг выдает блок 7 анализа, в котором кроме очередной цифры qj определяется и момент ее измененля. Если очередная цифра qj равна предыдущей, то сдвиг не производится. При перемене знака qj производится сдвиг содержаний в регистрах 5 и 6 на один разряд. В случае, когда содержания сумматоров-вычитателей 1 и 3 равны, процесс вычисления окончен и блок 7 анализа выдает в блок 8 управления сигнал останова. Так как сигналы перехода к Следующему сдвигу и останова формируются в разные мОменты времени, их можно передавать по одному проводу. По сигналу останова блок 8 перестает выдавать тактовые импульсы для следующей итерации. Для подавляющего большинства значений аргументов процесс вычисления функций оканчивается на итерации, номер которой меньше п. в таблице приведен пример вычисления указанных функций для аргументов X 0,5 и У 0,5, Из таблицы видно, что для этого случая необходимо только три итераций. Минимальное время вычисления указанных функций равно в тактах Т 2 р, + 2 для случая использования параллельных сумматоров-вычитателей. r l35il ri5 I 01,0 0,0 -1 0,0 1,0 1 0,75 0,25 -1 0,25 0,75 10,5 0,5 -f 1 0,5 0,5 Точность вычисления определяется длиной разрядной сетки регистров сдвига и сумматоров-вычитателей. После окончания процесса вычисления в .сумматорах-вычитателях 1 и 3 содержится значение функций 2 ХУ/{X + У), в сумматоре-вычитателе 2 содержится значение функций 2 х(X + У), а в сумматоре-вычитателе 4 содержится значение функций 2 yV(X + У) . Сравнительные испытания показали, то предложенный ЦФП позволяет вычислять три указанных функции одновременно в одном итерационном цикле, лительность которого значительно еньше времени вычисления даже одной из указанных функций -традиционными

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь | 1976 |

|

SU591861A1 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Цифровой функциональный преобразователь | 2017 |

|

RU2642381C1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления элементарных функций | 1980 |

|

SU920716A2 |

| Функциональный преобразователь | 1977 |

|

SU693379A2 |

Авторы

Даты

1980-06-30—Публикация

1976-07-19—Подача