Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации вычисления функций.

Известен цифровой функциональный преобразователь [А.с. 744595 СССР, 1978], содержащий блок анализа, первый и второй сумматоры-вычитатели, первый и второй регистры и блок управления, причем выход первого регистра соединен с первым входом первого сумматора-вычитателя, выходы блока управления соединены с управляющими входами первого и второго регистров и тактовыми входами первого и второго сумматоров-вычитателей, выходы которых соединены с входами блока анализа, первый выход которого подключен ко входу блока управления, а второй выход соединен с управляющими входами первого и второго сумматоров-вычитателей, выход второго регистра соединен с первым входом второго сумматора-вычитателя, вторые входы первого и второго сумматоров-вычитателей соединены с информационными входами соответственно второго и первого и являются входами преобразователя.

Преобразователь предназначен для вычисления функции частного суммы квадратов на сумму двух аргументов.

Недостатком известного преобразователя является то, что он не предназначен для вычисления других функций.

Наиболее близким к заявляемому является цифровой функциональный преобразователь [А.с. 922760 СССР, 1982], включающий блок анализа, первый и второй сумматоры-вычитатели, первый и второй сдвигающие регистры, блок управления и их связи, дополнительно содержащий третий и четвертый сумматоры-вычитатели и блок хранения констант, причем вход блока хранения констант соединен с первым выходом блока управления, второй выход которого соединен с тактовыми входами третьего и четвертого сумматоров-вычитателей, первые входы которых соединены с выходом блока хранения констант, установочный вход которого соединен с входом установки в единицу преобразователя, выход блока анализа соединен с управляющими входами сумматоров-вычитателей, вторые входы которых соединены с входом установки в ноль преобразователя.

Его недостатками являются также низкие функциональные возможности вычисления других функций.

Задача изобретения - совершенствование цифрового функционального преобразователя.

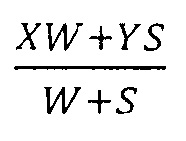

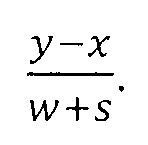

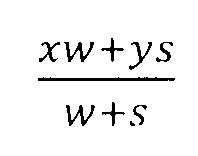

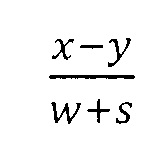

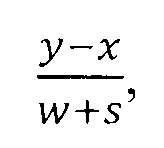

Технический результат - дополнительное расширение возможных для реализации функциональных зависимостей, в частности, за счет функций от четырех аргументов вида  и

и  где X, Y, W, S - аргументы функций.

где X, Y, W, S - аргументы функций.

Технический результат достигается за счет того, что каждый информационный вход цифрового функционального преобразователя расщеплен на два независимых друг от друга информационных входа, два из которых связаны со входами первого и второго сумматоров-вычитателей, а два остальных - со входами первого и второго сдвигающих регистров.

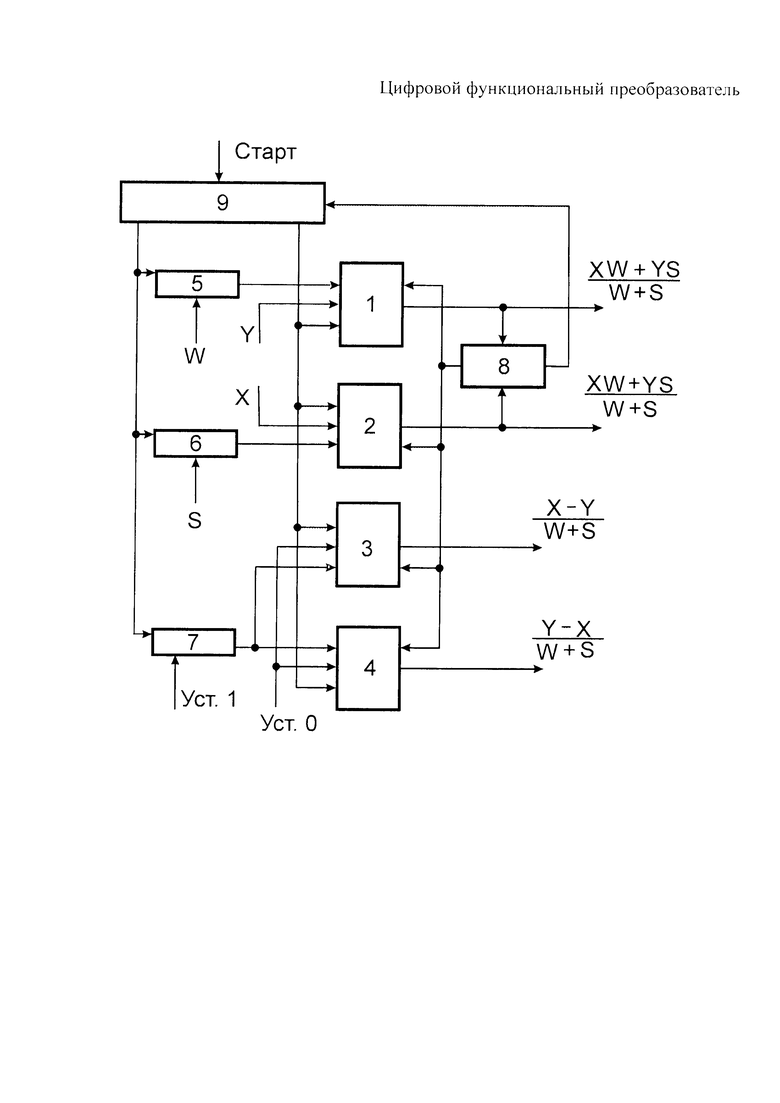

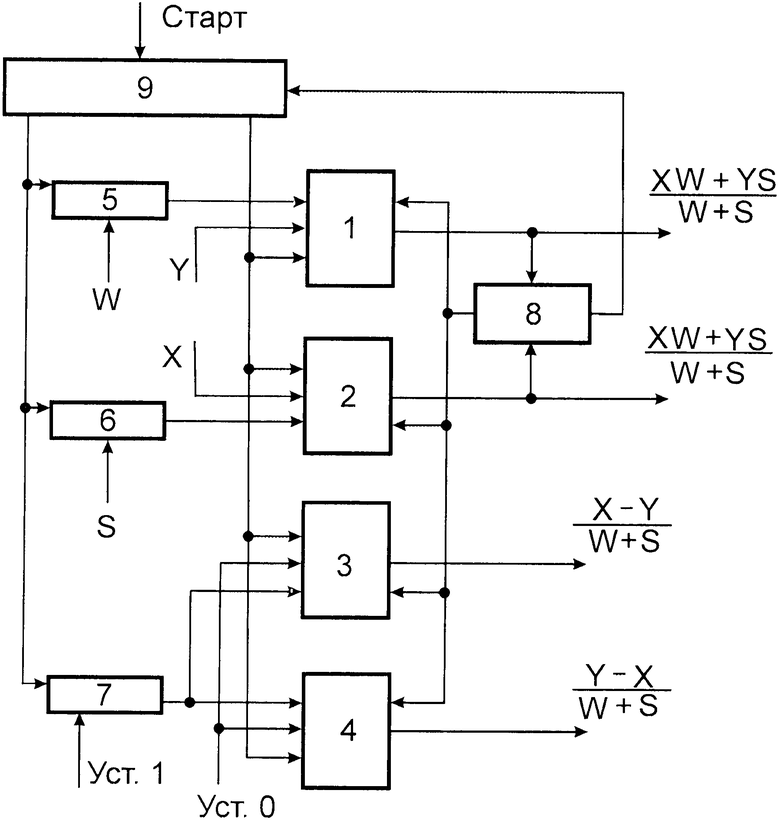

На фиг. приведена блок-схема преобразователя. Преобразователь содержит сумматоры-вычитатели 1-4, сдвигающие регистры 5-6, блок 7 хранения констант, блок 8 анализа и блок 9 управления.

Информационными входами являются четыре входа: X, Y - входы второго и первого сумматоров-вычитателей 2, 1 соответственно и W, S - входы первого и второго сдвигающих регистров 5, 6 соответственно.

Имеются технологические входы: установочный вход блока 7 хранения констант (для записи "1"), стартовый вход (для импульса начала вычисления) и вход "уст. 0" для предварительного сброса в "0" третьего и четвертого сумматоров-вычитателей 3, 4.

Сумматоры-вычитатели 1-4 могут быть выполнены на одноразрядных сумматорах-вычитателях и накопительном сдвиговом регистре. Первый вход одноразрядного сумматора является первым входом сумматора-вычитателя, второй вход которого является информационным входом регистра, выход которого является выходом сумматора-вычитателя. Выход младшего разряда регистра соединен с другим входом одноразрядного сумматора-вычитателя, выход которого соединен с входом старшего разряда регистра. Тактовый вход соединен с входом сдвига регистра. Управляющий вход соединен с входом одноразрядного сумматора-вычитателя, сигнал на котором управляет режимом сложения-вычитания по первому входу. Сумматор-вычитатель может быть реализован также на параллельной комбинационной схеме.

Входами блока 8 анализа являются выходы первого 1 и второго 2 сумматоров-вычитателей, а его выходы соединены с вторым входом блока 9 управления и управляющими входами всех четырех сумматоров-вычитателей 1-4 (режим сложения-вычитания).

Блок 7 хранения констант вида 2-(j+1) может быть реализован на сдвиговом рециркуляционном регистре, старший разряд которого соединен со схемой установки единицы, а на вход сдвига регистра подаются сдвигающие тактовые импульсы (второй выход блока управления 9). Блок 7 хранения констант может быть реализован в виде одностороннего запоминающего устройства.

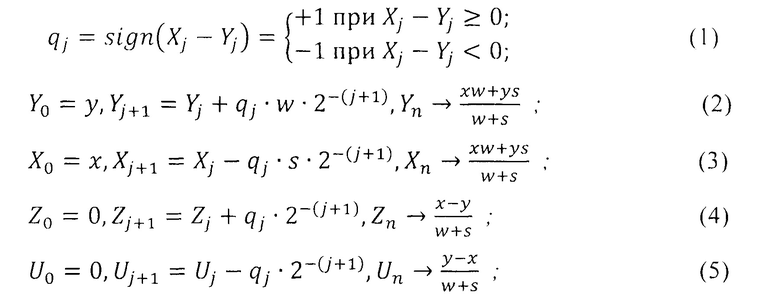

Работа данного цифрового функционального преобразователя основана на одновременном решении системы рекуррентных разностных уравнений в итерационном процессе

где j=0,1,2, …, (n - 1); n - разрядность аргументов.

Сходимость этого итерационного процесса (1) - (5) обеспечена при (w + s) ≥ (x - y).

Все уравнения решаются одновременно (Xn в сумматоре-вычитателе 2, Yn в сумматоре-вычитателе 1, Zn в сумматоре-вычитателе 3, оператор qj определяется в блоке 8 анализа, величина х ⋅ 2-(j+1) получается в сдвигающем регистре 5, величина y ⋅ 2-(j+1) получается в сдвигающем регистре 6, величина 2-(j+1) формируется в блоке 7 хранения констант), причем каждое из уравнений может вычисляться либо последовательно, либо параллельно.

Вычисления в предлагаемом преобразователе осуществляются следующим образом.

Перед началом работы в сумматоры-вычитатели 1, 2 устанавливаются первый и второй аргументы Y и X соответственно, а в сдвигающие регистры 5, 6 - третий и четвертый аргументы W w S соответственно.

При последовательном принципе вычисления в блок 7 хранения констант заносится единица (старший разряд регистра блока 7 хранения констант). На вторые входы сумматоров-вычитателей 3-4 подается сигнал установки нулевого значения. Затем на блок 9 управления подается стартовый импульс. С первого выхода блока 9 управления на сдвигающие регистры 5-6 и блок 7 хранения констант подается тактовый импульс, который сдвигает значения регистров на один двоичный разряд вправо от двоичной запятой. Затем тактовые импульсы с второго выхода блока 9 управления продвигают содержимое сдвигающих регистров 5-6 и регистры блока 7 хранения констант на входы соответствующих сумматоров-вычитателей 1-4. В последних производится сложение или вычитание поступающих операндов с предыдущими значениями.

Режим сложения-вычитания на следующей итерации определяется по разности Xj - Yj в блоке 8 анализа. В случае положительной разности (Xj - Yj ≥ 0) с второго выхода блока анализа выдается сигнал qj (в виде уровня напряжения), который определяет сложение в сумматорах-вычитателях 1 и 3 и вычитание в сумматорах-вычитателях 2 и 4. При отрицательной разности (Xj - Yj) в сумматорах-вычитателях 2 и 4 выполняется сложение, а в сумматорах-вычитателях 1 и 3 выполняется вычитание. Изменение сигнала qj производится после выполнения каждой итерации в момент появления тактового импульса на первом выходе блока 9 управления.

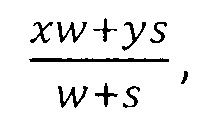

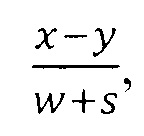

После выполнения n итераций вычисления заканчиваются и блок управления 9 перестает выдавать тактовые импульсы. В сумматорах-вычитателях 1-2 содержится значение функции  в сумматоре-вычитателе 3 содержится значение функции

в сумматоре-вычитателе 3 содержится значение функции  а в сумматоре-вычитателе 4 содержится значение функции

а в сумматоре-вычитателе 4 содержится значение функции

По сравнению с известным предлагаемый преобразователь обладает расширенными функциональными возможностями, поскольку обеспечивает дополнительно вычисление функции  , а также вычисление функций

, а также вычисление функций  и

и  причем время вычисления остается прежним. Расширение функциональных возможностей достигается путем минимальных затрат (добавления только двух сумматоров-вычитателей).

причем время вычисления остается прежним. Расширение функциональных возможностей достигается путем минимальных затрат (добавления только двух сумматоров-вычитателей).

Предлагаемый преобразователь предназначен для аппаратной реализации вычисления указанных функций, которая находит широкое применение в измерительной технике (для подсчета коэффициента модуляции, определения относительных погрешностей), в радиолокационной технике (например, при нормировании сигналов условных ошибок, при автосопровождении и т.д.), в специализированных вычислителях для научных расчетов и управления технологическими процессами и физическими объектами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Цифровой функциональный преобразователь | 1976 |

|

SU748434A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2595906C1 |

| Устройство для вычисления элементарных функций | 1975 |

|

SU553612A1 |

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

Изобретение относится к цифровой вычислительной технике и может найти применение для аппаратной реализации вычисления функций. Технический результат заключается в расширении арсенала средств для вычисления функциональных зависимостей. Цифровой функциональный преобразователь содержит четыре сумматора, два сдвигающих регистра, блок анализа, блок хранения констант, блок управления, четыре входа и четыре выхода, причем сдвигающие регистры связаны с сумматорами-вычитателями, выходы которых связаны с блоком анализа, а его выходы - с блоком управления и всеми сумматорами-вычитателями. 1 ил.

Цифровой функциональный преобразователь, содержащий блок анализа, первый, второй, третий, четвертый сумматоры-вычитатели, первый, второй сдвигающие регистры, блок управления, блок хранения констант, причем выходы первого и второго сдвигающих регистров соединены с первыми входами одноименных сумматоров-вычитателей, выходы блока управления соединены с управляющими входами обоих сдвигающих регистров, блока хранения констант и тактовыми входами всех сумматоров-вычитателей, выход блока хранения констант связан с первыми входами третьего и четвертого сумматоров-вычитателей, выходы первого и второго сумматоров-вычитателей связаны со входами блока анализа, выходы которого соединены с блоком управления и управляющими входами всех четырех сумматоров-вычитателей, выходы которых являются выходами цифрового функционального преобразователя, отличающийся тем, что каждый информационный вход цифрового функционального преобразователя расщеплен на два независимых друг от друга информационных входа, причем два из которых связаны с входами первого и второго сумматоров-вычитателей, а два остальных - со входами первого и второго сдвигающих регистров.

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| ЦИФРОАНАЛОГОВЫЙ ПРЕОБРАЗОВАТЕЛЬ | 2009 |

|

RU2433528C2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Огнетушитель | 0 |

|

SU91A1 |

Авторы

Даты

2018-01-24—Публикация

2017-02-06—Подача