(54) УСТРОЙСТВО ДЛЯ ИЗВЛЕЧЕНИЯ КОРНЯ ТРЕТЬЕЙ СТЕПЕНИ ИЗ ЧАСТНОГО И ПРОИЗВЕДЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления корня пятой степени | 1976 |

|

SU691848A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU911522A1 |

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Устройство для вычисления степенных функций | 1977 |

|

SU682895A1 |

| Цифровой функциональный преобразователь | 1979 |

|

SU922733A2 |

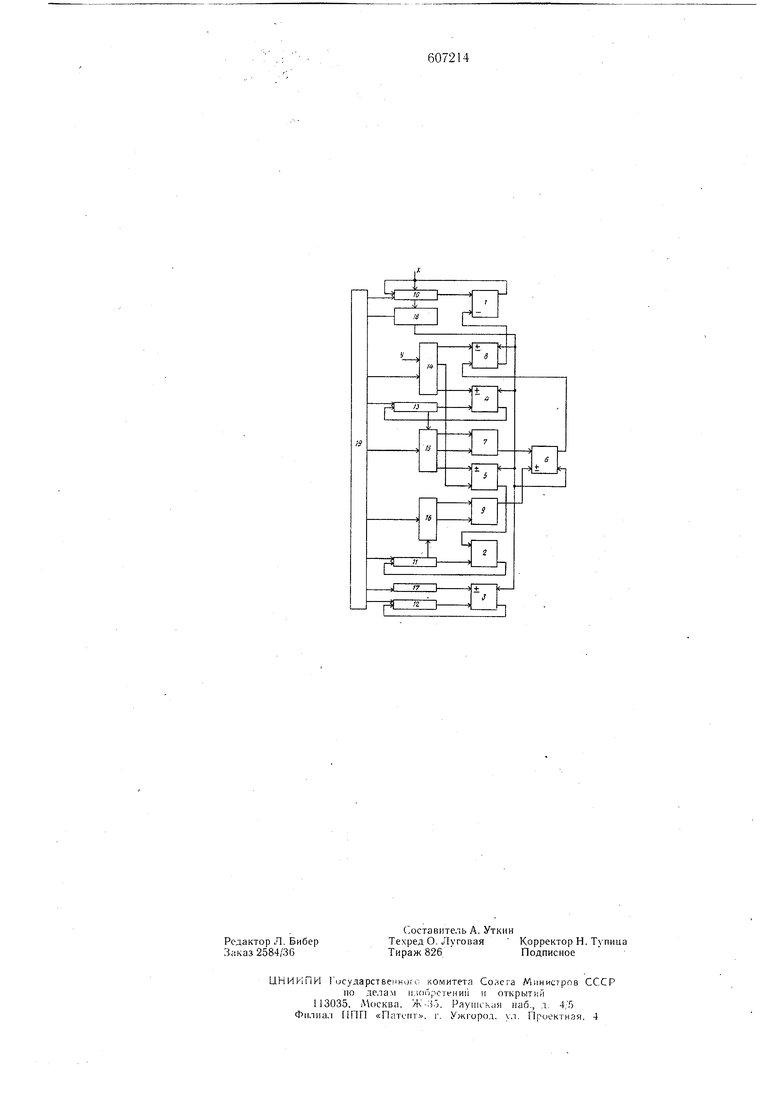

Изобретение относится к области цифровой вычислительной техники и может найти применение для аппаратной реализации вычисления функций кубического корня из частного двух аргументов, из произведения одного аргумента на квадрат второго или из квадрата аргумента и из аргумента. В настоящее время указанные функции вычисляются на ЭВМ общего назначения при использовании стандартных подпрограмм. Известные способы вычисления требуют для реализации сложных арифметических устройств и определяют большие затраты машинного времени. Известно устройство для извлечения корня п-степени, содержащее регистры сдвига, сумматоры, регистры, коммутаторы и блок управления 1. Известное устройство не предназначено для вычисления кубического корня из частного или произведения. Наиболее близким по технической сущности к изобретению является известное устройство для вычисления кубического корня, содержащее пять регистров сдвига, блок формирования констант, семь сумматоров-вычитахелей, блок анализа сходи.мости, блок тфавления, причем выходы первых четырех регистров сдвига соединены соответственно с первыми входами первых четырех сумматоров-вычитателей, выходы которых соответственно соединены с первыми входами этих регистров сдвига, второй выход первого регистра сдвига соединен с входами управления третьего, четвертого, пятого и шестого сум.маТоров-вычитателей, а второй выход - с входом блока управлеция, второй выход пятого регистра сдвига соединен через пятый сумматор-вычитатель со вторым входом второго сумматора-вычитателя, второй вход третьего сумматора-вычитателя соединен с выходом блока формирования констант, первый вход шестого сумматора-вычитателя соединен с выходом седьмого.сумматора-вычитателя 2. Известное устройство предназначено только для вычисления кубического корня из одного аргумента. Целью изобретения является расширение функциональных возможностей, т.е. вычисление кубического корня из частного двух apiyментов, из произведения одного аргумента на квадрат второго или из квадрата аргумента и из аргумента. Это достигается тем, что в предлагаемое устройство введены восьмой и девятый сумматоры-вычитатели и шестой и седьмой регистры сдвига, два выхода шестого регистра сдвига соединены соответственио со вторыми входами четвертого и восьмого сумматоров-вычитателей, а третий выход - с входом пятого сумматора-вычигателя, второй выход второго регистра сдвига соединеи с входом седьмого регистра сдвига, выходы которого соединены с входами девятого сумматора-вычитателя; выход которого соединен с вторым входом шестого сумматора-вычитателя, выход которого сое динен с первым входом восьмого сумматоравычитателя, выход которого соединен с вторым входом первого сумматора-вычитателя, второй выход четвертого регистра сдвига соединен с входом пятого регистра сдвига, второй и третий выходы которого соединены с соответствуюшими входами седьмого сумматора-вычитателя, вход управления восьмого сумматора-вычитателя соединен с выходом блока анализа сходимости, выходы блока управления соединены с соответствующими входами регистров сдвига и блока формирования констант. На чертеже представлена блок-схема описываемого устройства для извлечения корня третьей степени из частного и произведения, содержащего однорядные сумматоры-вычитатели 1-9 комбинационного типа, регистры сдвига 10-16, блок 17 формирования констант, блок 18 анализа сходимости и блок 19 управления. Входы сумматоров-вычитател й 1, 2, 3 и 4 соединены с входами регистров сдвига 10-13, выходы которых соответственно соединены с первыми входами указанных сумматоров-вычитателей. Второй выход первого регистра сдвига 10 соединен с входом блока 18 анализа сходимости, первый выход которого соединен с входами управления сумматоров-вычитателей 3, 4, 5, 6 и 8, а второй выход соединен с входом блока 19 управления. Второй выход второго регистра сдвига 11 соединен с входом седьмого регистра сдвига 16, два выхода которого соединены с входами сумматора-вычитателя 9. Выход последнего соединен со вторым входом сумматора-вычитателя 6. Второй выход четвертого регистра сдвига 13 соединен с входом пятого регистра сдвига 15, первый выход которого соединен со вторым входом сумматора-вычитателя 5, а второй и третий выходы соединены с входами сумматора-вычитателя 7. Выход сумматора-вычитателя 7 соединен с входом сумматора-вычитателя 6. Первый и второй выходы шестого регистра сдвига 15 соединены соответственно со вторыми входами сумматора-вычитателя 4 и 8. Третий выход щестого регистра сдвига 15 соединен с входом сумматора-вычитателя 5, выход которого соединен со вторым входом сумматора-вычитателя 2. Выход сумматора-вычитателя 6 соединен с входом сумматора-вычитателя 8. Выход сумматора-вычитателя 8 соединен со вторым входом сумматора-вычитателя 1. Выход блока 17 формирования констант соединен с вторым входом сум.матора-вычитателя 3. Выходы блока уггравления соединены с входами регистров сдвига 10-13 блока 17 формирования констант, регистров сдвига 15-17. Блок 17 формирования констант вида 2 может быть выполнен, например, в виде регистра сдвига или одностороннего запоминающего устройства. Блок 18 анализа сходимости предназначен для анализа сходимости процесса вычисления и определения знака содержания в первом регистре сдвига 10. Блок 18 анализа сходимости содержит, например, блок сравнения кодов, триггеры и логические элементы. Блок 19 управления предназначен для формирования тактовых (сдвигающих) и.1пульсов и содержит, например, генератор импульсов, счетчики, логические элементы. Входами устройства являются входы первого регистра сдвига 10 для аргумента X и входы шестого регистра сдвига 16 для аргумента Y. Выходами устройства для функции X/Y является выход регистра сдвига 12, для функции VXY - выход четвертого регистра сдвига 13, для функции - выход второго регистра сдв-ига 11. Процесс вычисления указанных функций основан на одновременном решении в итерационном процессе системы разностных рекуррентных соотношений, например, для двоичной системы счисления: Vj,(,-3-2- - V,.,j.-2,, s,g«v, (l.;p..v.o Uj i Uj qjWj-2.-2- - Y-2-J tj +qi-2где j 0, 1, 2,..., n, П - число разрядов одного из аргументов. Устройство работает следующим образом. Первоначально в первый регистр сдвига 10 заносится значение аргумента X, в регистры сдвига 11 -13 - нулевые значения, а в регистр сдвига 16 - значение аргумента Y. Включается генератор импульсов в блоке 19 управления. В любой j-й итерации с выходов блока 19 управления выдаются серии (последовательности) тактовых импульсов для сдвига значений в регистрах сдвига 10-16 и выборки очередной константы из блока 17 формирования констант. Результаты каждой итерации записываются с выходов сумматоров-вьшитателей 1, 2, 3 и 4 младщими разрядами вперед в освобождающиеся при сдвиге старшие разряды регистров сдвига 10-13 и продвигаются в сторону младших разрядов. В конце каждой итерации в блоке 18 анализа сходимости определяется по знаку содержания в регистре сдвига 10 очередная цифра qj, которая в виде сигнала с первого выхода блока 18 анализа выдается на входы управления сумматоров-вычитателей 3, 4, 5, 6 и 8. При qj +1 сумматоры-вычитатели 3-6,8 работают в режиме сложения. При qj -1 сумматоры-вычитатели 3-6,8 работают в режиме вычитания. Сумматор-вычитатель 1 работает только в режиме вычитания. Сумматоры-вычитатели 2, 7 и 9 работают только в режиме сложения. В случае, когда содержание регистра сдвига 10 равно нулю, блок 18 анализа сходимости выдает сигнал останова блока 19 управления, который перестает выдавать тактовые импульсы на следующей итерации, так как процесс вычисления закончен. В perHCTjDe сдвига 12 находится значение функции VX/Y jB perHCTpe сдвига 11 - значение функции , в Ёегистре сдвига 13 - значение функции YXY . Когда значение аргумента Y 1, в регистре сдвига 11 находится значение функции {Х , в регистрах сдвига 12 и 13 - значение функции /Х. .. Когда зна-. чение аргумента X 1, в регистре-сдвига 12 находится значение функции 1/Y, в. регистре сдвига 11 - значение функции регистре сдвига 13 - значение функцииVY, . Цикл вычисления указанных функций с погрешностью половины младшего разряда состоит из п -f 1 итераций. Каждая итерация включает параллельное вычисление всех соотношений алгоритма. Причем каждое соотношение вычисляется последовательным путем за п + m тактов, где гп - число дополнительных (защитных) разрядов регистров для компенсации погрешности усечения чисел при сдвиге. Максимальное время вычисления функций в тактах равно .c п + п (m + 1) + m. Для п 12Тлл«,: 327 тактов, что значительно меньше времени вычисления известными способами при сравнимых затратах аЬпаратуры. Однако благодаря асинхронному режиму работь для большинства значений аргументов время-вычисления еще меньше. Достоинством предложенного цифрового функционального преобразователя является возможность вычисления одновременно трех сложных функций за время вычисления одной -L элементарной функции в специализированном устройстве. Предлагаемый цифровой функциональный преобразователь с унифицированной параллельно-последовательной структурой обладает простотой схемных решений из стандартных цифровых элементов и относительно высокой однородностью и регулярностью, что позволяет полностью .использовать возможности современной интегральной технологии для реализации устройства в виде одной БИС. Предлагаемое устройство совмещает, противоречивые требования повышения надежноети, быстродействия, унификации и технологичности структуры, снижения аппаратурных затрат. Использование предложенного устройства позволит сократить расходы на разработку устройств для вычисления аналогичных задач. Формула изобретения Устройство для извлечения корня третьей степени из частного и произведения, содержашее регистры сдвига, блок формирования констант, сумматоры-вычитатели, блок анализа сходимости, блок управления, причем выходы nepBtix четырех регистров сдвига соединены собтветственно с первыми входами первых четырех сумматоров-вычитателей, выходы которых .соединены соответственно с первыми входами регистров сдвига, второй выход первого регистра сдвига соединен, с входо.м блока анализа сходимости, первый выход которого соединен с входами управления третьего, четвертого, пятого и шестого сумматоров-вычитателей, а второй выход - с входо.м блока управления, второй выход пятого регистра сдвига соединен через пятый сумматор-вычитатель с вторым входом второго сумматора-вычитателя, второй вход третьего сумматора-вычитателя соединен с выходом блока формирования констант, первый вход шестого сумматора-вычитателя соединен с выходом седьмого сумматора-вычитателя, отличающееся тем, что, с целью расширения функциональных возможностей, в устройство введены восьмой и девятый сум.маторы-вычитатели и шестой и седьмой регистры сдвига, два выхода шестого регистра сдвига соединены соответственно со вторыми входами четвертого и восьмого сумматоров-вычитателей, а третий выход - с входом пятого су.мматора-вычитателя, второй выход второго регистра сдвига соединен с входом седьмого регистра сдвига, выходь которого соединены с входами девятого сумматора-вычитателя, выход которого соединен со вторым входом шестого сумматора-вычитателя, выход которого соединен с первым входом восьмого су.мматоравычитателя, выход которого соединен со вторым входом первого с:умматора-вычитателя, второй выход четвертого регистра сдвига соединен с входом пятого регистра сдвига, второй и третий выходы которого соединены с соответствующими входами седьмого cyммaтopa-вычитaтeля вход управления восьмого сумматора-вычитателя соединен с выходом блока анализа сходимости, выходы блока управления соединены с соответствуюшими входами регистров сдвига и блока формирования констант. Источники информации, принятые во внимание при экспертизе: 1.Авторское свидетельство СССР № 491946, М. КЛ.2 G 06 F 7/38, 1974. 2.Авторское свидетельство СССР № 516037 кл. G 06 F 7/38, 1973.

Авторы

Даты

1978-05-15—Публикация

1976-03-24—Подача