Изобретение относится к цифровой вычислительной технике, может быть использовано для аппаратной реализации операций вычисления функций в устройствах автоматики и вычислительной техники.

По основному авт. св. № 633016 известно арифметическое устройство, содержащее блок управления, выходы которого подключены к управляющим входам регистров сдвига, первые выходы первого, второго и третьего регистров сдвига соединены соответственно с первыми входами первого, йторого и третьего сумматоров-вычитателей, выходы которых соединены с первыми входами соответствую1цих регистров сдвига, вторые выходы второго и третьего регистров сдвига соединены соответственно с первыми входами четвертого и пятого регистров сдвига, выход четвертого регистра сдвига соединен со вторыми входами первого и второго -сумматоров-вычитатепей, выход пятого регистра сдвига - со вторым входом третьего сумматора-вычитателя, вход блока анализа сходимости вычисления - со вторы 4 выходом первого регистра сдвига, первый и второй внкоды - с соответствуютими входами

блока управления, третий выход с управляющими входами сунматороввычитателей, причем блок анализа сходимости вычисления содержит две схемы сравнения, выходы которых подключены соответственно ко входам триггеров, выходы которых подключены соответственно к первым входам элементов И, вторые входы которых подклю10чены тактовой шине, выходы элементов И подключены соответственно к первому и второму выходам блока, входы схем сравнения и первый вход третьего-элемента И являются входами

15 блока анализа сходимости, второй вход третьего элемента И подключен к тактовой шине, выход третьего элемента И - через третий триггер - к третьему выходу блока анализа сходимости

20 вычисления Cl.

Недостатками арифметического устройства являются ограниченные функциональные возможности, так как устройство предназначено для вычисления только одной функции - частного от деления произведения двух аргументов на третий.

Целью изобретения является расширение класса решаемых задач за счет

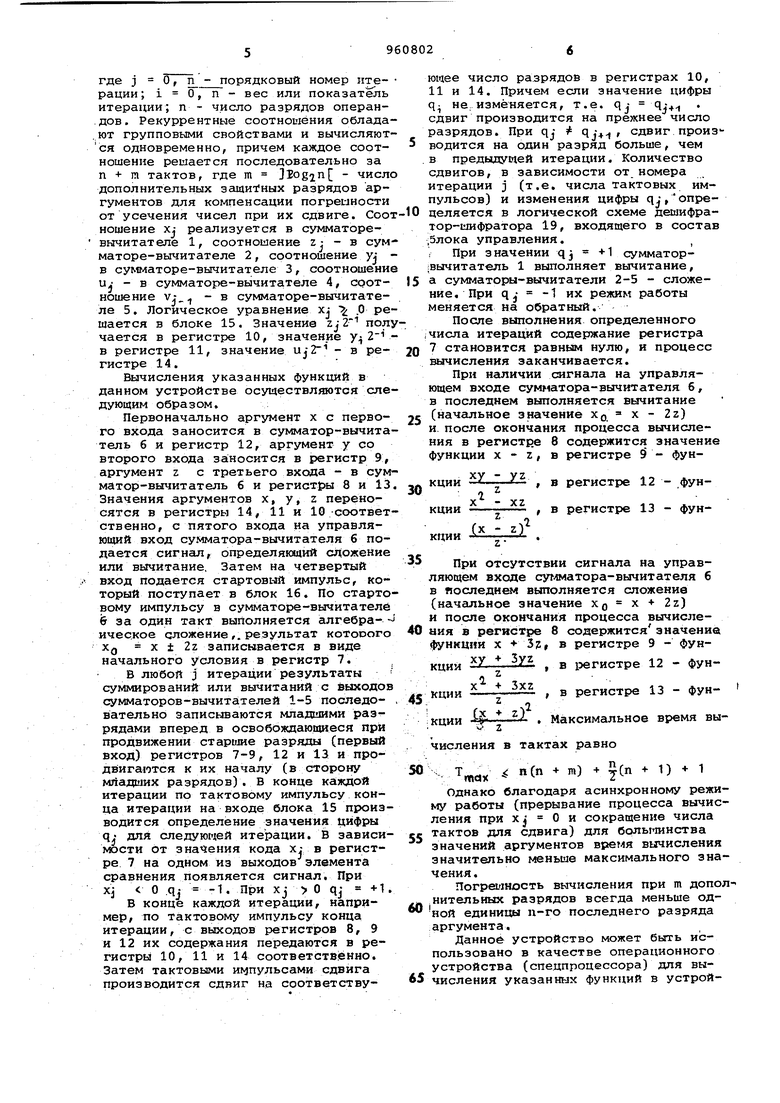

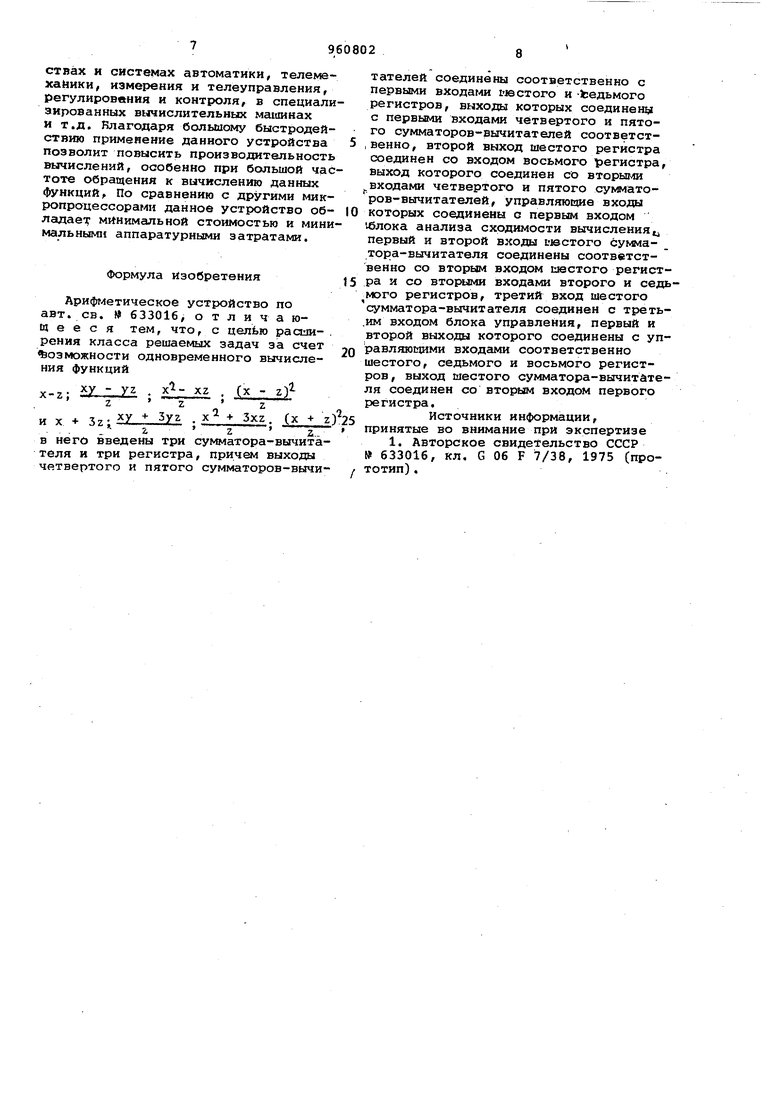

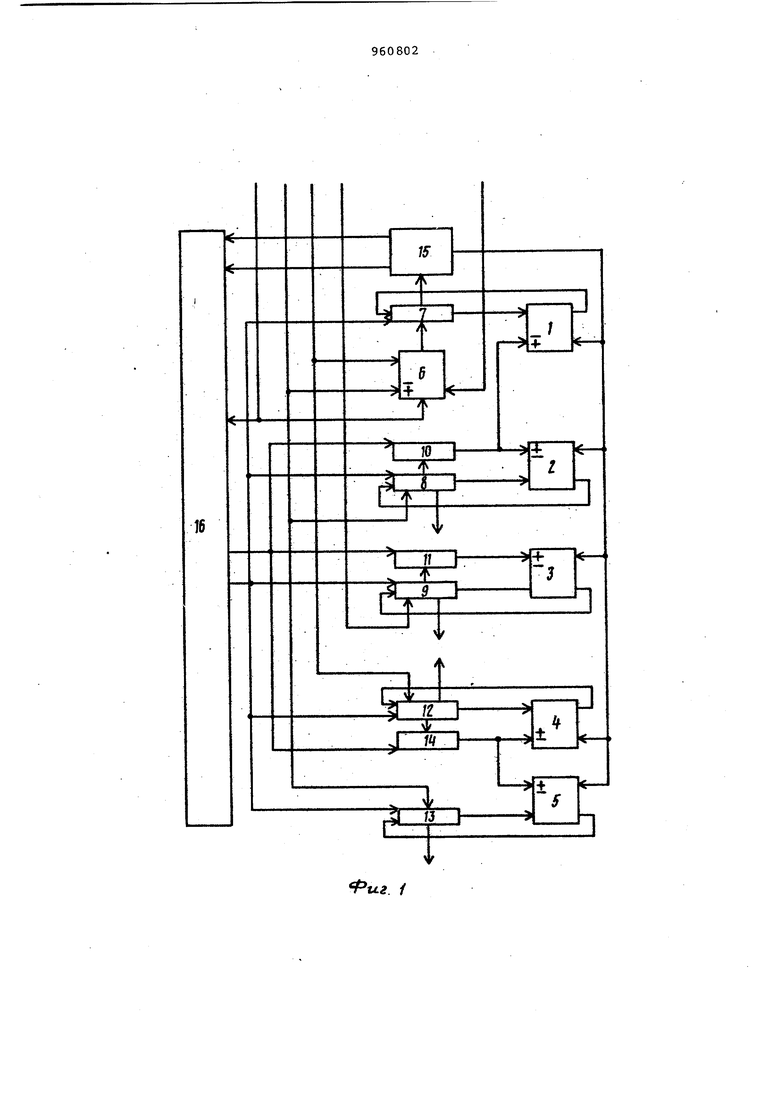

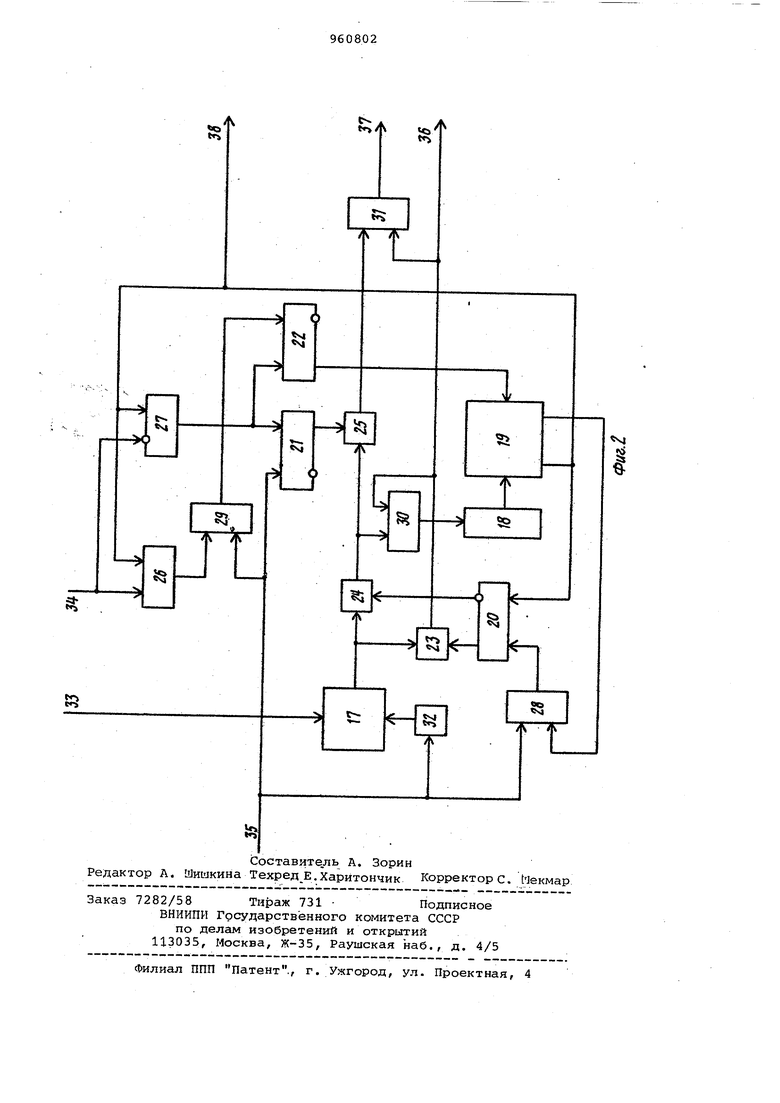

30 возможности одновременного вычисления функций x-z; ,г ху + 3yz и X 3z; (X - z) Поставленная цель достигается тем, что в устройство дополнительно введены три сумматора-вычитатепя и три ре-1 гистра, причем выходы четвертого и пятого сумматоров-вычитателей соеди нёны соответственно с первыми входами шестого и седьмого регистров, выходы которых соединены с первыми вхо-} дами четвертого и пятсяго сумматороввычитателей соответственно, второй выход шестого регистра соединен со входом восьмого регистра, выход кото рого соединен со вторыми входами чет вертого и пятого суивиаторов- вычитате лей, управляющие входы Кото1ялх соеди нены с первым выходом блока анализа, первый и второй входы шестого сумматора-вычитателя соединены соответственно со вторым входом шестого регис ра и со вторыми входами второго и седьмого регистров, третий вход шестого су1Ф атора-вычитателя соединен с третьим входом блока управления, лервый и второй выходы которого соединены с управляющими входами соответственно iflecToro, седьмого и восьмого регистров выход шестого сумматора-вычитателя соединен со вторым входом первого регистра. Такое схемо-техническое решение позволяет за одно и то же время вычислить четыре сложных функции. На фиг. 1 представлено арифметическое устройство; на фиг. 2 - одна из возможных схем блока управления. Схема (фиг. 1) содержит cyм iaтopы вычитатели 1-6, регистры 7-11 сдвига регист 12-14, блок 15 анализа сходимости вычислений и блок 16 управле ния. Блок 16 управления СФиг. 2J прёД назначен для синхронизации устройства и может содержать управляемый генератор 17 тактовых импульсов, работающий в старт-стопном режиме, счет-, чик 18, дешифратор 19, триггеры 2022, элементы И 23-27, элемента ИЛИ 28-31, элемент 32 задержки. Первый вход 33 от блока 15 для сигнала О соединен с остановочным входом генератора 17. Второй вход 34 от блока 15 для сигнала q; соединен со входами элементов И 26 и 27, причем вход элемента И 27 является инвертирующим. Третий вход 35 от третьего входа устройства соединен со входом пуска генератора 17. Первый выход 36 соединяется с управляющими входами регистров 7-9, 12 и 13 для подачи на них последовательности тактовых импульсов, необходимых для продвижения их содержаний на первые входы сумматоров-вычитателей 1-5. Второй выход 37 соединяется с управляющими входами регистров 10, 11 и 14 для подачи на них последовательности тактовых импульсов для сдвига и последовательности тактовых импульсов для продвижения предварительно сдвинутых содержаний на вторые входы сумматоров-вычитателей 1-5, причем вторая последовательность снимается с первого выхода 36 через элемент ИЛИ 31. Третий выход 38 может быть соединен с третьим входом блока 15 для подачи тактового импульса конца итерации с первого выхода дешифратора-шифратора 19, второй выход которого для тактового импульса конца сдвига соединен через элемент ИЛИ 28 с установочным входом триггера 20. (Соединение выхода 38 блока 16 управления с входом блока 15 на фиг. 1 не приведено, поскольку при другом варианте выполнения блока 15 в этой связи нет необходимостиJ. Вычисление функций в данном устройстве основано на одновременном решении в итерационном процессе системы разностных рекуррентных соотношений (алгоритма вычислрния) :

где j О, n - порядковый номер нтерации; i О, n - вес или показатель итерации; n - число разрядов операн.дов. Рекуррентные соотноиюния облада.ют групповыми свойствами и вычисляются одновременно, причем каждое соотношение решается последовательно за n + m тактов, где m Iog2n - число дополнительных защит ных разрядов аргументов для компенсации погреиности от усечения чисел при их сдвиге. Соот ношение Xj реализуется в сумматоревычитателе 1, соотношение Z: - в сумматоре-вычитателе 2, соотношение у; в cy лaтope-вычитaтeлe 3, соотношение Uj - в сумматоре-вычитателе 4, сротношение v: - в сумматоре-вычитателе 5. Логическое уравнение х; .0 решается в блоке 15. Значение z; полу чается в регистре 10, значение регистре 11, значение Uj2 - в регистре 14.

Вычисления указанных функций в данном устройстве осуществляются следующим образом.

Первоначально аргумент х с первого входа заносится в сумматор-вычитатель б и регистр 12, аргумент у со второго входа за:носится в регистр 9, аргумент z с третьего входа - в сумматор-вычитатель 6 и регистры 8 и 13. Значения аргументов х, у, 2 переносятся в регистры 14, 11 и 10 соответственно, с пятого входа на управляющий вход сумматора-вычитателя 6 подается сигнал, определяющий сложение или вычитание. Затем на четвертый вход подается стартовый импульс, который поступает в блок 16. По стартовому импульсу в сумматоре-вычитателе & за один такт выполняется алгебра- ическое сложение,. результат котового XQ X ± 2z записывается в виде начального условия в регистр 7.

В любой j итерации результаты суммирований или вычитаний с выходов сумматоров-вычитателей 1-5 последовательно записываются младшими разрядами вперед в освобождающиеся при продвижении старшие разряды (первый вход) регистров 7-9, 12 и 13 и продвигаются к их началу (в сторону мйадших разрядов). В конце каждой итерации по тактовому импульсу конца итерации на входе блока 15 производится определение значения Цифры q. для следующей итерации. В зависимости от значения кода х; в регистре 7 на одном из выходов элемента сравнения появляется сигнал. При

О .qj -1, При Xj О qj +1,

XJ

В конце каждой итерации, например, по Тактовому импульсу конца итерации, с выходов регистров 8, 9 и 12 их содержания передаются в регистрь 10, 11 и 14 cooTBeTCTBieHHO, Затем тактовыми и)пульсами сдвига производится сдвиг на соответствующее число разрядов в регистрах 10, 11 и 14. Причем если значение цифры Я- не, изменяется, т.е. qj q,;+ сдвиг производится на прежнее число разрядов. При qj Ф сдвиг производится на один разряд больше, чем .в предыдущей итерации. Количество сдвигов, в зависимости от номера итерации j (т,е, числа тактовых импульсов) и изменения цифры q;,onpe0 целяется в логической схеме дешифратор-шифратора 19, входящего в состав ,5лока управления.

При значении qj + сумматоргвычитатель 1 выполняет вычитание, 5 а сумматоры-вычитатели 2-5 - сложение. При qj -1 их режим работы меняется на обратный.

После выполнения определенного .числа итераций содержание регистра 0 7 становится равным нулю, и процесс вычисления заканчивается.

При наличии сигнала на управляющем входе сумматора-вычитателя 6, в последнем выполняется вычитание 5 (начальное значение Хд х - Zz) и после окончания процесса вычисления в регистре 8 содержится значение функции X - Z, в регистре S - фун , в регистре 12 - функции

30

кции --I- , в регистре 13 - фун(X - Z)

кции

z35 При отсутствии сигнала на управляющем входе сумматора-вычитателя 6 в последнем выполняется сложение (начальное значение XQ х 2z) и после окончания процесса вычисле40 аия в регистре 8 содержится значение функции X Зг, в регистре 9 - функций -/. .У.. , в регистре 12 - функции , В регистре 13 - фун

. 2)

кции , Максимальное время вычисления в тактах равно

тах п(п -ь т) + 5(п -- 1) + 1

Однако благодаря асинхронному режиму работы (прерывание процесса вычисления при х О и сокращение числа

тактов ДЛЯ сдвига) для большинства значений аргументов время вычисления значительно меньше максимального значения,

norpeiiHOCTb вычисления при m дополнительных разрядов всегда меньше одной единицы п-го последнего разряда аргумента.

Данное устройство может быть использовано в качестве операционного устройства (спецпроцессора) для вычисления указанных функций в устройствах и системах автоматики, телемехайики, измерения и телеуправления, регулироввния и контроля, в специализированных вычислительных маишнах и т.д. Благодаря большому быстродействию применение данного устройства позволит повысить производительность вычислений, особенно при большой частоте обращения к вычислению данных функций. По сравнению с другими микропроцессорами данное устройство облапает минимальной стоимостью и минимальными аппаратурными затратами.

Формула Изобретения

Арифглетическое устройство по авт. св. 633016, отличающееся тем, что, с целЬю расыи- . рения класса решаемых задач за счет возможности одновременного вычисления функций

тг -, ХУ yZ . XZ . (Х - Z)

X-Z,Z -Г

и X + 3z- У У . (X + г

Z Z2

в него введены три сумматора-вычитателя и три регистра, причем выходы четвертого и пятого сумматоров-вычитателей соединены соответственно с первыми входами tJscToro и -Седьмого регистров, выходы которых соединены с первыми входами четвертого и пятого сумматоров-внчитателей соответст,венно, второй выход шестого регистра соединен со входом восьмого регистра, выход которого соединен со вторы1 ш входами четвертого и пятого сумматоров-вычитателей, управляющие входы которых соединены с первым входом 1блока анализа сходимости вычисления первый и второй входы иэстого dyivwaтора-вычитателя соединены соответственно со вторым входом шестого регистра и со вторами входами второго и седьмого регистров, третий вход шестого сумматора-вычитателя соединен с треть.им входом блока управления, первый и второй выходы которого соединены с управляющими входами соответственно шестого, седьмого и восьмого регистров, выход шестого сумматора-вычитателя соединен со вторым входом первого регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 633016, кл. G 06 F 7/38, 1975 (прототип) .

/

| название | год | авторы | номер документа |

|---|---|---|---|

| Арифметическое устройство | 1977 |

|

SU728127A2 |

| Устройство для извлечения корня третьей степени из частного и произведения | 1976 |

|

SU607214A1 |

| Устройство для вычисления экспоненциальной функции | 1977 |

|

SU711578A2 |

| Устройство для вычисления логарифмической функции | 1973 |

|

SU541167A1 |

| Арифметическое устройство | 1980 |

|

SU903868A2 |

| Устройство для вычисления тригонометрического тангенса | 1973 |

|

SU537344A1 |

| Устройство для вычисления корня четвертой степени | 1975 |

|

SU561184A1 |

| Устройство для вычисления гиперболического тангенса | 1973 |

|

SU526890A1 |

| Арифметическое устройство | 1975 |

|

SU633016A1 |

| Устройство для вычисления кубического корня | 1973 |

|

SU516037A1 |

Авторы

Даты

1982-09-23—Публикация

1980-06-19—Подача