деления отклонения частоты импульсной последовательности от заданной, п

Целью изобретения является повышение точности определения отклонения частоты,

С этой целью в устройство для определения отклонения частоты импульсной последовательности от заданной, содержащее R - S триггеры, нулевые входы первого и второго из которых подключены к нулевому выходу третьего триггера и к первым входам пер.вого и второго элементов й-НЕ, соединенных выходами docTBeTCTBeHHO с единичным и нулевым входами четвертого триггера, а второй вход первого элемента И-НЕ подключен к единичному выходу первого триггера, соединенного нулевым выходом со вторым входом второго элемента И-НЕ, третий вход которого подключен к единичному выходу второго триггера, соединенного нулевым выходом с третьим входом первого элемента И-НЕ, дополнительно введена пятый и шестой триггеры и элемент задержки, соединенный входом с нулевым выходом третьего триггера,

единичным входом пятого триггера и ;

первым единичным входом шестого тр1иггера и подключенный выходом к единичному входу первого триггера и нулевому входу пятого триггера, единич- , ный выход которого соединен с единичным входом третьего триггера, подключенного первым нулевым входом к единичному выходу шестого, а вторым нулевым, входом - к входу устройства и второму единичному входу шестого триггера, единичный выход которого соединен с единичным входом второго триггера, а нулевой вход шестого триггера подключен к нулевому выходу пятого триггера.

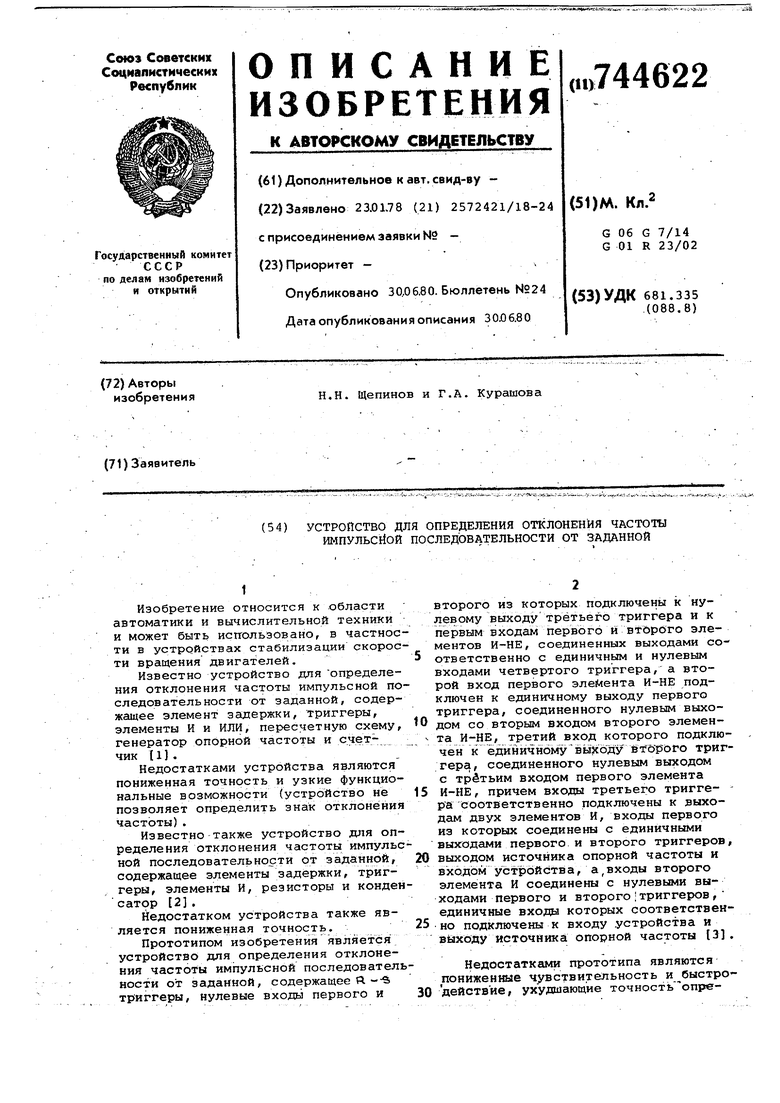

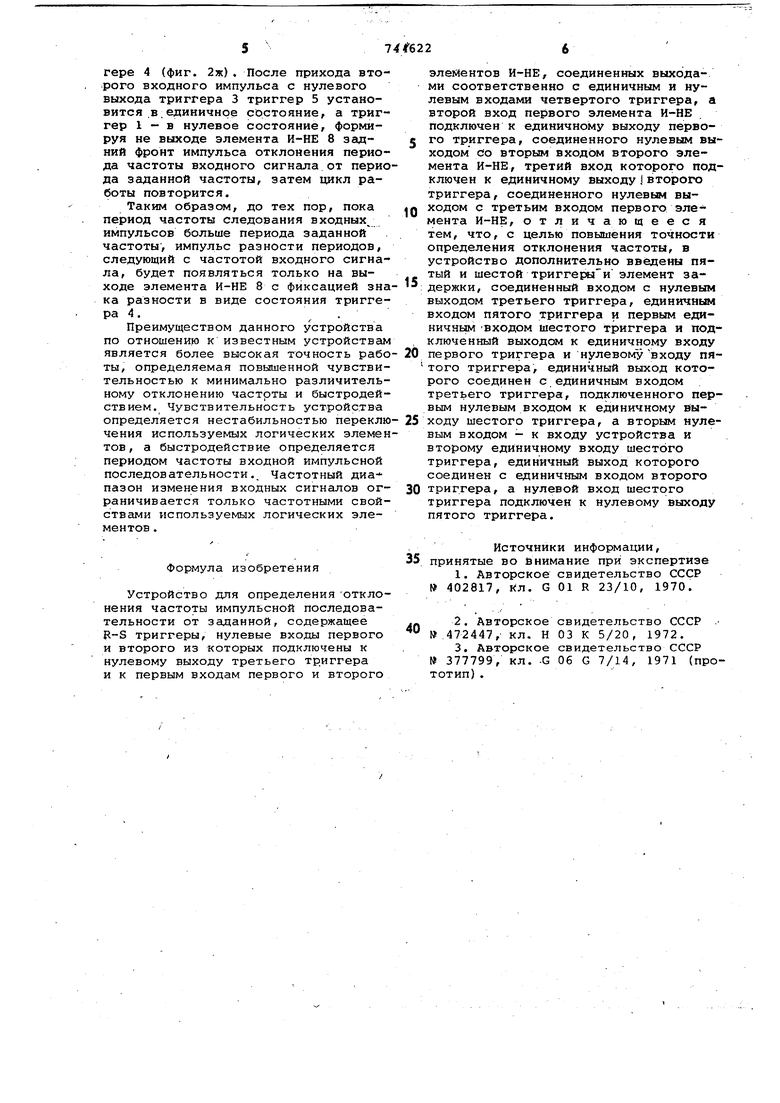

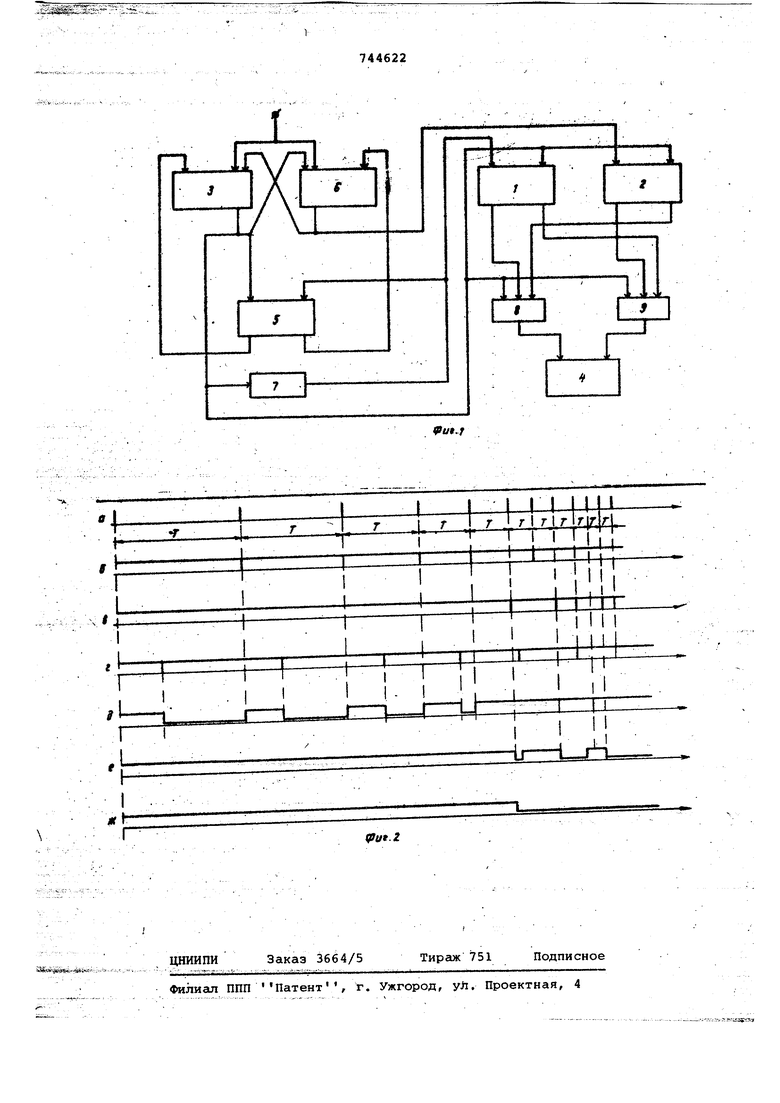

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг 2 - временная диаграмма работы. ,

.Устройство содержит первый, второй, третий, четвертый, пятый и шестой л -а. триггеры 1-6, элемент 7 задержки и первый и второй элементы И-НЕ 8 и 9. Третий, пятый и шестой триггеры 3, 5 и 6 образуют триггер со счетным входом, выполненный по схеме трех триггеров, причем пятый триггер 5 является основным триггером этого .триггера со Очетным входом, а третий и шестой триггеры 3 и б - коммутирующими триггерами.

Предлагаемое устройство работает следующим образом.

Импульсы контролируемой импульсной последовательности (фиг. 2а) подаются на второй нулевой вход триггера 3 и второй единичный вход триггера б, представ ляющие собой счетный вход счетного трриггера по схеме трех триггеров 3, 5и б. При появлении им пульса иа нулевом выходе триггера 3

(фиг. 2б) триггер 5 устанавливаете в единичное состояние, а триггеры I и 2 устанавливаются в нулевое состояние, при этом логические элементы; И-НЕ 8 и 9 предохраняют от воздейсте ВИЯ паразитного сигнала одновременного переброса триггеров 1 и 2 .триггер 4, который фиксирует знак отклонения исследуемой частоты. . Если период Т частоты следования

Q входных импульсов меньше периода заданной частоты (период заданной частоты равен длительности задержки в элементе задержки 7), то следующий импульс входногосигнала появится на единичном выходе триггера 6 (фиг. 2в) раньше, чем импульс на выходе элемента 7 (фиг. 2г). Этот импульс с выхода триггера 6 установит триггер 2 в единичное состояние. При этом на выходе элемента И-ИЕ 9 (фиг. 2е) начнется формирование длительности импульса отклонения частоты следования входного сигнала от заданной с фиксацией соответствующего знака отклонения в виде состояния триггера 4

5 (фиг. 2ж). После прихода с выхода элемента 7 задержки импульса, задержанного на период заданной частоты. На нулевой вход основного триггера 5, триггера со счетным входом, триггер

Q 5 через цепь, образованную триггерами 6 и 3, переключится в нулевое состояние, а триггер 1 импульсом с выхода элемента 7 установится в единичное состояние, формируя на выходе

r элемента И-НЕ 9 задний фронт импульса отклонения входного сигнала от периода заданной частоты. Последующий импульс входного сигнала появится вновь на нулевом выходе триггера 3, и далее цикл работы повторится. Та0 КИМ образом, до тех пор, пока период частоты следования входных импульсов будет меньше периода задан.ной частоты, импульс разности периодов , следующий с заданной частотой,

5 будет появляться на выходе элемента И-НЕ 9 (фиг. 2е) с фиксацией знака разности в виде состояния триггера 4.

Если период частоты следования

Q входных импульсов больше периода за- данной частоты, то импульс на выходе элемента 7 задержки появится раньше импульса входного сигнала с единич- ного выхода триггера 6 и установит триггер 5 в нулевое состояние, а

триггер б - в единичное состояние, а вследствие этого запретит появление импульса входной частоты с единичного выхода триггера б. При этом импульс с выхода элемента 7 задержки

О установит в единичное состояние триггер 1, формируя на выходе элемента И-НЕ 8 (фиг. 2д) передний фронт импульса отклонения периода частоты входного сигнала от заданной с фиксацией знака рассогласования на тригсере 4 (фиг. 2ж). После прихода второго входного импульса с нулевого выхода триггера 3 триггер 5 установится в единичное состояние, а триггер 1 - в нулевое состояние, формируя не выходе элемента И-НЕ 8 задний фронт импульса отклонения периода частоты входного сигнала от перио да заданной частоты, затем цикл работы повторится. Таким образом, до тех пор, пока период частоты следования входных импульсов больше периода заданной частоты , импульс разности периодов, следующий с частотой входного сигнала, будет появляться только на выходе элемента И-НЕ 8 с фиксацией зна ка разности в виде состояния триггера 4 .. Преимуществом данного устройства по отношению к известным устройствс1М является более высокая точность рабо ты, определяемая повышенной чувствительностью к минимально различительному отклонению частрты и быстродействием. Чувствительность устройства определяется нестабильностью переклю чения используемых логических элемен тов, а быстродействие определяется периодом частоты входной импульсной последовательности.. Частотный диа пазон изменения входных сигналов огр1аничивается только частотными свойствами используемых логических элементов . Формула изобретения Устройство для определения отклонения частоты импульсной последовательности от заданной, содержащее E-S триггеры, нулевые входы первого и второго из которых подключены к нулевому выходу третьего триггера и к первым входам первого и второго элементов И-НЕ, соединенных выходами соответственно с единичным и нулевым входами четвертого триггера, а второй вход первого элемента И-НЕ подключен к единичному выходу первого триггера, соединенного нулевым выходом со вторым входом второго элемента И-НЕ, третий вход которого подключен к единичному выходу i второго триггера, соединенного нулевым выходом с третьим входом первого элемента И-НЕ, отличающееся тем, что, с целью повышения точности определения отклонения частоты, в устройство дополнительно введены пятый и шестой триггеры и элемент задержки, соединенный входом с нулевым выходом третьего триггера, единичным входом пятого триггера и первым единичным ВХОДОМ шестого триггера и подключенный выходе к единичному входу первого триггера и нулевомувходу пятого триггера, единичный выход которого соединен с.единичным входом третьего триггера, подключенного первым нулевым входом к единичному в1ыходу шестого триггера, а вторым нулевым входом - к входу устройства и второму единичному входу шестого триггера, единичный выход которого соединен с единичным входом второго триггера, а нулевой вход шестого триггера подключен к нулевому выходу пятого триггера. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 402817, кл. G 01 R 23/10, 1970. 2. Авторское свидетельство СССР . № 472447, кл. Н 03 К 5/20, 1972. 3. Авторское свидетельство СССР № 377799, кл. .G 06 G 7/14, 1971 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты на три | 1988 |

|

SU1569976A1 |

| ПРЕОБРАЗОВАТЕЛЬ ЦИФРОВОГО КОДА В ЧАСТОТУ СЛЕДОВАНИЯ ИМПУЛЬСОВ | 1992 |

|

RU2037960C1 |

| ФОРМИРОВАТЕЛЬ СУММЫ, РАЗНОСТИ И ЗНАКА РАЗНОСТИ ДВУХ ЧАСТОТ | 2002 |

|

RU2262798C2 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1992 |

|

RU2062549C1 |

| ЧАСТОТНО-ИМПУЛЬСНОЕ МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1992 |

|

RU2012040C1 |

| Умножитель частоты следования импульсов | 1980 |

|

SU923002A2 |

| Устройство задержки сигналов | 1983 |

|

SU1091306A2 |

| Устройство для дифференцирова-Ния чАСТОТы СлЕдОВАНия иМпульСОВ | 1978 |

|

SU798881A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1976 |

|

SU738158A1 |

| Устройство для интегрирования частотно-импульсных сигналов | 1974 |

|

SU615496A1 |

Авторы

Даты

1980-06-30—Публикация

1978-01-23—Подача