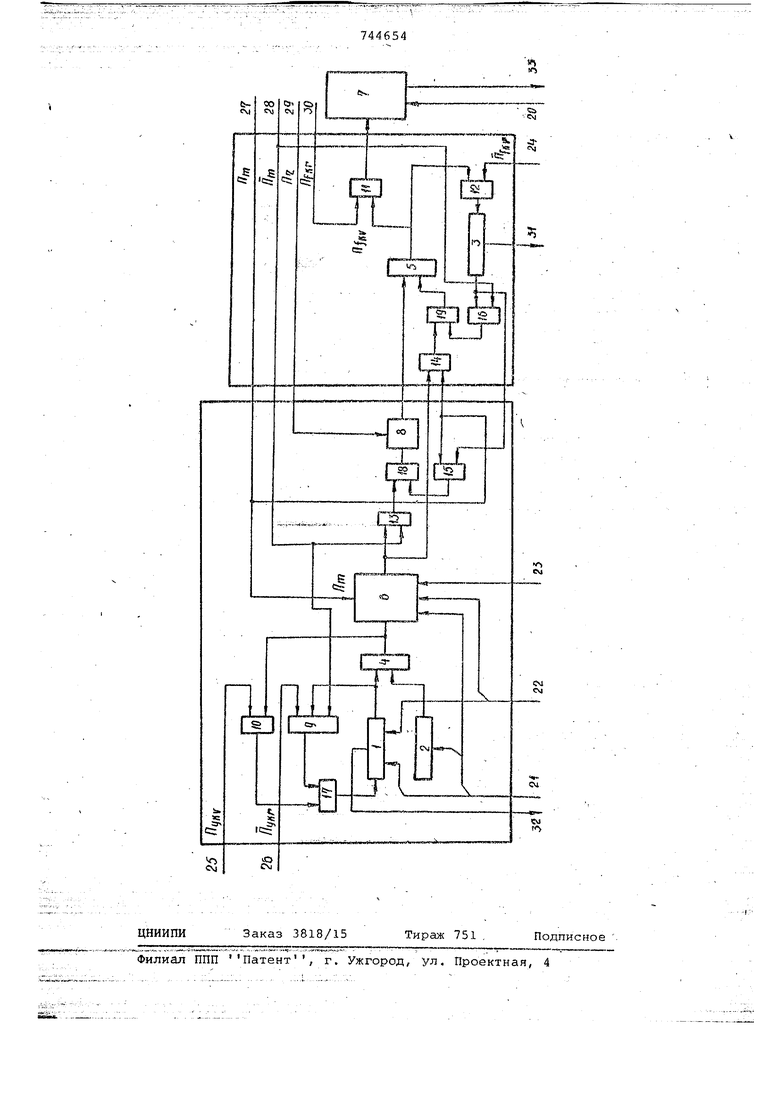

Изобретение относится к области .вычислительной техники и может быть использовано в цифровых вычислительных комплексах, работающих в системах управления, для решения в регшьном масштабе времени эпизодических точечных задач и математических зависимостей с непрерывным характером изменения переменных, а также описываемых различного вида дифференцирования уравнениями. Известны цифровыеинтеграторы, содержащие регистр, делитель, триггеры элементы И, ИЛИ 1. Быстродействие таких вычислителей оказывается недостаточным при решении дифференциальных уравнений и математических зависимостей с непрерыв ным характером изменения переменных. Наиболее близким по технической сущности к предлагаемому изобретению является интегрирующее устройство, содержащее первый, второй и третий регистры, первый и второй сумматора формирователь приращений, экстраполя тор, элементы И, ИЛИ, преобразовател кода , причем первый выход первого .регистра соединен с первым входом первого сумматора и с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, первый вход первого регистра соединен с выходом первого элемента ИЛИ, второй,вход которого соединен с выходом второго элемента И, выход второго регистра соединен со вторым входом первого сумматора, выход которого соединен с первым входом формирователя приращений и с первым входом второго элемента И, выход преобразователя кода соединен с 1первым входом второго сумматора, выход которого соединен с первыми входами третьего и четвертого элементов Ц, выход, третьего элемента И подключен к первому входу экстраполятбра, выход четвертого элемента И подключен ко входу третьего регистра, второй и третий входы первого регистра, вход второго регистра, второй, третий и четвертый входы формирователя приращений и второй вход экстраполятора является информационными входами устройства, вторые входы первого, второго третьего и четвёртого элементов И, первый вход преобразователя кода являются управляющими входами устройства, выход экстраполятора и йторой выход первого регистра являю ся информационными выходами устройства 2. „„.JHSSSSMS-li s известного, интегри Щего устройства для решения эпизод ческих эадач, вычисления Функций в точад, реализации зависимостей вида Эк у yk,x и др. мет дом интегрирования порождающих их дифференциальных уравнений снижает скорость вычисления по сравнению с прямым вычислением таких выражений с использованием арифметических операций умножения, умножения со .сложением, умножения с вычитанием. Цель изобретения- повышение быстродействия работы устройства. Поставленнаяцель достигается тем, что в устройство введены допол нительные элементы И, ИЛИ, причем в выход формирователя приращений соединен с первыми входами первого и второго дополнительных элементов И, выходы которых соединены с первыми входами соответственно первого и вто рого дополнительных элементов ИЛИ,вы ход первого дополнительного элемента ИЛИ подключен ко второму входу преобразователя кода, выход второго дополнительного элемента ИЛИ подключен ко второму входу второго сумматора, первый выход третьего регистра подключен к первым входам третьего и четвертого дополнительных элементов И, выходы которых соединены соот ветственно со вторыми входами первог и второго дополнительных элементов ИЛИ; пятый вход формирователя приращений, третий вход nepsoro, /вторые йхоДы первого, второго, третьего и четвертого дополнительных элементов И ЯВЛ5МТСЯ управляющими входами устройства, а выход третьего регистра- информационным выходом устройства . На чертеже представлена блоксхема интегро-арифметичеекого устро ства. .. Интегро-арифметическое устройств содержит регистры, 1, 2 и 3, суммато ры 4 и 5, формирователь б приращений экстраполятор 7 , преобразов ат пь 8 кода,элементы 9, ГОJ 11 и 12 И, до полнительные элементы 13, 14, 15 и 16, дополнительные элементы 17, 18 и 19 ИЛИ, информационные входы 20, 2.1. 22 и 23, управляющие входы 24, 25, 26, 27, 28, 29 и 30, информацио ные выходы 31, 32 и 33. Предлагаемое интегро-арифметическое устройство работает следующим образом. Вь41Г1Олнение.операции при работе в арифмёгическом режиме начинается после поступления из запоминающего устройства по. входу 21 множимого у в регистр 1, множителя х в формиро ватель б приращений. Операнд R является результатом предыдущей операции и к началу рассматриваемой операции хранится в регистре 3. После занесения в интегро-арифметическое устройство необходимой для выполнения операций умножение-сложение, умножение-вычитание информации код множимого из регистра 1 через сумматор 4, на второй вход которого поступает нулевая информация с выхода регистра 2, без изменения проходит на третийвход формирователя, б, осуществляющего при П 1 (Птпризнак умножение) перемножение величин ху. Произведение ху с выхода формирователя 6 через элемент 14 и и элемент 19 ИЛИ поступает на первый вход сумматора 5. На второй вход этого сумматора с выхода регистра 3 через элемент 15 и, элемент .18 ИЛИ и преобразователь 8, на второй вход которого заводится признак П (признак инверсии), поступает величина R (-1)2, При выполнении операции умножениесложение П 0 с выхода преобразователя 8 на второй вход сумматора 5 поступает величина R. При выполнении операции умножениевычитание Пг на вход сумматора 5 поступает величина R (-1)2. в сумматоре 5 формируется сумма Z xy+R(-l) поступающая на вход регистра 3 через элемент 12 И. Результат операций умножерие-сложение, умножение-вычитание остается в регистре 3 и заносится в ЗУ по выходу 31. Вычислительный процесс выполнения к-ой операции интегрирования в (i+l)ом шаге при работе в режиме интегри-. рования начинается после поступления из ЗУ по входу 21 приращения регистр 2, приращенийuypp(,.i)Ayf 0,1, ..,, m-1) в формирователь 6, подынтегральной функции ур,-; в регистр 1. Кроме того, при выполнении экстраполяции и квантования по входу 20 в экстраполятор 7 из ЗУ поступает остаток и приращенияду( (об ,12,....., т). Значение ординаты поступает на первый вход сумматора 4, на второй вход которого поступает значение приращенияvypT()/Ayс выхода регистра 2. Новое значение подынтегральной функции Ург.(.( + 1) с выхода сумматора 4 направляется в формирователь б и одновременно поступает в регистр 1 через элемент 10 И, на второй вход которого поступает признак Пурр , и через элемент 17 ИЛИ, В случае Пург,-0 неизменное значение подынтегральной функции с выхода регистра 1 через элементы 9 И и 17 ИЛИ перезаписывается в регистр 1. Полуенное на выходе формирователя б прмaщeниev5p(:(, поступающее при Пгп- О через элемент 13 И и элемент 15 ИЛИ, преобразователь 8, умножаетя в последнем на коэффициент (-1). выхода преобразователя -8 значение Л5р(р((,/ay направляется на вхо сумматора 5 и Складывается с содержимым регистра 3,поступающим на сумматор 5 через элемент 16 И и элемент 19 ИЛИ. Если отсутствует признак окончания формирования переменной tlf сумма с выхода сумматора 5 через элемент 12 и проходит в регистр 3. ЕслиП | 1, элемент 12 И закрыт и с выхода сумматора 5 через элемент 11 приращениеуудЦ л/лу поступает в экстраполятор 7. . После окончания вычислений на выход 32 поступает и заносите в ЗУ значение Урр при Пурр О (признак формирования нового значения подынте гральной функции) или . при , снимаемое с выхода регистра 1 а на выход 33 поступают и заносят ся в ЗУ эначенкяуу(;,1,/ду,Оук(1)/Ду npHil p,j и приращениеуд7(2)/ДУ Р выполнении экстраполяции приращения, После записи результатов операции выбирается информация для следующей операции, выполн ение которой аналогично. Использование предлагаемого устро ства позволяет увеличить скорость вычислений при решении эпизодичес,ких задач, требующих вычисления в отдельных точках значений прямых и. обратных тригонометрических логарифмических, экспоненциальных функций и других математических зависимостей Использование в предлагаемом устройстве операций умножения со сложением, вместо операций умножения и сложения, позволяет в 1,5 раза увеличить скорость вычисления указанных выше математических зависимостей. Формула изобретения Интегро-арифметическое устройство, содержащее первый, второй и третий регистры, первый, и второй сумма торы, формирователь приращений, экстраполятор, элементы И, ИЛИ, преобразователь кода, причем первый выход первого регистра соединен с первым входом первого сумматора и с первым входом первого элемента И, выход которого подключен к первому входу первого элемента ИЛИ, первый вход первого регистра соединен свыходом первого элемента ИЛИ, второй вход которого соединен с выходом второго элемента И, выход второго регистра соединен со вторым входом первого сумматора, выход которого соединен с первым входом формирователя приращений и с первым входом второго элемента И выход преобразователя кода соединен с первым входом второго сумматора, выход которого соединен с первыми входами третьего и четвертого элементов И, выход третьего элемента И подключен к первому ход у экстраполятора, выход четвертого элемента И подключен ко входу третьего регистра; второй и третий входы первого регистра; вход второго регистра, второй, третий и четвертый входы формирователя приращений и второй вход экстраполятора являются информационными входами устройства, вторые входы первого второго, третьего и четвертого элементов И, первый вход преобразователя кода являются управляющими входами устройства, выход экстраполятора и второй выход первого регистра: являются информационными выходами устройства, отличающеес я тем, что, с целью повышения быстродействия в него введены дополнительные элементы И, ИЛИ, причем выход формирователя приращений соединен с первыми входами первого и второго дополнительных элементов И, выхбды которых соединены с первыми входами, соответственно первого и второго дополнительных элементов ИЛИ, выход первого дополнительного элемента ИЛИ подключен ко второму входу преобразователя кода, выход второго дополнительного элоиента ИЛИ подключен ко второму входу второго сумматора, первый выход третьего регистра подключен к первым входам третьего и четвертого дополнительных, элементов И, выходы котор&гх соединены соответственно со вторыми входами первого и второго дополнительных элементов ИЛИ; пятый вход формирователя приращений, третий вход первого, вторые входы первого, второго, третьего и четвертого дополнительных элементов И являются управляющими входами устройства, а выход третьего регистра -. информационным выходом устройства. Источники информации, принятые во йнимание при экспертизе 1.Авторское свидетельство СССР №317079, кл. G Об J 1/02, 1969. 2.Авторское свидетельство СССР №335992, кл. G Об J 1/02, 1970 (прототип) ..

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегро-арифметическое устройство | 1979 |

|

SU783813A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Интегро-арифметическое устройство | 1977 |

|

SU746602A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Цифровой экстраполятор | 1984 |

|

SU1239728A1 |

| Цифровой экстраполятор | 1983 |

|

SU1126970A1 |

| ЭКСТРАПОЛЯТОР ПРИРАЩЕНИЙ ДЛЯ ЦИФРОВОЙ ИНТЕГРИРУЮЩЕЙ Л\АШИНЬГ | 1969 |

|

SU244735A1 |

| Цифровой интегратор | 1980 |

|

SU920721A1 |

| Низкоскоростной дельта-модулятор | 1984 |

|

SU1203706A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

Авторы

Даты

1980-06-30—Публикация

1977-01-04—Подача