(54) БЛОК ВЫБОРКИ ИНФОРМАЦИИ ИЗ МАТРИЧНОГО НАКОПИТЕЛЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Адресный дешифратор для полупроводникового постоянного запоминающего устройства | 1980 |

|

SU960949A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| СТАТИЧЕСКАЯ ЗАПОМИНАЮЩАЯ ЯЧЕЙКА С ДВУМЯ АДРЕСНЫМИ ВХОДАМИ | 2011 |

|

RU2470390C1 |

| Матричный накопитель | 1980 |

|

SU942151A1 |

| НАКОПИТЕЛЬ ИНФОРМАЦИИ И ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1987 |

|

SU1494785A1 |

| Буферный усилитель (его варианты) | 1983 |

|

SU1112409A1 |

| Запоминающее устройство (его варианты) | 1983 |

|

SU1098035A1 |

| Запоминающее устройство | 1980 |

|

SU903981A1 |

. I.

Изобретение относится к вычислительной технике, а именно к схемам выборки данных и микроэлектронных репрограмми- руемых постоянных запоминающих устройств с ультрафиолетовым стиранием.

Известна схема выборки данных, содержащая адресные МОП-транэисторы, . истоки которых подключены к разрядным шинам накопителя, а затворы подключены к адресным шинам 1 .

Однако известное устройство обладает недостаточным быстродействием.

Наиболее близким к предлагаемому по технической сущности и схемному решению является блок выборки информации ю матричного накопителя, содержащий МОП-транзисторы 23 .

Однако указанная схема характеризуется недостаточным быстродействием, обусловленным длительным зарядом невыбранных истоковых разрядных шин, имеющих значительную емкость, после изменения адреса столбца.

Целью изобретения 5тляется повьпиение быстродействия.

Поставленная цель достигается тем, что в блоке выборки информации кз мат ричного накопителя, содержащем МСЯ1транзисторы, затвор первого транзистора соединен с первой адресной шиной, а его сток соединен со стоком второго транзистора и первой информационной шиной, исток первого транзистора соединен с

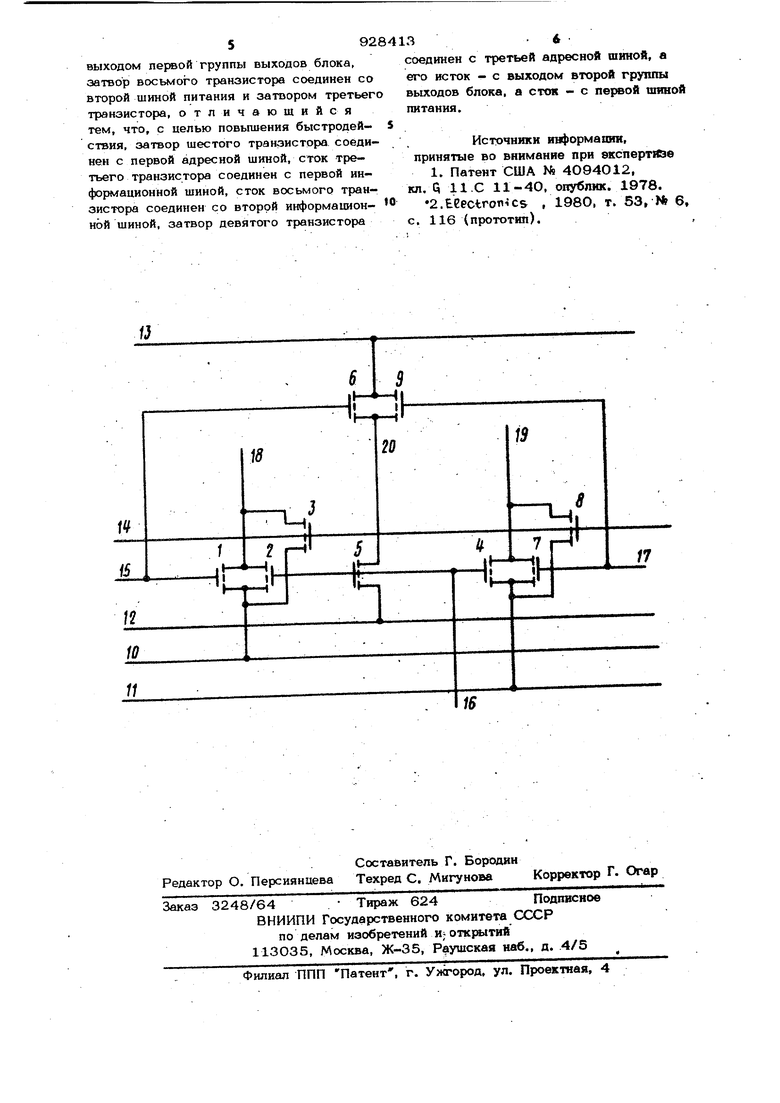

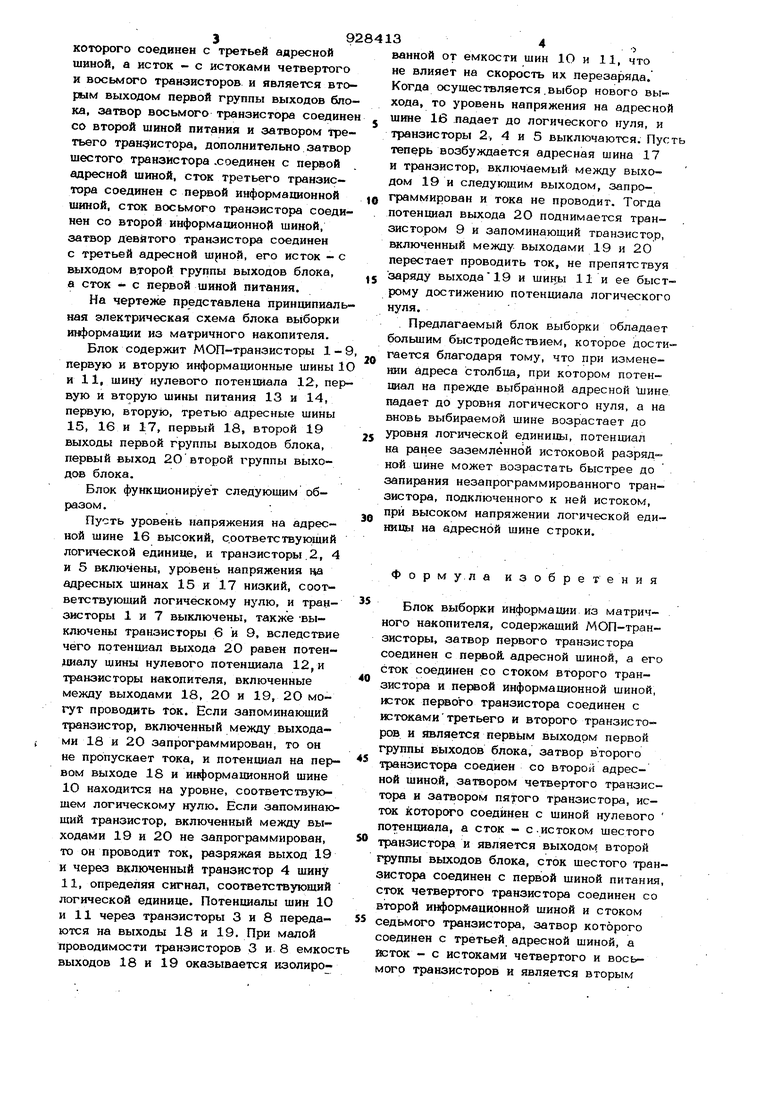

to истоками третьего и второго транзисторов и является первьсм выходом первой группы выходов блока, эатеор второго транзистора соединен со второй адресной шиной, затвором четвертогот|аанзисISтора и затвором пятого транзистора, исток которого соединен с шиной нулевого потенциала, а сток - с истоком шестого транзистора и является вторым выходом второй группы выходов блока, сток шес20того транзистора соединен с первой шиной питания, сток четвертого транзистора соединен со второй информационной шиной и стоком седьмого транзистора, затвор которого шиной, а и восьмого транзисторов и является вто рым выходом первой группы выходов бло ка, затвор восьмого транзистора соедин со второй шиной питания и затвором Тре тьего транзистора, дополнительно затвор шестого транзистора .соединен с первой адресной шиной, сток третьего транзистора соединен с первой информационной шиной, сток восьмого транзистора соеди нен со второй информационной шиной, затвор девятого транзистора соединен с третьей адресной , его исток - с выходом второй группы выходов блока, а сток - с первой шиной питания. На чертеже представлена принципиаль ная электрическая схема блока выборки информации из матричного накопителя Блок содержит МОП-транзисторы 1первую и вторую информационные шины 1 и 11, шину нулевого потенциала 12, пер вую и вторую шины питания 13 и 14, первую, вторую, третью адресные шины 15, 16 и 17, первый 18, второй 19 выходы первой группы выходов блока, первый выход 20 второй группы выходов блока. Блок функционирует следующим образом. Пусть уровень напряжения на адресной шине 16 высокий, соответствующий логической единице, и транзисторы .2, 4 и 5 включены, уровень напряжения на адресных шинах 15 и 17 низкий, соответствующий логическому нулю, и транзисторы 1 и 7 выключены, также -выключены транзисторы 6 и 9, вследствие чего потенциал выхода 20 равен потен даалу шины нулевого потенциала 12, и транзисторы накопителя, включенные между выходами 18, 20 и 19, 20 могут проводить ток. Если запоминающий транзистор, включенный между выходами 18 и 20 запрограммирован, то он не пропускает тока, и потенциал на первом выходе 18 и информационной шине 1О находится на уровне, соответствуюнщем логическому нулю. Если запоминаю щий транзистор, включенный между выходами 19 и 20 не запрограммирован, то он проводит ток, разряжая выход 19 и через включенный транзистор 4 шину 11, определяя сигнал, соответствующий логической единице. Потенциалы шин 10 и 11 через транзисторы 3 и 8 передаются на выходы 18 и 19. При малой проводимости транзисторов 3 и. 8 емкос выходов 18 и 19 оказывается изолиро39284134., соединен с третьей адреснойванной от емкости шин 10 и 11, что исток - с истоками четвертогоне влияет на скорость их перезаряда. Когда осуществляется.выбор нового выхода, то уровень напряжения на адресной шине 16 падает до логического нуля, и транзисторы 2, 4 и 5 выключаются. Пусть теперь возбуждается адресная шина 17 и транзистор, включаемый между выходом 19 и следующим выходом, запрограммирован и тока не проводит. Тогда потенциал выхода 20 поднимается транзистором 9 и запоминающий транзистор, шслюченный между выходами 19 и 20 перестает проводить ток, не препятствуя заряду выхода19 и шнцъ 11 и ее быстрому достижению потенциала логического нуля. . Предлагаемый блок выборки обладает большим быстродействием, которое достигается благодаря тому, что при изменении адреса столбца, при котором потенциал на прежде выбранной адресной шине падает до уровня логического нуля, а на вновь выбираемой шине возрастает до уровня логической единицы, потенциал на ранее заземленной истоковой разрядной шине может возрастать быстрее до запирания незапрограммированного транзистора, подключенного к ней истоком, при высоком напряжении логической едиШ1ЦЫ на адресной шине строки. Форму,ла изобретения Блок выборки информации из матричного накопителя, содержащий МОП-транзисторы, затвор первого транзистора соединен с пе{жой. адресной шиной, а его сток соединен со стоком второго транзистора и первой информационной шиной, исток первого транзистора соединен с истокамитретьего и второго транзисторов, и является первым выходом первой группы выходов блока, затвор второго транзистора соедиен со второй адресной шиной, затвором четвертого транзистора и затвором пяу-ого транзистора, исток которого соединен с шиной нулевого потенциала, а сток - с-истоком шестого транзистора и является выходом второй группы выходов блока, сток шестого фанзистора соединен с первой шиной питания, сток четвертого транзистора соединен со второй информационной шиной и стоком седьмого транзистора, затвор которого соединен с третьей адресной шиной, а ИСТОК - с истоками четвертого и восьмого транзисторов и является вторым

выходом пе|жой группы выходов блока, затвор восьмого транзистора соединен со второй шиной питания и затвором третьег транзистора, отличающийся тем, что, с целью повьпиения быстродействия, затвор шестого транзистора соединен с первой адресной шиной, сток третьего транзистора соединен с первой информационной шиной, сток восьмого транзистора соединен со второй информационной шиной, затвор девятого транзистора

соединен с третьей адресной шиной, а его исток - с выходом второй группы выходов блока, а сток - с шиной питания.

Источники информации, принятые во внимание при акспертйэе

Авторы

Даты

1982-05-15—Публикация

1980-08-13—Подача