(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1981 |

|

SU980163A1 |

| Оперативное запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1539844A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Модуль постоянной памяти | 1979 |

|

SU905858A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU627543A1 |

| УСТРОЙСТВО ДЛЯ ПАРАЛЛЕЛЬНОЙ ОБРАБОТКИ ДАННЫХ | 1991 |

|

RU2028664C1 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Устройство для вычисления квадратного корня | 1981 |

|

SU1003078A1 |

1

Изобретение относится к вычислительной технике и может быть использовано для построения устройств хранения дискретной информации.

Известны постоянные запоминающие устройства для хранения дискретной информации, содержащие дешифратор адреса, выходы которого подключены ко входу накопителя, а выходы накопителя к выходным усилителям 1J.

Такие запоминаюп1ие устройства имеют малую информационную емкость и большой объем накопителя из-за огромного числа запоминающих элементов в накопителе.

Известны также постоянные запоминающие устройства, которые кроме дешифратора адреса и накопителя имеют шифратор, входы которого подключены к накопителю, а выходы шифратора являются выходами устройства 21.

Но и эти постоянные запоминающие устройства имеют болыиое количество оборудования и малую информационную емкость, . Наиболее близким техническим ренгениемк предлагаемому является запоминающее устройство, содержащее де1нифратор адреса, выходы которого через первую группу

элемеитов ИЛИ соединены с соответствующими входами накопителя, второй группы элементов ИЛИ, входы которых подключены к выходам накопителя, а выходы через усилители считывания -- к соответствующим входам сумматора.

В сумматоре постоянного запоминающего устройства происходит формирование требуемых кодов чисел путем сложения нескольких кодов, выбранных из различных частей накопителя 3J.

10

Недостатком этого устройства является то, что оно имеет большое количество оборудования, в особенности запоминающих элемеитов в накопителе иневысокое быстродействие из-за иаличия в устройстве сум матора. Так, например, время сложения () двух чисел в наиболее быстродействующем асинхронном сумматоре зависит от разрядности сумматора (разрядность сумматора определяется разрядностью суммиjg pyeMbix чисел) и

fcK login -in.

где tj.- BpeMjf срабатывания схемы образования CVMMl r,

t,- время распространения переноса в одном разряде;

п- число разрядов сумматора.

: Время срабатывания известного (tejM4.«jBj запоминающего устройства равно

срАб.Нйв. 2tvA« ч- tyc+ Ufti

ГД W илм V вы6 и tcft соотЪетственно время сраоатывания дешифратора адреса, элемента ИЛИ, усилителя считывания,время выборки кода числа из накопителя и время суюжения двух чисел на сумматоре.

Цель изобретения. повышение надежности и быстродействия устройства.

Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее дешифратор, выходы которого соел.йнёны со входами накопителя и. элементов ИЛИ первой группы, вторую группу эле- ментов ИЛИ, введены элементы И и регистр числа, входы которого через элементы ИЛИ второй соединены с выходами соответствующих элементов И, первые входы соответствующих элементов И подключены К выходам накопителя, а вторые - к выходам элементов ИЛИ первой группы.

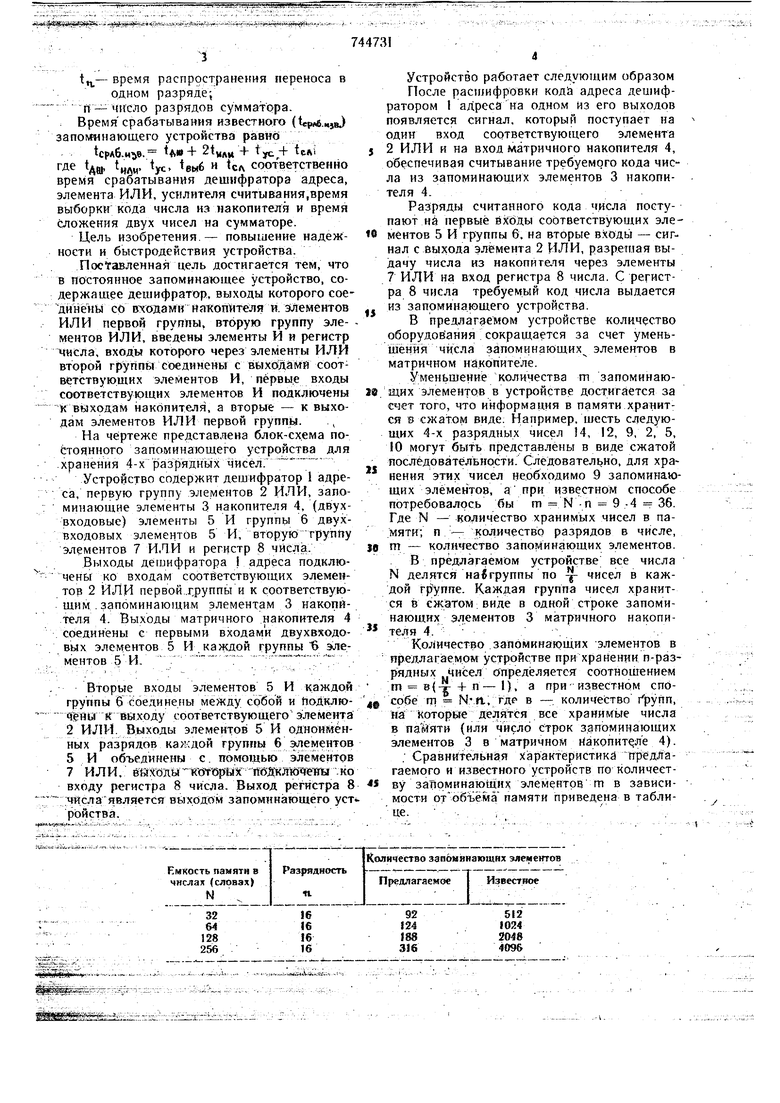

На че:ртеже представлена блок-схема постоянного запоминающего устройства для .хранения 4-х разрядных чисел.

Устройство содержит дешифратор I адреса, первую группу элементов 2 ИЛИ, запоминающие элементы 3 накопителя 4, (дВухвходовые) элементы 5 И группы 6 двухвходовых элементов 5 И, вторуюгруппу элементов 7 ИЛИ и регистр 8 чИела.

Выходы дешифратора I адреса подключены ко входам соответствующих элементов 2 ИЛИ первой .группы и к соответствующим . запоминающим элементам 3 накопителя 4. Выходы матричного накопителя 4 соединены с первыми входами двухвходовых элементов 5 И каждой группы Б элементов 5 И. -- .--::..-.-.- .-

Вторые входы элементов 5 И каждой группы 6 соединены между с()бой и йоДключейы К: выходу соответствующего э лемента 2 ИЛИ. Выходы элементов 5 И одноимённых разрядов каждой группы 6 элементов 5 И объединены с. полтощью элементов 7 ИЛИ, gSWKy lKW6pHr SKff 04i&mi ко входу регистра 8 числа. Выход регистра 8 является выходом запоминающего уст ройства.

..S

Устройство работает следующим образом После расшифровки кода адреса дешифратором 1 адреса на одном из его выходов появляется сигнал, который поступает на один вход соответствующего элемента 5 2 ИЛИ и на вход матричного накопителя 4, обеспечивая считывание требуемого кода числа из запоминающих элементов 3 накопителя 4.

Разряды считанного кода числа поступают на первые вХоДы соответствующих элеe ментов 5 И группы 6, на вторые входы - сиг., нал с выхода элемента 2 ИЛИ, разретпая выдачу числа из накопитетя через элементы 7 ИЛИ на вход регистра 8 числа. С регистра 8 числа требуемый код числа выдается из запомина.ющего устройства.

В предлагаемом устройстве количество оборудования сокращается за счет уменьшения числа запоминающих элементов в матричном накопителе.

Уменьшение количества m запоминаюв.щих элементов в устройстве достигается за счет того, что информация в памяти хранится в сжатом виде: Например, шесть следующих 4-х разрядных чисел 14, 12, 9, 2, 5, 10 могут быть представлены в виде сжатой последовательности. Следовательно, для хранения этих чисел не.обходимо 9 запоминающих элементов, а при известном способе потребовалось бы m N -п 9 -4 36. Где N - количество хранимых чисел в памяти; п - количество разрядов в числе, 0 m - колич ество запоминающих элементов. В предлагаемом устройстве все числа N делятся Hai группы по Ц- чисел в каждой г)уппе. Каждая группа чисел хранится в сжатом. виде в одной строке запоминающих элементов 3 матричного накопи теля 4.

Количество запоминающих элементов в предлагаемом устройстве при хранении п-разрядных чисел определяется соотношением т в{-т + п- П, а при известном споg собе т Nft, ГДР в -. количество фупп, на Которые делятся все хранимь1е числа в паМяти (или число строк запоминающих элементов 3 в матричном Накопителе 4). ; Сравнительн;зя х;арактеристика предлагаемого и известного устройств по количест ву заТ оминающих элементов m в зависимости от объёма памяти приведена в таблиу . це. . , ,. Количество элементов 2 ИЛИ и число групп б элементов 5 определяется количеством групп в, на которые делятся все хранимые числа N (или то же самое количеством строк в матричном накопителе), а количество элементов И 5 в каждой группе 6 и число элементов 7 ИЛИ равно п. Время срабатывания предлагаемого (срлб.пр.) устройства определяется соотношением.np Цш + вмб Ч- 1„ +1„дц+ ftf. Если предположить, что любое, запрмкйаюшее устройство имеет регистр числа и что . то предлагаемое устройство по сравнению с известным позволяет повысить быстродействие на величину tc.-f tyc. Применение групп двухвходовых элементов И выгодно отличает предлагаемое запоминающее устройство от известного, так как позволяет уменьшить количество оборудования, в особенности запоминающих элементЬв в накопителе, а также увеличить быстродействие за счет того, что формирование кодов чисел, в отличие от известного,осуществляется без применения сумматора. . Формула изобретения Постоянное запоминающее устройство, содержащее дешифратор, выходы которого соединены со входами накопителя и элементов ИЛИ первой группы, вторую группу элементов ИЛИ, отличающееся тем, что, с целью повы.шения надежности и быстродействия устройства, оно содержит элементы И и регистр числа, входы которого через элементы ИЛИ второй группы соединены с выходами соответствующих элементов И, nepBbie входы соответствующих элементов И подключены к выходам накопителя, а вторые - к выходам элементов ИЛИ первой группы. Источники информации, . принятые во внимание при экспертизе 1.Брик Е. А. Постоянные запоминающие устройства. «Энергия, 1969, с. 25. 2.Авторское свидетельство СССР 312310, кл. G II С 17/00, 1971. 3; Авторское свидетельство СССР 490184, кл. G 11 С 17/00, 1-975 (прототип).

Авторы

Даты

1980-06-30—Публикация

1978-03-28—Подача