Изобретение относится к вычисли,тельной технике и может быть исполь .зовано для построения устройств хранения дискретной информации. Известны запомингиоище устройства состоящие из дешифратора адреса, выходы которого через первую группу элементов ИЛИ подключены к входам i накопителя, второй группы ИЛИ, вход которых соединены с выходами накопи теля, а выходы через усилители считывания - к сумматору ij . Но все зти постоянные запсичинающ устройства имеют большое количество оборудования и малую информационную емкость. Наиболее близким по .технической сущности к предлагаемому является запоминающее устройство, состоящее из дешифратора, выходы которого соединены с входами накопителя и элементов ИЛИ первой группы, регистра числа, входы которого через злементы ИЛИ второй группы подключены к выходам группы соответствующих элементов И, первые входы элементов И соединены с выходами накопителя, а вторые - с выходами ИЛИ первой группы 2 . Устройство имеет большое количество оборудования и вследствие этого невысокую надежность. Так, например, количество элементов И в группе равно , где N - количество хранимых чисел в пги 1яти; Ь число групп, на которое делятся.чсе числа; п - разрядность исходных чисел. А число элементов ИЛИ второй группы равно п, причем все элементы на п входов. Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что постоянное запоминающее устройство, содержащее дешифратор, выход которого соединен с входом накопителя и входом первого блока элементов ИЛИ, второй блок элементов ИЛИ, выход которого подключен к первому входу сдвигового регистра числа и элемент И, дополнительно содержит генератор импульсов, выход которого подключен к первому входу элемента И, второй вход элемента И подключен к выходу сдвигового регистра числа, выход элемента И соединен с третьим входом сдвигового регистра числа, четвертый вход которого подключен к выходу накопителя.

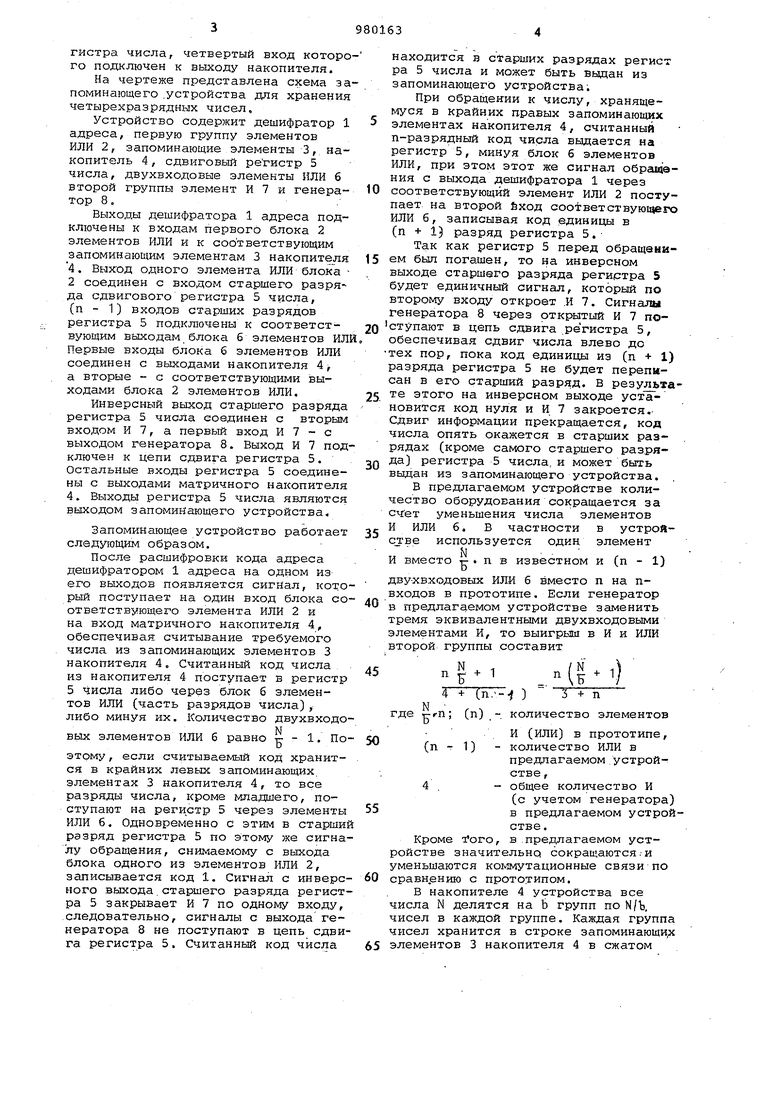

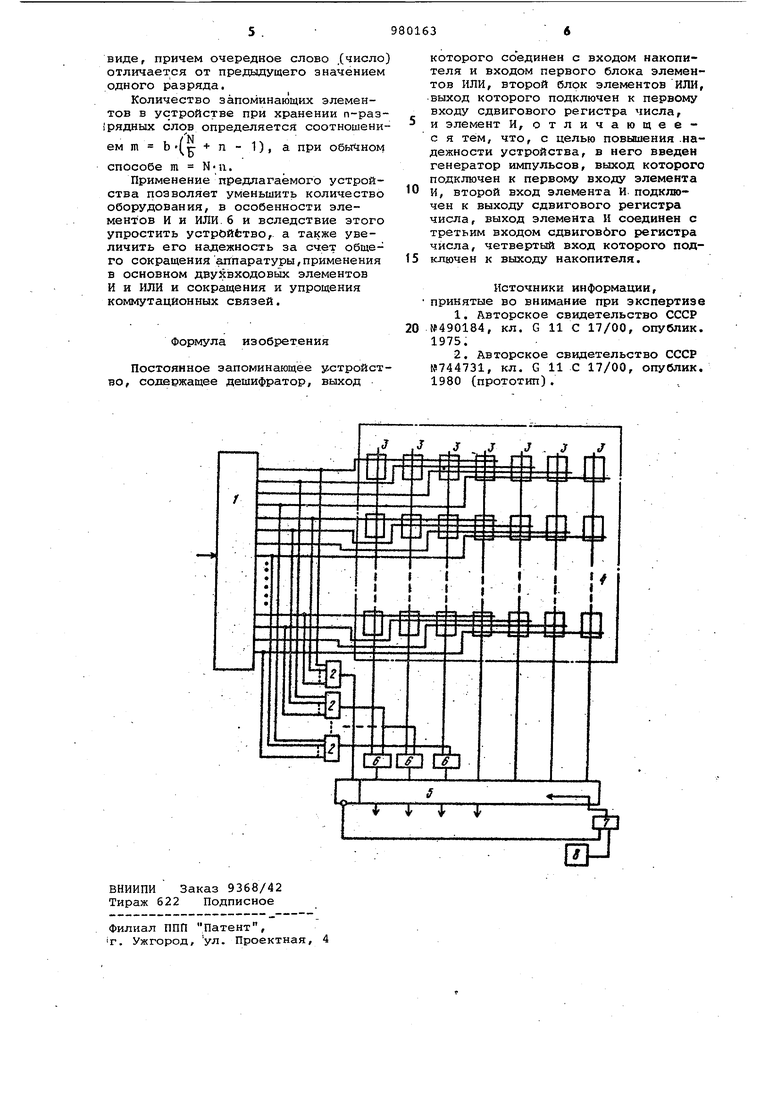

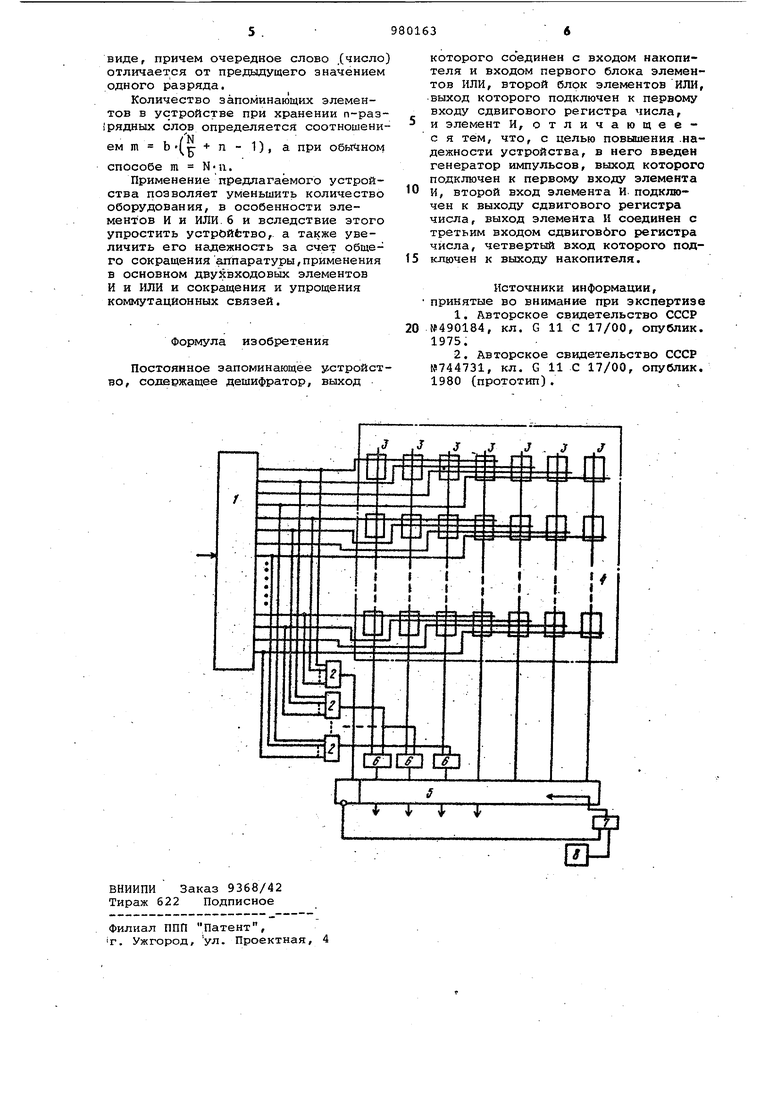

На чертеже представлена схема запоминающего .устройства для хранения четырехразрядных чисел.

Устройство содержит дешифратор 1 адреса, первую группу элементов ИЛИ 2, запоминающие элементы 3,, накопитель 4, сдвиговый регистр 5 числа, двухвходовые элементы ИЛИ б второй группы элемент И 7 и генератор 8.

Выходдл дешифратора 1 адреса подключены к входам первого блока 2 элементов ИЛИ и к соответствующим запоминающим элементам 3 накопителя 4. Выход одного элемента ИЛИ блока 2 соединен с входом старшего разряда сдвигового регистра 5 числа, (п - 1) входов старших разрядов регистра 5 подключены к соответствующим выходам блока 6 элементов ИЛИ Первые входы блока 6 элементов ИЛИ соединен с выходами накопителя 4 а вторые - с соответствующими выходами блока 2 элементов ИЛИ.

Инверсный выход старшего разряда регистра 5 числа соединен с вторым входом И 7, а первый вход И 7 - с выходом генератора 8. Выход И 7 подключен к цепи сдвига регистра 5. Остальные входы регистра 5 соединены с выходами матричного накопителя 4. Выходы регистра 5 числа являются выходом запоминающего устройства.

Запоминающее устройство работает следующим образом.

После расшифровки кода адреса дешифратором 1 адреса на одном из его выходов появляется сигнал, который поступает на один вход блока соответствующего элемента ИЛИ 2 и на вход матричного накопителя 4, обеспечивая считывание требуемого числа из запоминающих элементов 3 накопителя 4. Считанный код числа из накопителя 4 поступает в регистр 5 числа либо через блок 6 элементов ИЛИ (часть разрядов числа), либо минуя их. Количество двухвходоN

вьзх элементов ИЛИ 6 равно -р - 1. Поэтому , если считываемый код хранится в крайних левых запоминающих, элементах 3 накопителя 4, то все разряды числа, кроме младшего, поступают на регистр 5 через элементы ИЛИ б. Одновременно с этим в старши разряд регистра 5 по этому же сигналу обращения, снимаемому с выхода блока одного из элементов ИЛИ 2, записывается код 1. Сигнал с инверсного выхода старшего разряда регистра 5 закрывает И 7 по одному входу, следовательно, сигналы с выхода генератора 8 не поступают в цепь сдвига регистра 5. Считанный код числа

находится в старших разрядах регист ра 5 числа и может быть выдан из запоминающего устройства;

При обращении к числу, хранящемуся в крайних правых запоминающих

элементах накопителя 4, считанный п-разрядный код числа выдается на регистр 5, минуя блок 6 элементов ИЛИ, при этом этот же сигнал обрадэния с выхода дешифратора 1 через

соответствующий элемент ИЛИ 2 поступает на второй бход соответствую1чего ИЛИ 6, записывая код единицы в (п + 1) разряд регистра 5,Так как регистр 5 перед обращанием бьш погашен, то на инверсном выходе старшего разряда регистра 5 будет единичный сигнал, который по второму входу откроет .И 7. Сигналы генератора 8 через открытый И 7 поступают в цепь сдвига регистра 5, обеспечивая сдвиг числа влево до тех пор, пока код единицы из (и + 1) разряда регистра 5 не будет переписан в его старший разряд. В результате этого на инверсном выходе установится код нуля и И 7 закроется.Сдвиг информации прекращается, код числа опять окажется в старших раз рядах (кроме самого старшего разряда) регистра 5 числа, и может быть выдан из запоминающего устройства. В предлагаемом устройстве количество оборудования сокращается за счет уменьшения числа элементов

И ИЛИ 6. В частности в устроЯqjBe используется один элемент

И вместо т- . п в известном и (п - 1)

дву-хвходовых ИЛИ б вместо п на пвходов в прототипе. Если генератор в предлагаемом устройстве заменить тремя эквивалентными двухвходовыми элементами И, то выигрыш в И и ИЛИ второй группы составит

.()

N

+ 1

п

4 (п/- )

3 + п

N

где (п) .- количество элементов

И (ИЛИ) в прототипе, (п - 1) - количество ИЛИ в

предлагаемом устройстве , 4 . - общее количество И

(с учетом генератора)

5в предлагаемом устройстве.

Кроме Ioro, в предлагаемом устройстве значительно сокращаются;и уменьшаются коммутационные связи по 0 сравн.ению с прототипом.

В накопителе 4 устройства все числа N делятся на b групп по N/Ъ, чисел в калщой группе. Каждая группа чисел хранится в строке запоминающи,х 5 элементов 3 накопителя 4 в сжатом

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Оперативное запоминающее устройство | 1975 |

|

SU653624A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU834768A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Запоминающее устройство на сдвиговых регистрах | 1979 |

|

SU860139A1 |

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| ПРОЦЕССОР ДЛЯ ЦИФРОВОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ | 1971 |

|

SU305477A1 |

| Генератор псевдослучайных испытательных последовательностей | 1986 |

|

SU1354401A2 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

Авторы

Даты

1982-12-07—Публикация

1981-06-15—Подача