I

Изофетение огносигся к запоминающим устройствам.

Известно устройство, содержащее блоки памяти, адресные входы которых подключены к блоку формирования адресов, первые управляющие входы - к выходу блока регистрации, втфой управляющий вход первого блока памяти - к выходу второго блока памяти, второй управляющий вход Korqporo соединен с выходом первого блока памяти и со входом блока регистрации, а третий управляющий вход первого блока памяти подключен к выходу блока сравнения l.

Недостатком этого устройства является недостаточно высокое быстродействие.

Наиболее близким по техннческсй сущности к предлагаемому является устройство, которое содержит постоянный накопитель, регистр числа, дешифратор адреса, первый к второй дополнительные накопители, блсж обнаружения ошибки, внешний (эталонный накопитель), блек преобразования адреса, блок управления. ВыХОД постоянного накопителя подключи к первому входу регистра числа, второй вход которого соединен с выходом первого дополнительного накопителя, третий вход - с выходом блока управления, выходы второго дополнительного накопителя подключены ко второму входу блока сравнения, первый вход соединен с выходом младших разрядов регистра адреса, а выход - со входом блока управле0ния, адресные входы первого и arqioro дополнительных накопителей подкпюче ны к выходу старших разрядов регистра адреса.

5

Устройство позволяет ароизводнть контроль постоянного накопителя в автоматическое занесение информацив неисправных ячеек памяти в резервные, подменяющие отказавшие

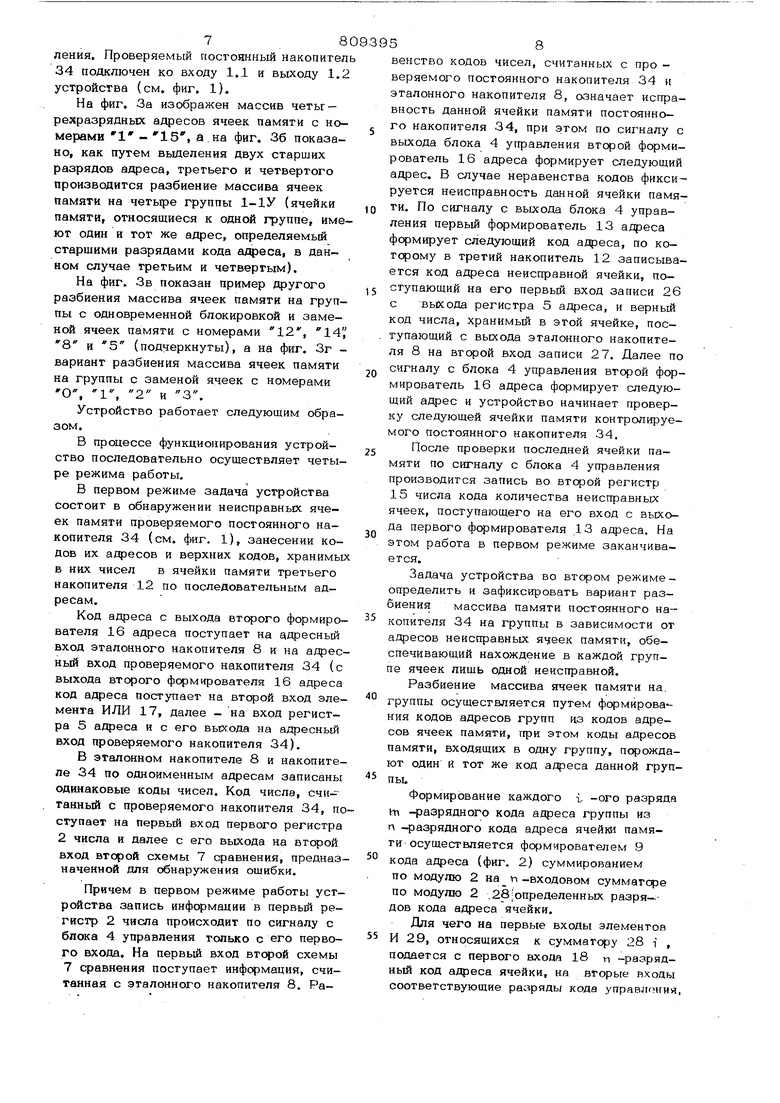

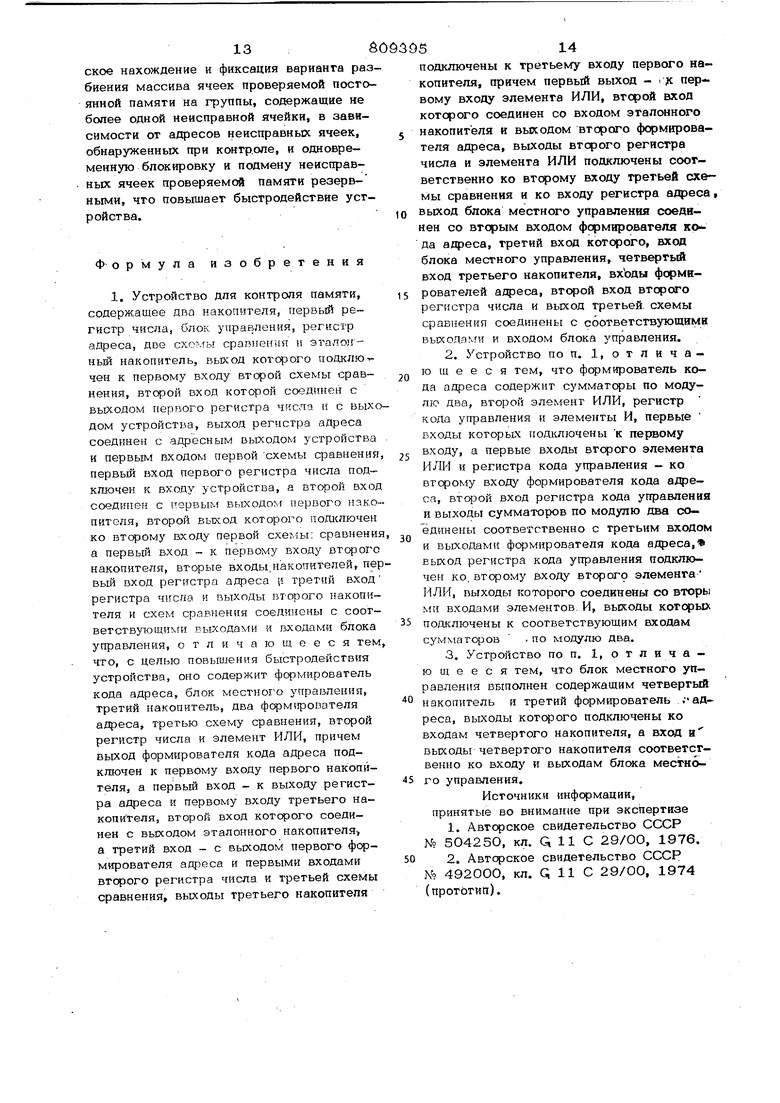

В устройстве массив ячеек памяти постоянного накопителя разбивается на группы путем выделения в коде адреса части стаоших разрядов, определяющих группу 380 ячеек памяти и части младших разрядов, определйющих ячейку памяти в группе. Каждой группе соответствует одна ячейка памяти в первом дополнительном накопителе, куда гфи обнаружении отказа одной ячейки памяти в группе автоматически заносится информация отказавшей ячей ки памяти, считанная с соответствующей ячейки внешнего накопителя, и одна ячейка памяти во втором дополнительном накопителе, куда заносится код младших разрядов адреса отказавшей ячейки, опре;Деляющий отказавшую ячейку памяти в группе. В дальнейидем, при контроле устройства в процессе работы, по текущему адресу производится считывание информации с постоянного накопителя, а также по адресу, определяемому старшими разрядами регистра адреса, производится считывание информации с первого и второго дополнительных накопителей, Блок сравнения производиг сравнение кода адреса, считанного со второго Дополнительного накопителя, и адреса, определяемого младшими разрядами регистра адреса, В случае их равенства фиксируется факт обращения к неисправной ячейке памяти и нужная информация запи сывается в регистр числа с выхода первого дополнительного накопителя 2. Недостатком этого устройства является невозможность автоматически находит и фиксировать нужный-вариант разбиения массива ячеек памяти на группы в зависимости от ащэесов неисправных ячеек, обнаруженных при контроле, и согласно этому варианту заносить информацию отказавших ячеек памяти в резервные ячей ки первого дополнительного накопителя п соответствующим адресам, что снижает быстродействие устройства. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство для ко 1троля памяти, содержащее два накопителя, первый регистр числа, блок управления, регистр адреса, две схемы сравнения и эталонный накопитель, выход которого подключен к первому входу второй схемы срав нения, второй: вход которой соединен с выходом первого регистра числа и с вы ходом устройства, выход регистра адре са соединен с адресным выходом устрой сг 1за и nepBbnvi входом первой схемы ер внения, первый вход первого регистра ч сла подключен к входу устройства, а второй вход соединен с первым выходом ервого накопителя, второй выход котороо подключен ко второму входу первой хемы сравнения, а первьй вход - к пер-т ому входу втфого накопителя, вторые входы накопителей, первый вход регистра а/чэеса и третий вход регистра числа и выходы второго накопителя и схем сравн.ения соединены с соответствующими выходами и входами блока управления, введены формирователь кода адреса, блок местного управления, третий накопитель, два фс мирователя адреса, третья схема сравнения, второй регистр числа и элемент ИЛИ, .причем выход формирователя кода адреса подключен к первому входу первого накопителя, а первый. вход - к выходу регистра адреса и первому входу третьего накопителя, второй вход которого соединен с выходом эталонного накопителя, а третий вход - с выходом первого формирователя адреса и первыми входами BTOfJoro регистра числа и третьей схемы сравнения, выходы третьего накопителя подключены к третьему входу первого накопителя, причем первый выход к первому входу элемента ИЛИ, втсрой вход которого соединен со входом эталонного накопителя и выходом второго формирователя адреса, выходы BTqaoro регисгра числа и элемента ИЛИ подключены соответственно - ко второму входу третьей схемы сравнения и ковходу регистра адреса, выход блока местного управления соединен со вторым входом формирователя кода сдреса, третий вход которого, вход блока местного управления, четвертый вход третьего накопителя, входы формирователей адреса, второй вход второго регистра числа и выход третьей схемы сравнения соединены с соответствующими выходами и входом блока управления. При этом формирователь кода адреса целесообразно выполнить содержащим сумматоры по модулюдва, второй элемент ИЛИ, регистр кода управления и элементы И, первые входы которых подключены к первому входу, а первые входы элемента ИЛИ и регистра кода управления - ко второму входу формирователя кода адреса, второй вход регистра кода управления и выходы сумматоров по модулю два соединены соответственно с третьим входом и выходами формироватедя кода аареса, выход регистра кода управлення подключен ко второму входу элемента ИЛИ, выходы которого соединены со вторыми входами элементов И, вьссоДы которых подключены к соотвегствующим входам сумматоров по модулю два. Блок местного управления целесообразно выполнить содержащим четвертый накопитель и третий формирователь адреса, выходы которого подключены ко входам четвертого накопителя, а вход и выходы четвертого накопителя соответственно ко входу и выходам блока местного управления. На фиг. 1 изображена принципиальная схема устройства; на фиг, 2 - схемы фор мирователя кода адреса и блока местного управления; на фиг. За,б,в и г -примеры разбиения массива ячеек памяти на группы. Устройство для контроля памяти содержит (фиг. 1) вход 1.1 и адресньш выход 1.2 устройства, первый регистр 2 числа, накопитель 3, блок 4 управления, регистр 5 адреса, первую б и вторую 7 схемы сравнения, эталонньй накопитель 8, формирователь 9 кода адреса, блок 10 местного управления, второй 11 и третий 12 накопители, первый формирователь 13 адреса, третью схему 14 сравнения, регистр 15 числа, втсрой формирователь 16 адреса, первый элемент ИЛИ 17, входы 18-2О и выходы 21 формирователя кода адреса, вькод 22 и вход 23 блока 1О местного управления, выходы 24 и 25 и первый 26 и второй 27 входы третьего накопителя 12. ВьосоД эталонного накопителя 8 подключен к первому входу втqDoй схемы 7 сравнения, второй вход кorqэoй соединен с выходом первого регистра 2 числа и с выходом устройства. Выход регистра 5 адреса соединен с адресным выходом 1.2 устройства и первым входом первой схем 6 сравнения. Первый вход первого регист ра 2 числа подключен ко входу 1.1 устройства, а второй вход соединен с первы выходом первого накопителя 3, второй вы ход которого подключен ко второму входу первой схемы 6 сравнения. Первый вход первого накопителя 3 подключен к первому входу второго накопителя 11. Вторые входы первого 3 к второго 11 накопителей, первьш вход регистра адреса 5 и третий вход первого регистра числа 2 и выходы накопителя 11, первой 6 и второй 7 схем сравнения соединены с соответствующими выходами и входами блока 4 управления. Выходы21 формирователя 9.кода адреса подключень( к первому входу первого накопителя 3, а первый вход 18 к вы856 ходу регистра 5-адреса и первому входу 26третьего накопителя 12, второй вход 27которого соединен с выходом эталонного накопителя 8, а третий вход - с выходом первого формирователя 13 адреса и; первыми входами второго регистра числ 15 и третьей схемы 14 сравнения. Выходы 24 и 25 третьего накопителя 12 подключены к третьему входу первого накопителя 3, причем первый выход 24 - к первому входу элемента ИЛИ 17, второй вход которого соединен со входом-эталонного накопителя 8 и выходом второго формирователя 16 адреса.Выходнвторотч) регистра 15 числа и элемента ИЛИ 17 подключены соответственно ко второму входу третьей схемы 14 сравнения и ко входу регистра 5 адреса. Выход 22 блока 10 местного управления соединен со вто- рым входом 19 формирователя 9 кода адреса, третий вход 2О которого, вход 23 блока 1О местного управления и четвертый вход третьего накопителя 12 входы, первого 13 и второго 16 формирователей адреса, второй вход бторого регистра 15 числа и выход третьей схемы 14 сравнения соединены с соответствующими выходами и входами блока 4 управления. При этом ффмирователь 9 кода адреса (см, фиг. 2) содержит сумматоры по модулю два , элементы И 29, второй элемент ИЛИ ЗО и регистр 31 кода управления. Первые входы элементов И 29 подключены к первому входу 18, а первые входы второго элемента ИЛИ 30 и регистра 31 кода управления - ко второму 19 входам формирователя 9 кода адреса. Второй вход регистра 31 кода управления и выходы сумматоров по модулю два 28 - 28 соединены соответственно с третьим входом 2О и выходами формирователя 9 кода адреса. .Выход регистра 31 кода управления подключен ко второму входу второго элемента ИЛИ ЗО, выходы которого соединены со вторыми входами элементов И 29, выходыкотсрых подключены к соответствующим входам сумматоров по модулю два 28 28„,. При этом блок 10 местного управления ыполнен содержащим (см. фиг. 2) четертый накопитель 32 и третий формироатель 33 адреса, выходы которого подлючены ко входам четвертого накопитея 32, Вход третьего формирователя 33 адреа и выходы четвертого накопителя 32 оединены соответстветю со входом 23 вькодом 22 блока 10 местного управления. Проверяемый посгоянный накопитель 34 подключен ко входу 1.1 н выходу 1.2 устройства (см, фиг. 1).

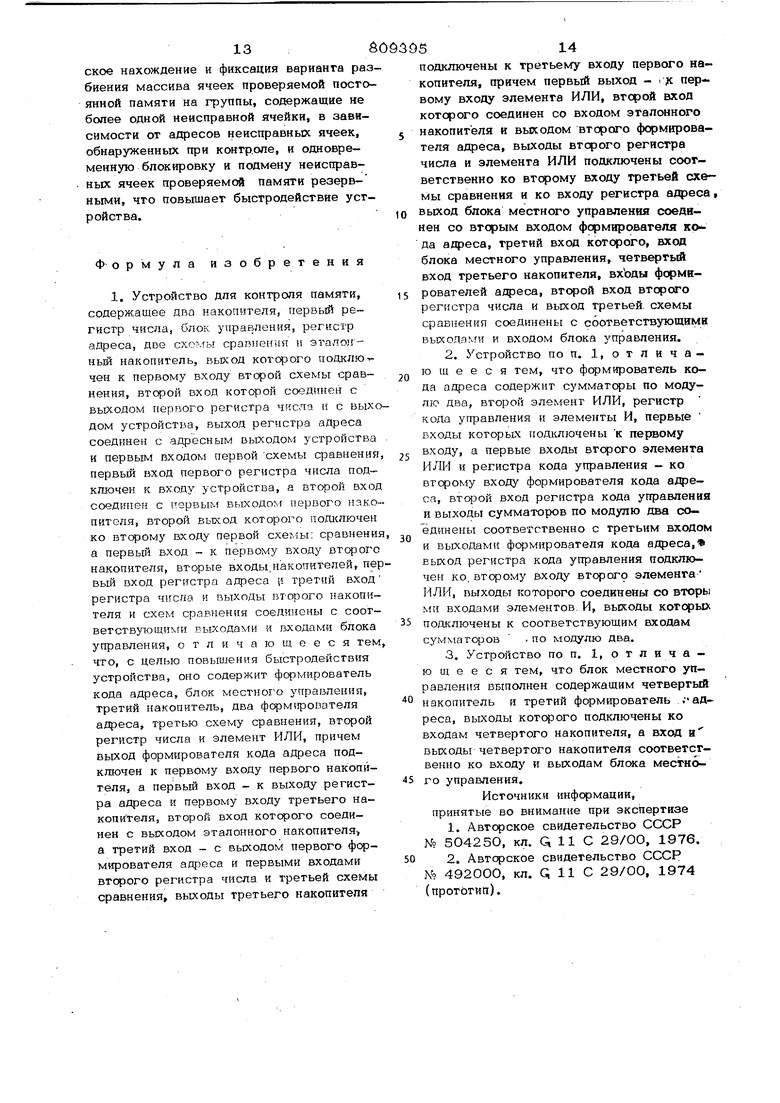

На фиг. За изображен массив четырехразрядных адресов ячеек памяти с номерами - 15, а. на фиг. 36 показано, как путем выделения двух старших разрядов адреса, третьего и четвертого производится разбиение массива ячеек памяти на четьфе группы 1-1У (ячейки памяти, относящиеся к одной группе, имеют один и тот же адрес, определяемый старшими разрядами кода адреса, в данном случае третьим и четвертым).

На фиг. Зв показан пример рругого разбиения массива ячеек памяти на группы с одновременной блокировкой и заменой ячеек памяти с номерами 12, 14 8 и 5 (подчеркнуты), а на фиг. Зг вариант разбиения массива ячеек памяти на группы с заменой ячеек с номерами О, 1, 2 и 3.

Устройство работает следующим образом.

В процессе функционирования устройство последовательно осуществляет четыре режима работы.

В первом режиме задача устройства состоит в обнаружении неисправньсх ячеек памяти проверяемого постоянного накопителя 34 (см. фиг. 1), занесении кодов их адресов и верхних кодов, хранимых в них чисел в ячейки памяти третьего накопителя 12 по последовательным адресам.

Код адреса с выхода второго формирователя 16 адреса поступает на адресный вход эталонного накопителя 8 и на адресный вход проверяемого накопителя 34 (с выхода второго формирователя 16 адреса код адреса поступает на вход элемента ИЛИ 17, далее - на вход регистра 5 адреса и с его выхода на адресньй вход проверяемого накопителя 34).

В эталонном накопителе 8 и накопителе 34 по одноименным адресам записаны одинаковые коды чисел. Код числа, счи. танный с проверяемого накопителя 34, поступает на первый вход первого регистра 2 числа и далее с его выхода на второй вход второй схемы 7 сравнения, предназначенной для обнаружения ошибки.

Причем в первом режиме работы устройства запись информации в первый регистр 2 числа происходит по сигналу с блока 4 управления только с его первого входа. На первый вход второй схемы 7 сравнения поступает информация, считанная с эталонного накопителя 8. Равенство кодов чисел, считанных с про веряемого постоянного накопителя 34 н эталонного накопителя 8, означает исправность данной ячейки памяти постоянно- го накопителя 34, при этом по сигналу с выхода блока 4 управления второй формирователь 16 адреса формирует следующий адрес. В случае неравенства кодов фиксируется неисправность данной ячейки памяти. По сигналу с выхода блока 4 управления первый формирователь 13 адреса фсрмирует следующий код адреса, по которому в третий накопитель 12 записывается код адреса неисправной ячейки, по5 ступающий на его первый вход записи 26 с выхода регистра 5 адреса, и верный код числа, хранимый в этой ячейке, пос- . тупающий с выхода эталонного накопителя 8 на второй вход записи 27. Далее по сигналу с блока 4 управления второй формирователь 16 адреса формирует следующий адрес и устройство начинает проверку следующей ячейки памяти контролируемого постоянного накопителя 34.

После проверки последней ячейки памяти по сигналу с блока 4 управления производится запись во второй регистр 15 числа кода количества неисправньк ячеек, поступающего на его вход с выхода первого фqэмиpoвaтeля 13 адреса. На этом работа в первом режиме заканчивается.

Задача устройства во втором режимеопределить и зафиксировать вариант разбиения массива памяти постоянного на- копителя 34 на группы в зависимости от адресов неисправных ячеек памяти, обеспечивающий нахождение в каждой группе ячеек лишь одной неисправной.

Разбиение массива ячеек памяти на. группы осуществляется путем формирова ния кодов адресов групп из кодов адресов ячеек памяти, при этом коды адресов памяти, входящих в одну группу, порождают один и тот же код адреса данной группы.

Формирование каждого i -ого разряда Ж -разрядного кода адреса группы из п -разрядного кода адреса ячейк памяти осуществляется формирователем 9 кода адреса (фиг. 2) суммированием по модулю 2 на п -входовом сумматоре по модулю 2 .28;определенных разря-.дов кода адреса ячейки.

Для чего на первые входы элементов 55 И 29, относящихся к сумматору 28 i , подается с первого входа 18 п -разрядньй код адреса ячейки, на вторые входы соответствующие разряды кода управл(,

Поступающего со второго входа 19 через первый вход второго элемента ИЛИ 30.

В зависимости от кода управления с выходов И 29 на входы сумматора 28i поступают те или иные разряды кода адреса ячейки памяти, чем достигается выбор нужного алгоритма формирования каждого 1 -ого разряда кода адреса группы.

Различные коды управления записаны в четвертом накопителе 32 (фиг. 2) блока Ю местного управления. При этом формирование текущего значения кода управления осуществляется считыванием его из четвертого накопителя 32 по адреру, поступающему с выхода третьего формирователя 33 адреса.

Найденный в процессе работы устройства код управления, а следовательно и вариант разбиения массива ячеек памяти на группы, фиксируется в регистре 31 кода управления (фиг. 2). В данном режиме работы устройство осуществляет проверку каждот-о варианта разбиения массива ячеек памяти на группы, определяемого соответствующим текущим значением кода управлени$ т.е. определяет не содержится ли в каждой группе более одной неисправной ячейки памяти.

Для этого , начиная с первого адреса, производится последовательное считывание с третьего накопителя 12 кодов адресов неисправных ячеек памяти. Код адреса неисправной ячейки памяти с первсмго выхода 24 третьего накопителя 12 через первый ВХОД первого элемента ИЛИ 17 поступает на вход регистра 5 адреса и с его выхода на первьй вход 18 формирователя 9 кода адреса, служащего для фсрмирования кода адреса группы ячеек памяти.

С вьссода 2О формирователя 9 кода адреса m -разрядный код адреса группы поступает на azjpecHbui вход второго накопителя 11. По сигналу блока 4 угфавления производится считывание инфс мации из

одноразрядной ячейки памяти второго накопителя 11, расположенной по данному адресу, а затем запись в нее единичной информации. Предварительно все ячейки .памяти второго накопителя 11 обнуляются, поэтому считанная из его ячейки единичная информация свидетельствует о том, что обращение к ней уже было ранее Это означает, что в группу ячеек памяти, имеющих данный разрядный код адреса группы, входит более одной неисправной ячейки постоянного,накопителя 34, и

следовательно, проверяемый вариант разбиения массива ячеек памяти на группы, определяемый текущим значением кода управления, неприемлем. По единичнс у сигналу с выхода второго накопителя И блок 4 управления переводит устройство в режим проверки следующего варианта разбиения массива ячеек памяти на группы. Цпя этого по сигналу с блока 4 управления блок 10 местного управления формирует следующий проверяемый код управления, ячейки памяти второго накопителя 11 обнуляются, из третьего накопителя 12 вновь по последовательным

адресам, начиная с первого, считываются коды адресов неисправных ячеек памяти.

При считывании нулевого сигнала с выхода второго накопителя 11 устрсйст-

во остается в режиме проверки текущего варианта разбиения массива ячеек памяги на группы. При этом по сигналу с блока 4 управленияпервый .формирователь 13 ., адреса формирует следующий адрес, по которому из третьегонакопителя 12 счн- тьшается код адреса следующей неисправной ячейки и т.д. После анализа последнего кода адреса неисправной ячейки, что фиксируется поступлением на вход блсжа 4 управления сигнала сравнения с выхода третьей схемы 14 сравнения, произЕ дится запись текущего значения кода управления в регистр 31 кода управления формирователя кода адреса, для чего на его третий вход 20 с выхода блока 4

управления поступает сигнал записи. Данный вариант разбиения массива ячеек памяти на группы (данный код управления/. обеспечивает нахождение в каждсй группе не более одной неисправной ячейки памяти. На этом устройство свою работу во втором режиме заканчивает.

В третьем режиме работы устройства производится запись кодов чисел и кодов адресов неисправных ячеек памяти в ячей-

ки памяти первого накопителя 3 , расположенных по щ - разрядным адресам групп, ф чэмкруемым в соответствии с зафиксированным кодом управления из сог ответствуюших записываемых п -разрядных кодов адресов неисправных ячеек памяти. При этом из третьего накопителя 12 по последовательным адресам, начиная с первсго , производится считывание кодов чисел и кодов неисправньк ячеек.

Как и во втором режиме, код адреса неисправной ячейки с первся о выхода 24 третьего накопителя 12 поступает на первый вход 18 формирователя 9 кода адре11SOса, с выхода 20 которого vv -разрядный код адреса группы ячеек памяти поступает на адресньй вход первого накопителя 3, По данному адресу в первый накопитель 3 производится запись кода адреса и кода числа неисправной ячейки, поступающих на его третий вход соответственно с первого 24 и второго 25 выходов третьего накопителя 12. После считывания и записи инф мации, соответствующей последнейнеисправной ячейке, что фиксирует поступление на вход блока 4 управлениясигнала сравнения с выхода третьей схемы 14 сравнения, устройство свою работу в третьем режиме заканчивает, В четвертом режиме производится конт роль с блокировкой неисправных ячеек памяти запоминающего устройства, в состав которого входит постоянный накопитель 3, регистр 2 числа, регистр 5 адреса, первый накопитель 3, первая схема 6 сравне ния, формирователь 9 кода адреса. Как и в первом режиме, по сигналу с блока 4 управления второй формирователь 16 адреса последовательно формирует коды адресов. Текущий код адреса поступает с вьсхода второго формирователя 16 адреса на вход эталонного накопителя 8, на вход контролируемого постоянного накопителя 34 и на первый вход 18 формирователя 9 кода-адреса, с выхода 2О которого m -разрядный код адреса группы, сфсрмированньй в соответствии с зафиксированным 3 регистре 31 кодом управления, поступает на вход первого накопителя 3, По этим адресам из эталонного накопителя 8, постоянного накопителя 34 и первого накопителя 3 производится считывание информации. При этом из первого накопителя 3 считывается код числа и код адреса неисправной ячейки памяти, котфая входит в группу ячеек памяти, имеющих данный код адреса группы. Код адреса неисправной ячейки памяти со вто рого выхода первого накопителя 3 поступает на второй вход первой схемы 6 сра внения, на первьй вход которой с выхода регистра 5 адреса, подается текущий код адреса. Сигнал сравнения данных кодов, подаваемый с выхода первой схемы 6 сравнения на вход блсжа 4 управления, факт обращения к неисправной ячейке памяти. При этом с выхода блока 4 управления на третий вход первого регистра 2 числа поступает сигнал, разрешающий запись информации с его вто- рого входа, на который поступает верный код числа с первого выхода первого накопителя 3. Сигнал несравнения с выхода первой схемы 6 сравнения фиксирует обращение к исправной ячейке, памяти проверяемого постоянного накопителя 34, при этом на третий вход первого регистра 2 числа поступает сигнал разрещения записи инффмадии с его первого входа, на который подается код числа, считанный с постоянного накопителя 34. Код числа с выхода эталонного накопителя 8 поступает на первый вход второй схемы 7 сравнения,на второй вход которой подается код числа с вькода первого регистра 2 числа. При обнаружении ощибки с выхода второй схемы сравнения на вход блока 4 управления поступает сигнал ошибки. При отсутствии ощибки устройство переходит к проверке следующего аареса. Пример, иллюстрирующий блокировку и замену неисправных ячеек памяти при использовании различных вариантов разбиения массива ячеек памяти на группы в зависимости от наборов адресов неисправных ячеек, приведен на фиг. 3. Пусть постоянный накопитель 34 концентрируемый имеет шестнадцать ячеек памяти (см. фиг. За), но разбиение массива ячеек памяти на четыре группы производится не вьщелением двух старших разрядов адреса (см, фиг. 36), а формированием двухразрядного кода апреса группы из четырехразрядного адреса ячейки памяти. Причем первый разряд кода адреса группы формируется суммированием по модулю 2 первого и второго разряда кода адреса ячейки памяти, а второй - суммированием третьего и четвертого разрядов. Из фиг. Зв видно, что в этом случае производится разбиение массива ячеек памяти на группы и возможна, например, одновременная блокировка и замена ячеек памяти с номерами -12 14, 8, 5( на фиг. Зв подчеркнуты), что нельзя было осуществить в предыдущем случае, так как ячейки памяти с номерами 12 и 14 входят в одну группу. Аналогично при варианте разбиения массива ячеек памяти на группы (фиг, Зв) возможна одновременная блокировка и подмена ячеек памяти с но3, которая не мерами О, осуществима ни в первом, ни во втором случае. Технико-экономическое преимущество предложенного устройства заключается в том, что в нем обеспечено автоматиче-

ское нахождение и фиксация варианта разбиения массива ячеек проверяемой посгоянной памяти на группы, содержащие не более одной неисправной ячейки, в зависимости от адресов неисправных ячеек, обнаруженных при контроле, и одновременную блокировку и подмену неисправных ячеек проверяемой памяти резервными, что повышает быстродействие устройства.

Формула изобретения

1. Устройство для контроля памяти,

содержащее два накопителя, первый регисгр числа, блок управления, регнсгр адреса, две схсЛы сравнения и эгалои-ньй накопитель, выход которого подключен к первому входу второй схемы сравнения, второй вход которой соединен с выходом первого регистра чр-:сла и с выходом устройства, выход регистра адреса соединен с адресным выходом усгройсгва и первым входом первой схемы, сравнения первый вход первого регистра числа подключен к Bxoiiy устройства, а второй вход соединен с пэрвык выходом первого накопителя, второй выход которого аошшючен ко второму входу первой схемы: сравнения а первьй вход к первому входу второго накопителя, вторые входы,накопителей, первый вход регистра адреса i третий вход регистра числа и выходы второго накопителя и схем сравнения соединены с соответствующими выходами и входами блока управления, отличающееся тем что, с целью повышения быстродействия устройства, оно содержит формирователь кода адреса, блок местного управления, третий накопитель, два формирователя адреса, третью схему сравнения, второй регистр чис71а и элемент ИЛИ, причем выход формирователя кода адреса подключен к первому входу первого накопителя, а первый вход - к выходу регистра адреса и первому входу третьего накопителя, второй вход которого соединен с выходом эталонного накопителя-, а третий вход - с выходом первого формирователя адреса и первыми входами второго регистра числа и третьей схемы сравнения, выходы третьего накопителя

подключены к третьему входу первого накопителя, причем первый выход - . jc первому входу элемента ИЛИ, второй вход которого соединен со входом эталонного

накопителя и выходом второго формирователя адреса, выходы второго регисгра числа и элемента ИЛИ подключены соответственно ко второму входу третьей схемы сравнения и ко входу регисгра адреса,

выход блока местного управления соединен со вторым входом формирователя ко- да адреса, третий вход которого, вход блока местного управления, четвертый вход третьего накопителя, вхЪды формирователей адреса, второй вход второго регисгра числа и вькод третьей схемы сравнения соединены с соответствующимн выходами и входом блока управления. 2. Устройство поп. 1, отличаго щ е е с я тем, что ффмирователь кода адреса содержит сумматоры по модулю два, второй элемент ИЛИ, регистр копа угфавления и элементы И, первые входы которых подключены к первому

входу, а первые входы втфого элемента ИЛИ и регистра кода управления - ко второму входу формирователя кода адреса, второй вход регистра кода угтравления и выходы сумматоров по модулю два соединены соответственно с третьим входом и выходами формирователя кода адреса, выход регистра кода управления подключен ко. второму входу второго элемента ИЛИ, выходы которого соединены со вторы ми входами элементов. И, выходы

подключены к соответствующим входам сумматоров - по модулю Два.

3. Устройство по п. 1, отличают е е с я тем, что блок местного управления вБ1полнен содержащим четвертый

накопитель и третий формирователь , адреса, выходы которого подключены ко входам четвертого накопителя, а вход и выходы четвертого накопителя соответственно ко входу и выходам блока местного управления.

Источники информации, принятые во внимание при экспертизе

1. Автсрское свидетельство СССР № 504250, кл. Q 11 С 29/ОО, 1976.

2. Авторское свидетельство СССР № 492000, кл. Q 11 С 29/00, 1974 (прототип).

Ь

zr

.2/,

т

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с блокировкой неисправных ячеек | 1983 |

|

SU1115108A1 |

| Устройство для контроля памяти | 1978 |

|

SU752497A1 |

| Двухуровневое оперативное запоминающее устройство | 1982 |

|

SU1043742A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU888214A1 |

| Устройство для обработки элементов сканерных изображений | 1983 |

|

SU1134945A1 |

| Устройство для контроля памяти | 1979 |

|

SU783855A1 |

| Устройство для контроля блоков оперативной памяти | 1981 |

|

SU957276A1 |

| Буферное запоминающее устройство | 1982 |

|

SU1105940A1 |

| Оперативное запоминающее устройство с самоконтролем | 1978 |

|

SU771731A1 |

| Запоминающее устройство с кор-РЕКциЕй пРОгРАММы | 1979 |

|

SU809400A1 |

(риг.2 -rf-ra V V-fif-g - ri sifts Ф 0 ОГ010 04 о 0 2p 004 00nOOnOOH 5p 0 000f n 00001 n p 00000 000 H U -I r Фиг.За 3p OOOOf j I OOOOi -H 4p 0 0 0 0 0 0 0 0 n n M -f I iri.S OOHGOHOO fl ЗрФ- рООООН M lU-I 0000 Фмг. 3S p®4pO p®3pOO H 00 004 4 -i 4 00 Ф(уг.32 I I ffi-jy Q 4 Q л -15 9 3 2 3 7 /y 5 0 /i 5 3 i 7 6 i§ 45a g 5j(f Й 0 ,5 6 745 9 8 44 40 45 4A -fb 2

Авторы

Даты

1981-02-28—Публикация

1979-05-03—Подача