подключен кинформационному выходу микропроцессора, управляннций вход Ы-го мультиплексора подключен кгп-му выходу регистра адреса операнда, выход « -го разряда регистра первого операнда подключен к входу j-го разряда (М+3) информационного входа первого мультиплексора. (М- Изобретение относится к вычислительной технике и может быть использовано в устройствах оперативного преобразования информации для редактирования (преобразования) информа- ции.

Целью изобретения является- повышение быстродействия.

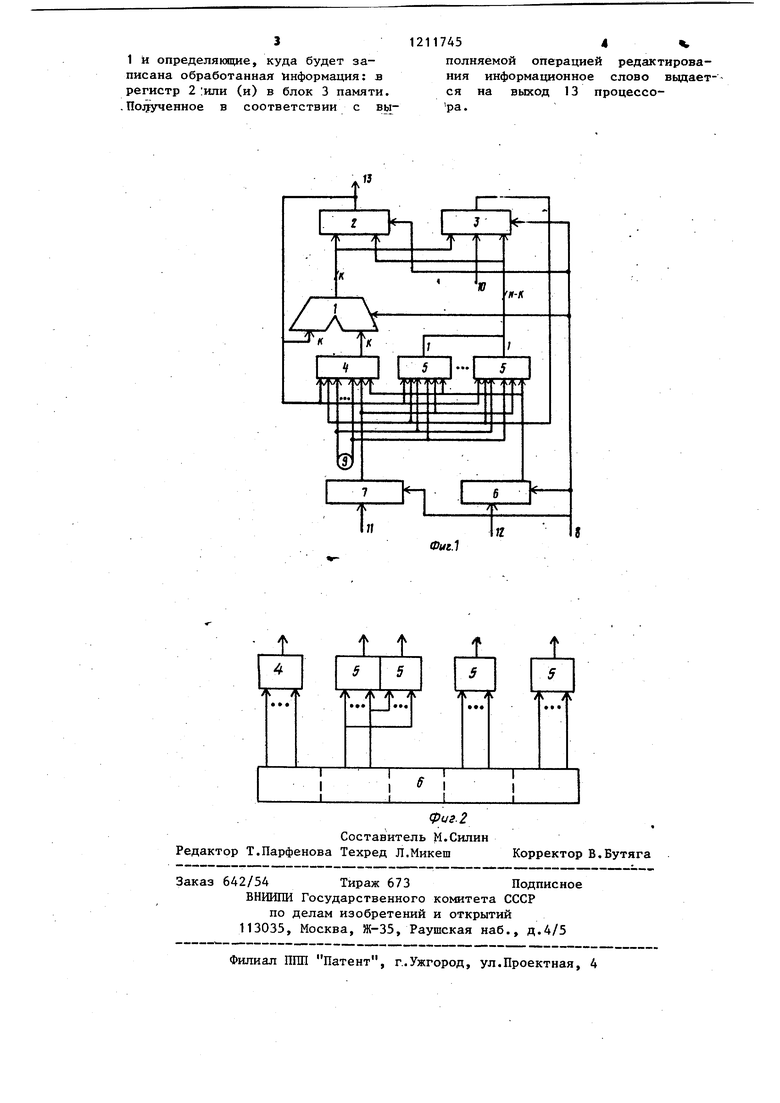

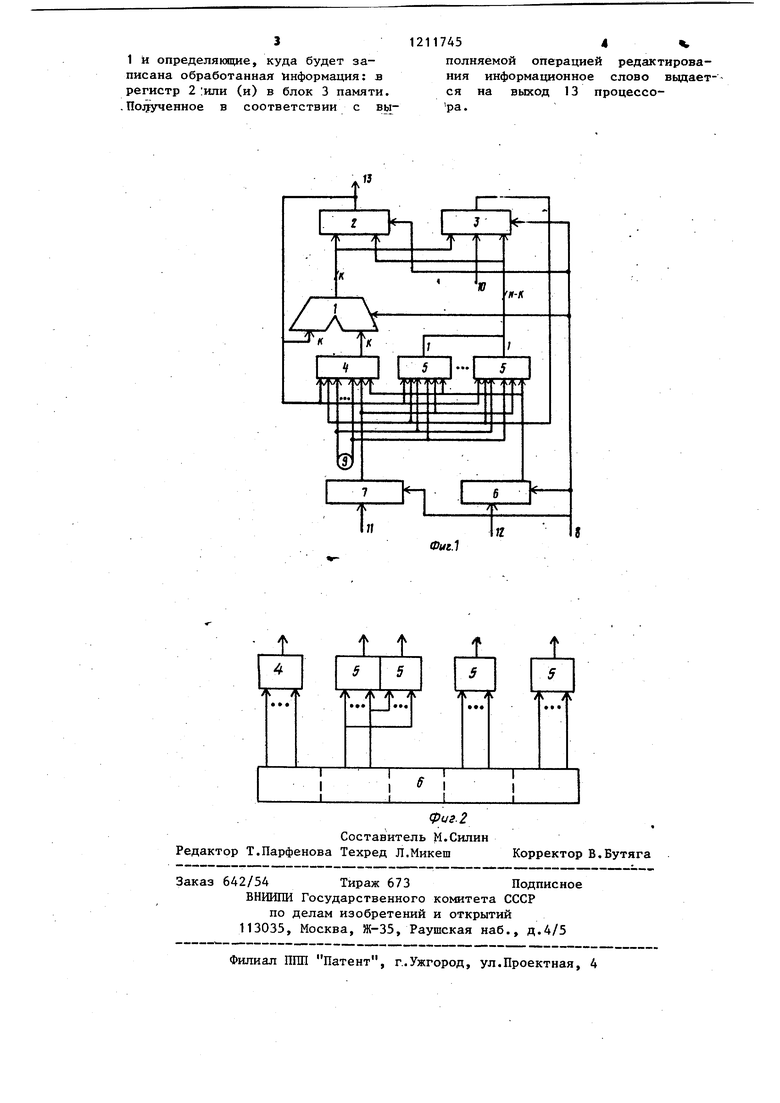

На фиг.1 изображена функциональная схема микропроцессораi на фиг.2- схема варианта объединения мультиплексоров в группы.

Микропроцессор содержит арифметико-логическое устройство 1, регистр 2 результата, блок 3 памяти, первый .мультиплексор 4, мультиплексоры 5, :регистр 6 адреса операнда, регистр 7 первого операнда, входы.: 8 - кода операции, 9 - информационный, 10 - адресный, 11 - первого операнда, 12 - адреса операнда микропроцессора выход 13 результата микропроцессора.

Регистр 6 управляет коммутацией информации, причем управление мультиплексорами осуществляется незави- симо, т.е. на их выходах могут формироваться сигналы с различных информационных направлений. Для этого регистр 6 условно разделен наМ-К+1 м -разрядных групп (по числу мульти- плексоров 5 и с учетом первого мультиплексора 4). Разрядность групп h определяется из условия

M + 3i2

гдеМ+3 - число информационных входов мультиплексоровJ М - - количество входов $. С целью уменьшения разрядности регистра 6 мультиплексоры 5 могут быть для конкретных реализаций процессора объединены в группы, каж+3)-й информационньш вход m-го мультиплексора подключен к выходу (т+ +К-1)-го разряда регистра первого операнда, информационный вход и син- хровход которого подключены соответственно к входу первого операнда и входу записи первого операнда входа кода операции микропроцессора.

5

5 0

5 0

5

дая из которых управляется соответ- ствуннцими выходами регистра 6 (фиг.2) .

По информационным входам 9 с раз-; личных направлений на входы мультиплексоров 4 и 5 поступают информационные слова, предназначенные для редактирования. Эти информационные слова в общем случае состоят из двух частей: части, предназначенной для обработки в арифметико-логическом устройстве 1, и части, которая не подвергается обработке в арифметико- логическом блоке 1. Редактирование информации заключается при зтом в изменении как первой, так и второй частей информационных слов в соответствии с конкретным алгоритмом редактирования.

Процессор работает следующим образом.

Перед началом операции редактирования управлякщим сигналом со входа 8 в регистр 7 заносится информация (константа), которую предполагают использовать в процессе редактирования, а в регистр 6 - коды, управляющие мультиплексорами 4 и 5, Эти коды позволяют подключить один из М+3 информационных входов мультиплексоров на их выходы. В результате на выходах мультиплексоров формируется новое информационное слово (например, на выходы мультиплексора 4 поступает информация от 1( младших разрядов регистра 2, на выходы первого и второго мультиплексоров 5 информация с К +1 и k+2 разрядов регистра 7 и т.д. в соответствии с программой редактирования).

Затем по входу 8 поступают управляющие сигналы, задающие операцию в арифметико-логическом устройстве

312117454

1 и определякщие, куда будет за- полняемой операцией редактироваписана обработанная Информация: в регистр 2 :или (и) в блок 3 памяти. . IIojyyMeHHoe в соответствии с выния информационное слово вьщается на выход 13 процессо ра.

(риг. 2

Составитель М.Силин Редактор Т.Парфенова Техред Л.Микеш

642/54 Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ПИП Патент, г..Ужгород, ул.Проектная, 4

полняемой операцией редактирования информационное слово вьщается на выход 13 процессо ра.

Корректор В.Бутяга

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессор | 1985 |

|

SU1330634A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Микропроцессор | 1983 |

|

SU1141419A1 |

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Адресное устройство для цифрового фильтра | 1985 |

|

SU1298859A1 |

| Микропроцессор | 1984 |

|

SU1179363A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| МОДУЛЬНОЕ ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО С РАЗДЕЛЬНЫМ МИКРОПРОГРАММНЫМ УПРАВЛЕНИЕМ АРИФМЕТИКО-ЛОГИЧЕСКИМИ СЕКЦИЯМИ | 1994 |

|

RU2079877C1 |

| Прангишвили И.В | |||

| Микропроцессоры и микроэвм | |||

| М.: Энергия, 1978, с.70 | |||

| Березенко А.И | |||

| и др | |||

| Микропроцессорные комплекты повышенного быст- родействия | |||

| М.: Радио и связь, 1981, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

Авторы

Даты

1986-02-15—Публикация

1984-07-09—Подача