1

Изобретение относится к вычислительной технике и предназначено для использования в монолитных интегральных запоминающих устройствах различного назначения.

Известен запоминающий элемент на взаим6допопняю1дих ЛЩП-транзисторах статического типа для интегральных запоминающих устройств, содержащий два интегратора, объединенных перекрестными связями, представляюгди.х собственно триггер и схему управления, состоящую из четырех дополнительных транзисторов l .

Недостаток этого запоминающего элемента - больщое количество шин (две шины питания и три информационные) и сложная схема управления. При реализации такого запоминающего элемента в интегральном исполнении увеличивается занимаемая площадь на кристалле полупроводника и снижается надежность работьи

Известны еще четыре типа запоминающих элементов на взаимодополняющих

МДП-транзисторах, содержащих собственно триггер и схему управления. Они отличаются друг от друга количеством транзисторов в схеме управления и количеством управляющих шин 2 .

Однако даже наиболее простой из этих элементов, состоящий из триггера и одного транзистора управления, содержит две шины питания и две информационные (управляющие) шины.

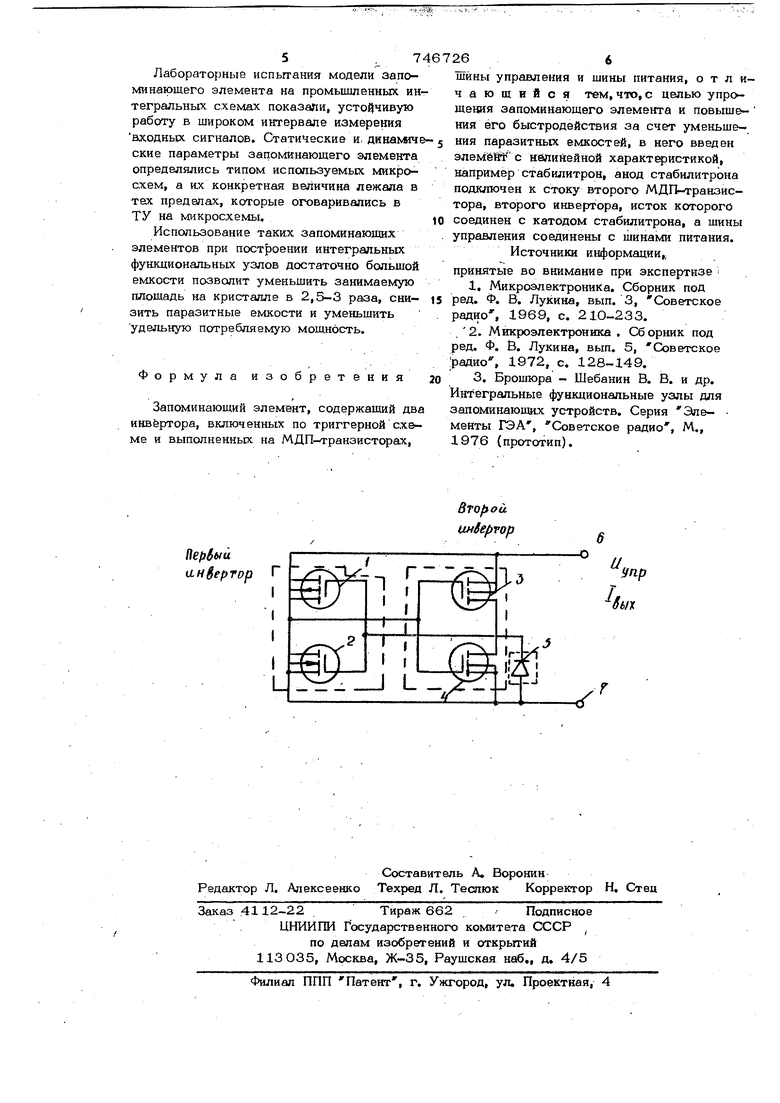

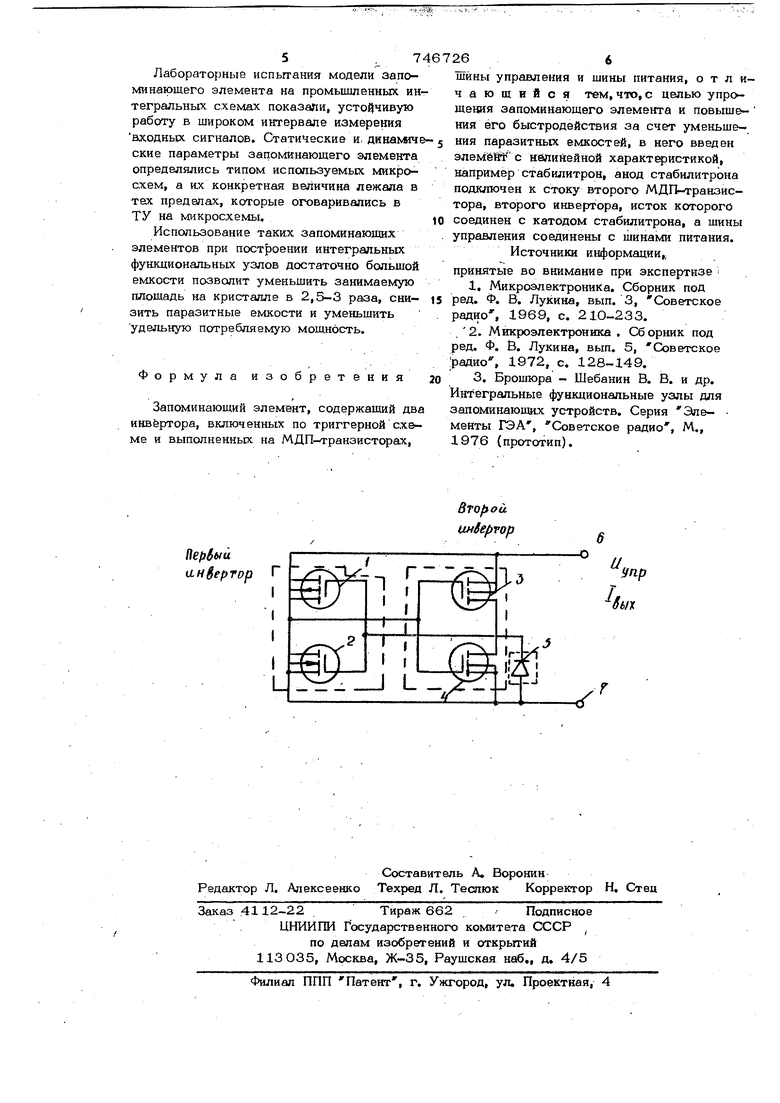

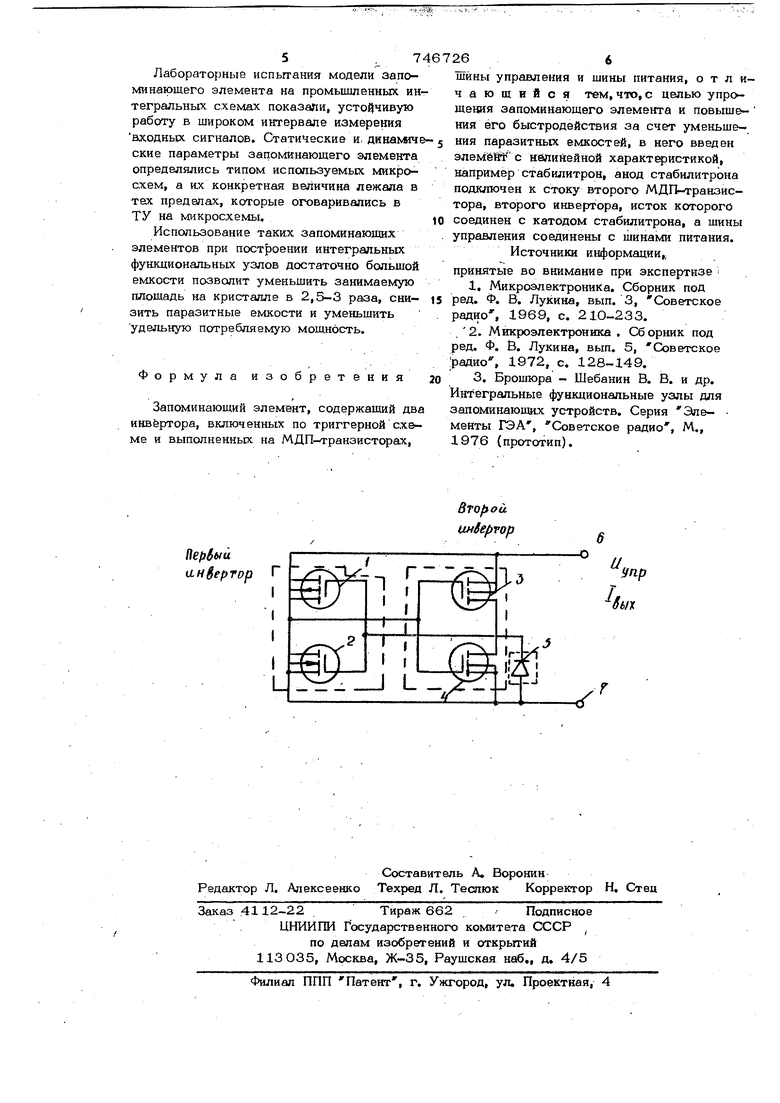

Наибопее близким к предлагаемому является -запомицающий элемент статического типа на взаимодополняющих МДП-транзисторах, который содержит два инвертора на взаимодополняющих МДП- ранзисторах, объединенных перекрестными связями, и дополнительный управляющий МДП-транзистор, сток которого соединен со средней точкой одного КЗ и ерторов, а исток и затвор подключены, соответственно, к разрядной и адресной щинам. В режиме хранения информации на затворе управляющего транзистора поддерживается положительный потенциал, который закрывает транзистор. При записи информации на адресную шину подается импульс отрицательной, а йа разрядную - положительной поля ности при записи кода I или нулевой пр записи кода О. Считывание информации осуществляется подачей импульса отрицательной полярности в адресную шину. Вели чина считьтающего импульса выбирается . Из условия неразрушающего считывания (Uc.,5-l,5 В). Этот запоминающий элемент потребляет очень малую мощность при хранении информации (единицы микроватт) и имеет достаточно высокое быстро действие 1J3 . Недостатки этого элемента заключаются в том, что он имеет большое количество шин (две шины питания, адресную и разрядную шины) и сложен в управлении, поскольку для его нормальной работы требуется подавать сигналы управления, совпадающие во времени в адресной и разрядной шинах, одновременно от двух фор-, мирующих устройств. При создании функциональных запоминающих узлов большой емкости в интегральном исполнении на таких элементах увеличивается занимаемая площадь на кристалле и паразитные емкости, снижается быстродействие и надежность. Цель изобретения - упрощение запоминающего элемента и повышение его быстродействия за счет уменьшения паразитных емкостей. Поставленная цель достигается тем, что в запоминающий элемент, содержашлй два инвертора, включенных по триггерной схеме ti выполненных на МДП-транзисторах, шины управления и шины питания, введен элемент с нелинейной характеристи кой, например стабилитрон, анод стабйлитройа подключен к /столу второго МДПтранзистора, второго инвертора, исток которого соединен с катодом стабилитрона, а шины упраЁления соединены с шинами питания. На чертеже представлена электрическая схема запоминающего элемента. Запоминающий элемент состоит из двух инверторов, первый из которых выполнен на МДП-транзисторах 1,2, второй - на МДП-транзисторах 3,4, элемента с нелинейной характеристикой, например стабилитрона 5, шин 6, 7 питания. Транзисторы в инверторах выбирают таким образом, что отношение произведения суммарной проводимости транзистора 4 и шунтирующего его стабилитрона 5 на провбТдимость транзистора 1 противоположного типа в соседнем инверторе к произведению проводимостей двух други.х транзисторов 2 и 3, меньше единицы при напряжэнии равном или меньше напряжения хранения, а при напряжении- равном или большем напряжения записи это отношение единицы. Запоминающий элемент работает следующим образом. В режиме хранения информации на шине 6 поддерживается положительный потенциал U у I величина которого больше порогового напряжения каждого из транзисторов 1,2,3,4 и меньше напряжения открывания стабилитрона 5. Если в запоминающем элементе хранится код , то этому соответствует низкий потенциал на выходе первого инвертора (сток транзистора 1) и высокий - на выходе второго (сток транзистора 4). При записи кода О в шину 6 подается положительный импульс, величина которого превышает напряжение открывания стабилитрона.Тогда стабилитрон открьюается и шунтирует транзистор 4. При этом напряжение на выходе второго инвертора уменьшается и триггер переходит во второе устойчивое состояние, т.е. устанавливается низкий потенциал на выходе второго инвертора и высокий - на выходе первого. При снятии импульса триггер сохраняет это состояние. Для записи кода в шину 6 подается импульс отрицательной полярности, величина которого уменьшается от О, при этом триггер перебрасывается в состояние 1 за счет того, что отношение произведения суммарной проводимости транзистора 4 и шунтирующего его стабилитрона 5 на проводимость транзистора 1 к произведению проводимостей двух других транзисторов 2 и 3 меньше единицы. Считьшание информации осуществляется подачей импульса, положительной полярности в шину 6, амплитуда которого выбирается из условия наразрушающего считьшания (DCH 0,7ЛЬгран-), при этом в шине течет большой информационный ток, если, в триггере хранится код , а малыйесли в триггере код О. Таким образом, использование в запоминающем элементе с нелинейной характеристикой стабилитрона позволяет сократить общее количество информационньк шин до минимального (две шины, включая шины источника питания), упростить управление запоминающим элементом и получить положит ЕЭТЬНЬЙ технико-экономический эффект.

Лабораторные испытания модели запоминающего элемента на промьшшанных интегральных схемах показапи, усто чивую работу в широком интервале измерения входных сигналов. Статические и, дикакмче ские параметры запоминающего элемента определялись типом используемых микросхем, а ах конкретная величина лежала в те.х пределах, которые оговаривались в ТУ на микросхемы,

Использование таких запоминающих элементов при пост роении интегральных функциональных узлов достаточно большой емкости позволит уменьшить занимаемую площадь на кристалле в 2,5-3 раза, онизить паразитные емкости и уменьшить удельную потребляемую мощность.

Формула изобретения зо

Запоминающий элемент, содержащий два инвертора, включенных по триггерной схеме и выполненных, на МДП- ранзистсрах,

шины управления и шины питания, отлчающийся тем, что, с целью упрощения запоминающего элемента и повышения его быстродействия за счет уменьшения паразитных емкостей, в него введен элемёйг с нелинейной характ истикой, например стабилитрон, анод стабилитрона подключен к стоку второго МДП- ранзистора, второго инвертора, исток которого соединен с катодом стабилитрона, а шины управления соединены с шинами питания.

Источники информации,, принятые во внимание при экспертизе

1. Микроэлектроника. Сборник под ред. Ф. В. Лукина, вып. 3, Советское радио , 1969, с. 210-233.

2, Микроэлектроника , Сб орник под ред. Ф. В. Лукина, вып, 5, Советское радио, 1972, с. 128-149,

3, Брошюра - Шебанин В. В. и др. Интегральные функциональные узлы для запоминающих устройств. Серия Эле- менты ГЭА, Советское радио , М,, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающий элемент | 1979 |

|

SU773738A1 |

| Запоминающий элемент | 1978 |

|

SU788174A1 |

| Квазистатическая ячейка памяти | 1975 |

|

SU598119A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| ИСТОЧНИК ПИТАНИЯ НЕЛИНЕЙНОЙ ИЛИ ЛИНЕЙНОЙ НАГРУЗКИ | 2021 |

|

RU2768272C1 |

| Устройство для выборки информации | 1981 |

|

SU1014029A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Элемент памяти | 1989 |

|

SU1635214A1 |

| Запоминающее устройство с перезаписью информации | 1974 |

|

SU570920A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

Пербый anSepTop Г

inp

г 6Ы1

Авторы

Даты

1980-07-05—Публикация

1978-04-10—Подача