Ш

ND

,-S

;о

/

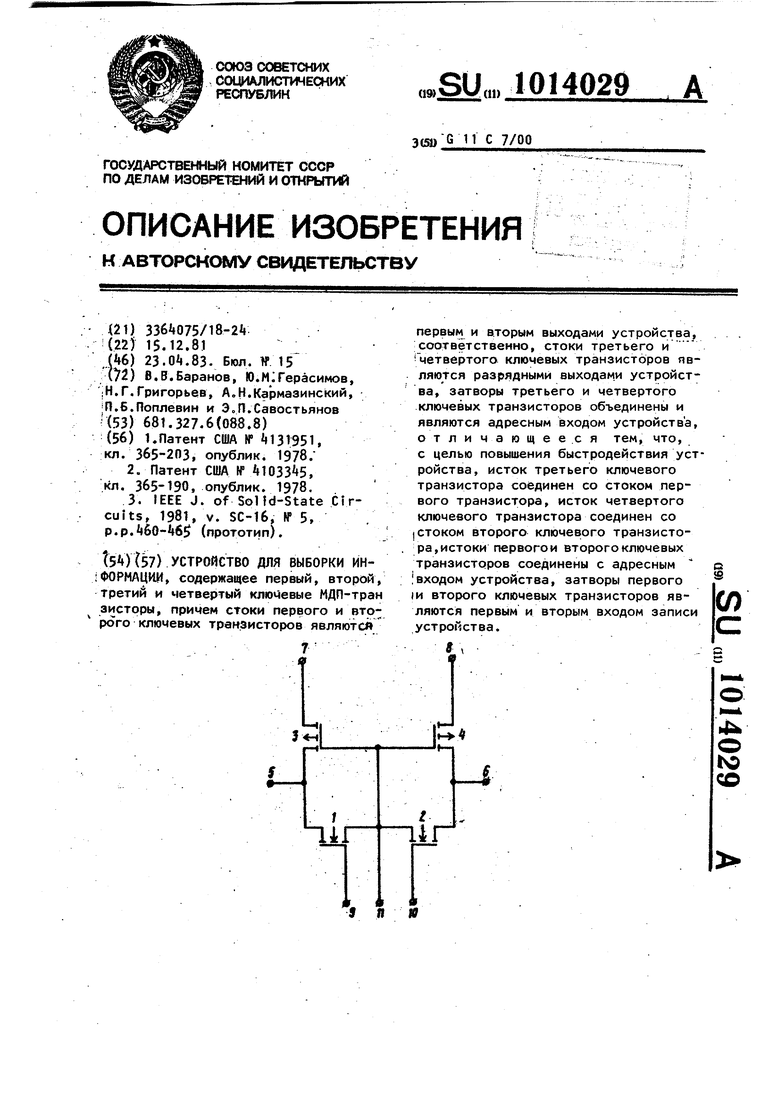

14 Г i Изобретение относится к вычислительной технике и может быть исполь зовано при построении микр6мощных1 интегральных запоминающих устройств на дополняющих МДП-транзисторах. . Известны устройства для выборки информации для оперативного запомин ющего устройства (ОЗУ на дополняющих МДП-транзисторах, содержащие два ключевых транзистора, две выходные и две разрядные шины, а также адрес ную шину, причем стоки ключевых тра зисторов соединены с внешними разрядными шинами, ИСТОКИ - с внутрен ними разрядными шийами l или шиной питания через дополнительные транзисторы 2 © Недостатком этих устройств является низкое быстродействие. Наиболее близким к изобретению по технической сущности является устрой ство д-ля выборки информации для ОЗУ на дополняющих МДП-транзисторах, со держащее два транзистора записи, два ключевых транзистора, два выходных транзистора и две разрядные шины, две шины, записи и адресную шину ЗТ : Недостатком известного устройства является низкое быстродействие обусловленное задержкой сигнала считывания,на транзисторе, включенном между ключевым транзистором и разрядной шиной. Цель изобретения - повышение быстродействия устройства для выборки информации для ОЗУ на дополняющих МДП-транзисторах. Поставленная цель достигается тем что в устройстве для выборки информации , содержащем первый, второй, третий и четвертый ключевые МДП-тран зисторы, причем стоки первого и второго ключевых транзисторов являются первйм и вторым выходами устройства, соответственно, стоки третьего и четвертого ключевых транзисторов являются разрядными выходами устройства, затворы третьего и четвертого ключевых транзисторов объединены и являются адресным входом устройства, исток третьего ключевого транзистора соединен со стоко .первого ключевого транзистора, исток четвертого ключевого транзистора со стоком второго ключевого транзистора, истоки первого и второго ключевых транзисторов соединены с адресным входом устройства, затворы первого и второго ключевых транзисторов являю мя первым и вторым входом записи устройства. На чертеже представлена принципиальная электрическая схема предлагаемого устройства. Устройство содержит первый 1 и второй 2 ключевые транзисторы первого типа проводимости. Третий 3 и четвертый Ц ключевые транзисторы второго типа проводимости, первый 5 и второй 6 выходы устройства, разрядные выходы 7 и 8, первый 9 и второй 10 входы и адресный вход 11. Устройство для выборки информации для ОЗУ на дополняющих МДП-транзисторах работает следующим образом. В режиме записи к адресному входу 11 и одному из входов записи, например 10, приложен сигнал логического нуля, а к входу 9 записи - сигнал логической единицы. При этом транзисторы 3 и 4 открыты по затвору, транзистор 2 закрыт, а транзистор 1 открыт, разряжая выход устройства 5 до уровня логического нуля. Таким образом обеспечивается запись логического нуля. Запись логической единицы обеспечивается подачей сигнала логического нуля на адресный вход 11 и вход 9 записи и подачей сигнала логической единицы на вход 10 записи. При считывании информации на адресный вход 11 и входы 9 и 10 записй подается сигнал логического нуля. . Транзисторы 1 и 2 при этом закрыты, а транзисторы 3 и открыты, обеспечивая прохождение сигнала считывания с выходов устройства 5 и 6 на разрядные входы 7 и 8. В устройстве для выборки информации повышение быстродействия достигается исключением ключевых транзисторов из тракта записи, подключением транзисторов 1 и 2 непосредственно к выходам устройства. Исключение ключевых транзисторов из тракта записи позволяет увеличить уровень полезного сигнала на выходах устройства за счет устранения потерь на паразитных сопротивлениях и емкостях разрядных шин {особенно важно для интегральных микросхем запоминающих устройств с большой информационной емкостью ) и последовательно включенных ключевых транзисторах. При этом условия записи легко могут быть обеспечены соответствующим выбором размеров транзисторов записи и транзисторов выходного каскада дешифратора

3 Qlk023

столбцов; Сведение к минимуму влияния максимальным конструктивным приблипараэитных сопротивления и емкостей . жением тра 13исторЬв записи к заломивнутренних разрядных шин достигается нающим элементам.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выборки информации из блоков памяти | 1984 |

|

SU1153357A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1982 |

|

SU1062785A1 |

| Усилитель считывания на дополняющих МДП-транзисторах | 1981 |

|

SU963087A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Ячейка памяти | 1976 |

|

SU681455A1 |

| Дешифратор на МДП-транзисторах | 1986 |

|

SU1325558A1 |

| Усилитель считывания | 1980 |

|

SU928406A1 |

| АДРЕСНЫЙ ФОРМИРОВАТЕЛЬ НА МДП-ТРАНЗИСТОРАХ | 1991 |

|

RU2088979C1 |

| Ячейка памяти (ее варианты) | 1982 |

|

SU1070604A1 |

УСТРОЙСТВО ДЛЯ ВЫБОРКИ ИН;ФОРМАЦИИ, содержащее первый, второй, третий и четвертый МДП-тран зисторы, причем стоки первого и второ го ключевых транзисторов являютсй первым и вторым выходами устройства, соответственно, стоки третьего и iчетвертого ключевых транзисторов являются разрядными выходами устройства, затворы третьего и четвертого ключевых транзисторов объединены и являются адресным входом устройства, отличающееся тем, что, с целью повышения быстродействия устройства, исток третьего ключевого транзистора соединен со стоком первого транзистора, исток четвертого ключевого транзистора соединен со стоком второго ключевого транзистора, истоки первогои второго ключевых транзисторов соединены с адресным входом устройства, затворы первого ж второго ключевых транзисторов являются первым и вторым входом записи устройства. ч .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| of Solfd-State Circuits, 1981, V | |||

| Устройство для электрической сигнализации | 1918 |

|

SU16A1 |

| p.p | |||

| (прототип) | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1983-04-23—Публикация

1981-12-15—Подача