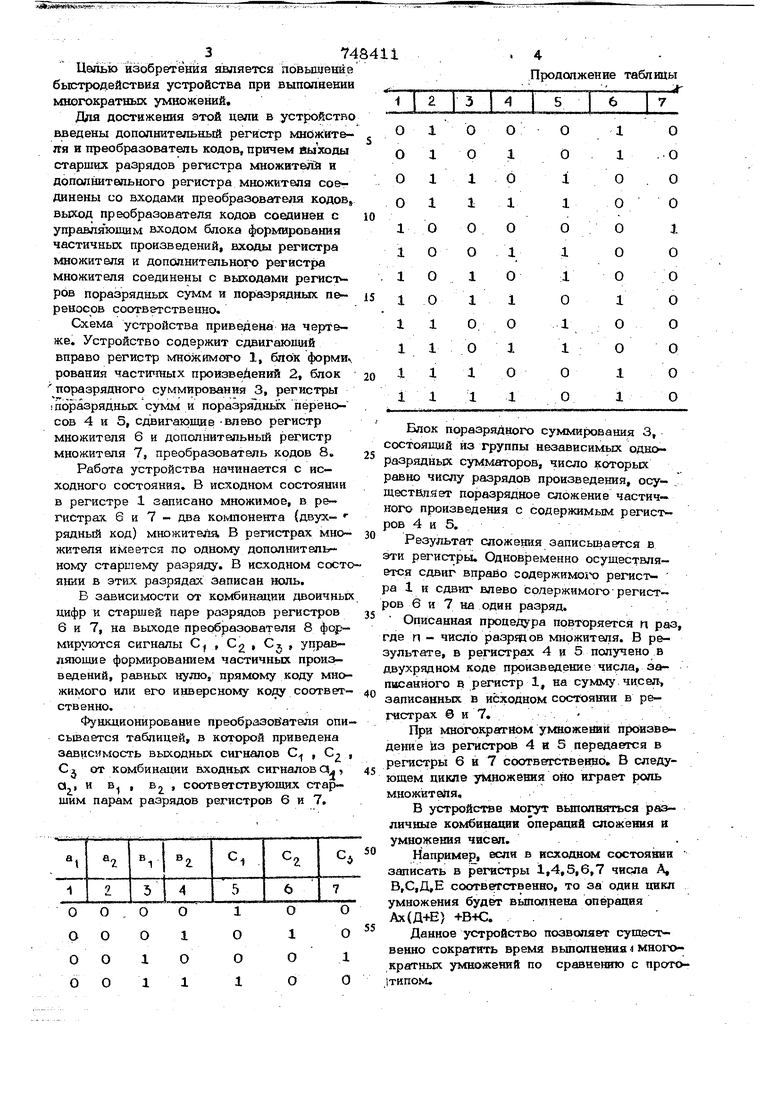

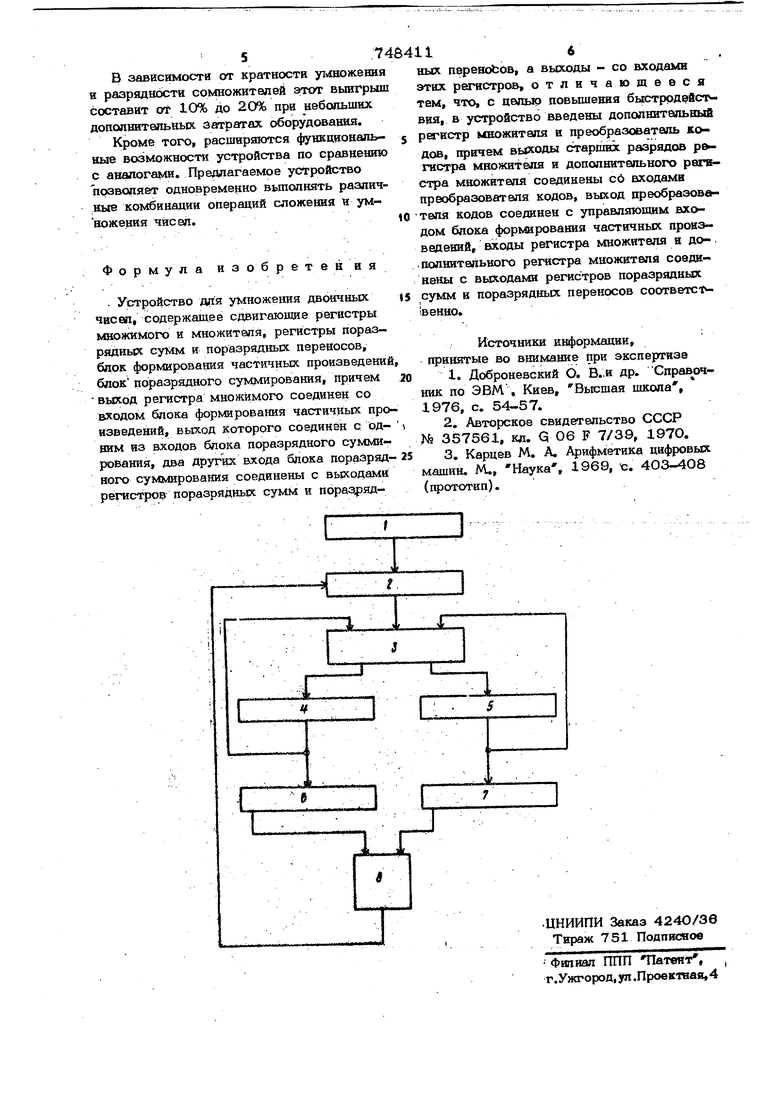

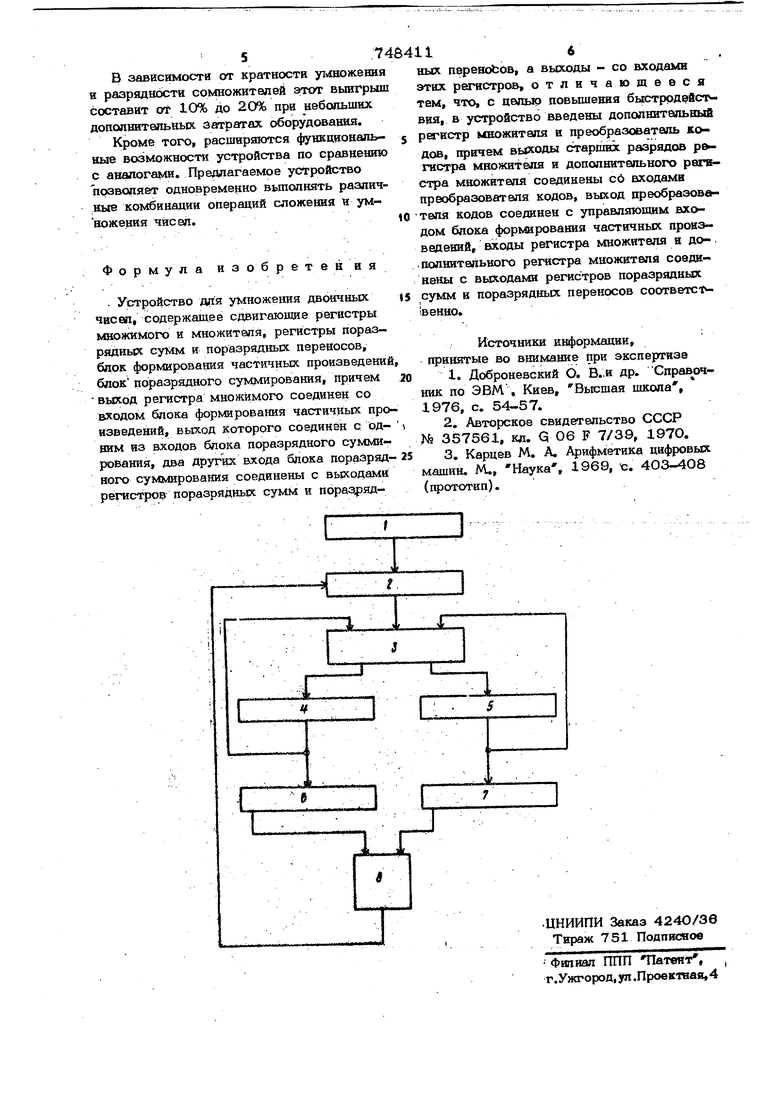

Изобретение относится к области выч слительной техники и может быть исполь зовано в арифметических устройствах спв циализированнь1х цифровых вычислительны машин. Известны устройства содержащие регистры множимого и множителя, схему формирования частичных произведений, блок суммирования частичных произведений. Умножение в таках устройствах начинается с младших разрядов множителя 1 . 2 . . Недостатком известных устройств является недостаточное быстродействие в связи с затратами времени на приведение двухрядного кода произведения. Наиболее близким к изобретению явля ется устройство для умножения двоичных чисел 3 , содержаш:ее сдвигающие р&гистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формирования частичных произведений, блок поразрядного суммиро вания. Кроме этого в устройстве выход старшего разряда регистра множителя соединен с управляющим входом блока формирования частичных произведений, информационный вход которого соединен с выходом регистра множимого, а выход с одним из входов блока поразрядного суммирова ния,два других входа которого соединены с выходами регистров поразрядных сумм и поразрядньрс переносов , а выходы - со входами ЭТИ.Х регистров. Умножение в данном устройстве осущ&ствпяется, начиная со старшах разрядов множителя. Это устройство имеет некоторое преимущество перед вышеупомянутыми устройствами, так как метод умножения со старших разрядов облегчает совмещение устройства умножения с устройством деления и позволяет одновременно с умножением выполнять суммирование. Недостатком устройства является недостаточное быстродействие в связи с затратами времени на приведение двухрядного кода произведения. 37 Целью изобретения является повышение быстродействия устройства при выполнени многократных умножений. Для достижения этой цели в устройств введены дополнительный регистр мнбжйтеля и преобразователь кодов, причем выходы старших разр5щов регистра множители и дополнительного регистра множителя соединены со входами преобразователя кодов выход преобразователя кодов соединен с управпяюлшм входом блока формирования частичных произведений, входы регистра множителя и дополнительного регистра множителя соединены с выходами регист ров Поразрядных сумм и поразрядных п©реносрв соответственно. Схема устройства приведена на чертеже. Устройство содержит сдвигающий вправо регистр множимого 1, блок форми рования частичных произведений 2, блок поразрядного суммирования 3, регистры (Поразрядных сумм и поразрядный, перёносов 4 и 5, сдвигающие влево регистр множителя 6 и дополнительный регистр множителя 7, преобразователь кодов 8, Работа устройства начинается с исходного состояния. В исходном состоянии в регистре 1 записано множимое, в регистрах 6 и 7 - два KosvfflOHeHTa {двух- рядный код) множителя В регистрах множителя имеется л о одному дополнительному старшему разряду. В исходном состо янии в этих разрядах записан ноль. В зависимости от комбинации двоичны цифр и старшей паре разрядов регистров 6 и 7, на выходе прес разователя 8 формируются сигналы С , Cg , C-t, , управ- Л5пощие формированием частичных произведений, равных нулю, прямому коду множимого или его инверсному коду соответственно. Функционирование преобразоватеяя опи сывается таблицей, в которой приведена зависимость выходных сигналов 0,0 Cj от комбинации входных сигналов С|, а,, и в , В2 , соответствующих старшим парам разрядов регистров 6 и 7. 1 Продолжение таблщы Блок поразрядного суммирования 3, состоящий из группы независимьЕх одноразрядных сумматоров, число которых равно числу разрядов произведения, осуществляет поразрядное сложение частичного произведения с содержимым регистров 4 и 5. Результат сложения записывается в эти регистры. Однов|эеменно осуществляется сдвиг впрайо содержимоях) регист- а 1 и сдвиг влево содержимого регистов 6 и 7 на один разряд. Описанная процедура повторяется п раз, где п - число разрядов множителя. В результате, в регистрах 4 и 5 получено в двухрядном коде произведение числа, записанного в регистр 1, на сумму чисел, записанных в исходном состоянии в регистрах 0 и 7. При многократном умножений произведение из регистров 4 и 5 передается в регистры 6 и 7 соответстве нно, В следующем цикле умножения оно играет роль множителя, В устройстве могут выполняться различные комбинации операций сложения и умножения чисел. Например, если в исходн %1 состоянии записать в регистры 1,4,5,6,7 числа А, В,С,Д,Е соответственно, то за один цикл умножения будет выполнена операция Ах(Д+Е) +В+С.. Данное устройство позволяет существенно сократить время выполнения-i многократных умножений по сравнению с прототипом. В зависимости от кратности у1лнонсения и разрядности сомножитвпей этот вьшгрыш составит от 10% до 20% при небольших дополнительных затратах оборудования. Кроме того, расширяются функциональные возмонсности устройства по сравнению с аналогами. Предлагаемое устройство позволяет одновременно вьшолнять различные комбинации операций сложения и умножения чисел. Формула изобретення . Устройство для умножения двоичных чисеи, содержащее сдвигающие регистры множимого и множителя, регистры поразрядных сумм и поразрядных переносов, блок формирования частичных произведений блок поразрядного суммирования, причем выход регистра множимого соединен со входом блока формирования частичных про изведений, выход которого соединен с одииМ из входов блока поразрядного суммирования, два других входа блока пораарядного су1уширования соединены с выходами регистров поразрядных сумм и пораз зядных перевоЬов, а выходы - со входами этих регистров отличающееся тем, что, с целыр повышения быстррдейст ВИЯ, в устройство введены дополнительный регистр множителя и преобразователь кодов, причем выходы старшвос разрядов регистра множителя и дополнительного регвстра множителя соединены ей входами преобразователя кодов, выход преобразов теля кодов соединен с управляющим входом блока формирования частичных произведений, аноды регистра множителя и дополнительного регистра множителя соединены с выходами регистров поразрядных сумм и поразрядных переносов соответс венно. Источники информации, принятые во внимание При экспертиза 1. Доброневский 6. В.,и др. Справ очник по ЭВМ , Киев, Вьюшая школа , 1976, с. 54-57. 2.Авторское свидетельство СССР 357561, кл. (3 06 F 7/39, 1970. 3.Карцев М. А, Арифметика цифровых ашин. М,, Наука, 1969, t. 403-408 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения двоичных чисел | 1978 |

|

SU748412A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1978 |

|

SU767761A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Конвейерное множительное устройство | 1981 |

|

SU1043642A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ | 1991 |

|

RU2021633C1 |

| Устройство для вычисления сумм произведений | 1975 |

|

SU551643A2 |

Авторы

Даты

1980-07-15—Публикация

1978-05-22—Подача