(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО БЕЗ РАЗРУШЕНИЯ

ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1979 |

|

SU849301A1 |

| Запоминающее устройство со считыванием без разрушения информации | 1979 |

|

SU773724A1 |

| Устройство для ввода информации | 1983 |

|

SU1117628A1 |

| Запоминающее устройство | 1983 |

|

SU1117709A1 |

| Опреративное запоминающее устройство | 1976 |

|

SU645204A1 |

| Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1977 |

|

SU693438A1 |

| Оперативное запоминающее устройство | 1983 |

|

SU1095233A1 |

| Запоминающее устройство | 1983 |

|

SU1115105A1 |

| Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах | 1979 |

|

SU773731A1 |

| Устройство для откладки программ | 1987 |

|

SU1474656A1 |

1

Изобретение относится к области цифровой вычислительной техники и может быть использовано в запоминающих устройствах без разрушения информации.

Известно запоминающее устройство без разрушения информации на многостверстных ферритовых элементах, содержащее коммутационные поля для подключения оборудования записи информации. Запись информации осуществляется кратковременным касанием щтеккера к контактам записи или с помощью выносного контактора с двадцатью контактами, перемещающегося по контактному полю 1.

Недостатком указанного устройства является возможность разрушения информации при неправильном контактировании в процессе записи из-за отсутствия контроля коммутации.

Наиболее близким к предлагаемому по технической сущности является полупостоянное запоминающее устройство на тороидальных магнитных сердечниках с диаметральными отверстиями, которое содержит блок управления, п запоминающих блоков с входными коммутационными элементами, адресные и разрядные формирователи токов

записи с выходными коммутационными элемента.ми, которые в режиме зап.иси подключены к входным коммутационным элементам одного из запоминающих блоков, и дешифратор запоминающих блоков 2.

Цель изобретения - повышение надежности устройства путем защиты информации при неправильной коммутации.

Указанная цель достигается тем, что в запоминающее устройство без разрушения информации, содержащее блоки памяти, первые входы которых через коммутационные элементы соединены с выходами разрядных и адресных формирователей токов записи, дещифратор выбора блоков памяти, вход которого соединен с первым выходом регистJ5 ра адреса, дешифратор записи, вход которого соединен со вторым выходом регистра адреса, выходы дешифратора записи соединены с одними из входов адресных формирователей токов записи, третий выход регистра адреса подключен ко вторым входам блоков памяти, блок управления, выход которого соединен с третьими входами блоков памяти, со входами разрядных формирователей токов записи и другими входами адресных формирователей токов записи, введен

блок анализа коммутации, соединеииый с блоком управлеи(я, входы блока анализа коммутации через :оммутациояиие элементы, соединены с четг ертыми входами блоков памяти, выходы дешифратора выбора блоков памяти соединены с 1 ятыми входами блоков памяти, блок анализа коммутации состомт из элемеггга И н триггера, одни из входов которого соединен с выходом элемента И, входы элемента И и другой вход триггера соединены со входами блока анализа коммутации, выход триггера соединен с выходом блока анализа комр,утан,ич, а каждый блок содержит 1аг олитель, коммутационные элементы, депгифратор считывания, элемен,т И и адресный формирователь токов считывания, выход которого соединен с одним из входов акопителя, другие входы накопителя соединены с первыми выходами коммутационных элементов, входы которых соединены с первыми и четвертыми входами блока иамяти, вторые выходы коммутационных злемеи1ов соединены с одним на 1 ходов элемента И. и с пятым входом блока памьти, вь(ход элемента И соединен с первым входом дешифратора сч1ггывания, второй вход которого подключен ко второму входу блока памяти, дузугой вход элемента И соеди ен с третьим входом блока иамяти, в|)1ход дешифратора считы.ва,чия соедннеи со входом адресного формирователя токов считывания.

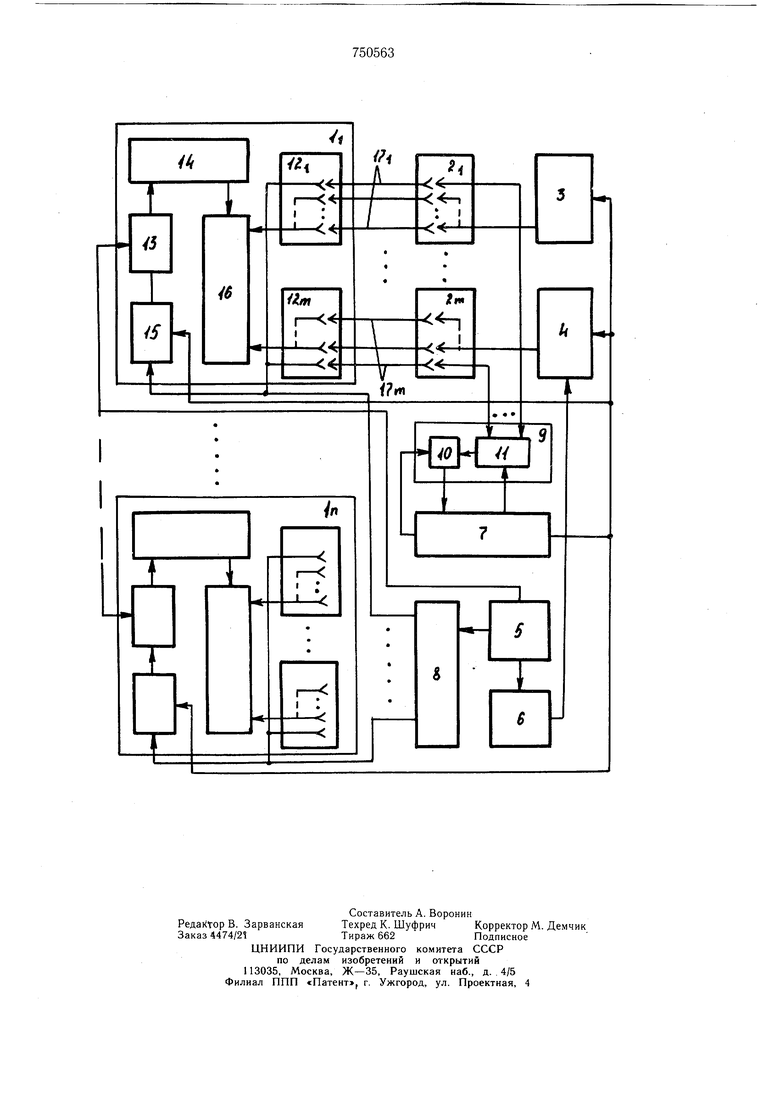

На чертеже изображена блок-схема гфедлагаемого устройства.

Оно содержит блоки 1, иамяти, коммутационные элементы 2,-2т, разрядные и адресные формирователи 3 и 4 токов записи, регистр 5 адреса, дешифратор 6 записи, блок 7 управления, дешифратор 8 выбора блоков памяти, блок 9 анализа коммутации, который выполнен на триггере 0 и элемеите II И. Каждый блок памяти содержит коммутационные элементы 12, -12„, дешифратор 13 считывания, адресный формирователь 14 токов считыва}И1я, элемент 15 И,накопитель 16, соединительные кабели 17,-17„.

Устройство работает следующим образом.

В режиме считывания блок 7 управления устанавливает триггер 10 блока 9 анализа коммутации в нулевое состояние, которое не меняется из-за отсутствия опроса элемента 1 1 И блоком 7 управления. В соответствии с кодом адреса, установленном в регистре 5 адреса, вырабатывается разрешающий нотенциал .на одном из выходов дешифратора 8 выбора блоков памяти, поступающего на вход элемента 15 И соответствующего блока I памяти, который пропускает на вход дешифратора 13 сигпал опроса, вырабатываемый блоком 7 управления. В результате этого опрашивается дешифратор 3 считывания, который в соответствии с кодом адреса на других его входах производит выборку адресных формирователей 14 токов считывания, возбуждающих токи опроса в накопителе 6.

В режиме записи блок (шмяги, в котором необходимо записать информацию, например блок ii, подключен разъемами 12 1-12,7, е помощью соеди)штельпых кабелей 7,- 17|т1 к разъемам 2,-2т соответствешо. На регистре 5 адреса устанавливается код, в соответствии с (оторым на выходе денлифратора 8 вырабатыяаегся сигпал, разреп1аюи|ий поступление импульса опроса из блока 7 управления в выбранпый блок памяти, например в блок 1 «-. При наличии вышеуказанной коммутац15и сигнал с дешифратора 8 через контрольные контакты разъемов 12,- 12лпИ 2,-2,„ поступает на все входы элементов 11 И блока 9 а1 ализа коммутации, связан)нле с разъемами При этом элемент 11 И не пропускает импульс опроса из блока 7 isa вход триггера 10, предиаз;1аченньи 1 для установки его в единичное состоя1 ие. llpeдвapliтeльнo триггер 10 был обиулеч сигналом с блока 7 управления. При наличии нулевого состояния триггера 10 блок 7 в режиме загноен вырабатывает сигналы опроса блоков 1 , 3, 4. В результате этого в накопителе 16 выбранного блока памяти 11 дополнительно к токам, протекаюН.1ИМ в режиме считывания, обеспечиваются адресные и разрядные токи записи, формируемые формирователями 4 и 3 и коммутируемые с 1юмош,ью элементов 12,-12„, 2,-2т и соединительных кабелей 17 t-17п,.

Рассмотрим варианты неправильной коммутации в режиме записи, например, с помощью соедипительных кабелей 17,-17™. К формирователям 3 и 4 будет подключен невыбран П)П блок памяти. В этом случае на входах блока 9 анализа коммутации, связанных с разъе.мами 2,-2п отсутствуют сигналы с выбранного выхода деп)ифратора 8. Вследствие этого через элемент 11 И пройдет импульс из блока 7 на вход триггера 10 и установит его в единичное состояние. При этом условии сигналы опроса блоков 1 ,- ij,,3, не будут сформированы блоком 7 и, таким образом, запись информации не произойдет. Аналогичным образом будет заблокировано выполнение записи информации при отсутствии хотя бы одной пары разъемов 12,--12т и 2 (---2т или при несоответствующей их стыковке. Например, разъем 12, с юмощью соединительного кабеля к разъему 2,л не обеспечивает стыковку контрольных контактов и соответственно наллчне на 2-х входах элемента 11 И сигналов, необходимых для запрета установки в единичное состояние триггера 10.

Использование предлагаемого устройства за счет введения контроля позволяет избежать разрушения информации при неправильной коммутации, что иовыа ает надежность хранения информации в запоминающем устройстве и эффективность использоВания устройства в составе различных шфровых систем.

Формула изобретения

. 1. Запоминающее устройство без разрушекня информации, содержащее блоки памяти, первые входы которых через конмутациопные элемепты соединены с выходами разрядр1ых н адресных формирователей токов записи, дешифратор выбора блоков памяти, вход которого соединен с первым выходом регистра адреса, дешифратор записи, вход которого соединен со вторым выходом ре-. гистра адреса, выходы дешифратора записи соединены с одними из входов гичресных формирователей токов записи, третий выход регистра адреса подключен ко вторым входам блоков памяти, блок управления, выход которого соединен с третьими входами блоков памяти, со входами разрядн1 Х формирователей токов записи и другими входа ми адресных формирователей токов записи, отличающееся тем, что, с целью повышения надежности устро 1ства путем защиты информации при ггеправилыюй коммутации, в устройство введен блок анализа коммутации, соединенный с блоком управления, входы блока анализа коммутации через коммутационные элементы соединены с четвертыми входами блоков памяти, выходы дешифратора выбора блоков памяти соединены с пятыми входами блоков памяти.

из элемента 11 и триггера, один из входов которого соединен с nbi.XT;o:Ni элемента i-1, входы з. Н и другой вход триггера соединены со иходамп блока анализа коммутации, выход тр ггера соединен с выходом блока а 1алнза коммутации.

Гг накопителя, другие входы накопителя соединены с nepFibiMH выходами коммутационных элементов, входы которых соединены с первыми li четвертыми входами блока намяти, вторые выходы кoм yтaциolHlыx элементов соединены с одним из входов элеме та И и с пятым входом блока памяти, выход элемента М соединен с первым входо.л деп1ифратора считывания, второй вход которого подключен ко второму входу блока памяти, другой вход элемента И сое3динен с третьим входом блока памятн, выход деш1 фратора считывания соединен со

формирователя токов счнвходом адресного тывания.

лсточннки информации, принятые во внимание прн экспертизе

Авторы

Даты

1980-07-23—Публикация

1978-05-04—Подача