(54) .ЛНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Устройство для аналого-цифрового преобразования | 1987 |

|

SU1425828A1 |

| Измеритель параметров комплексных сопротивлений | 1989 |

|

SU1751690A1 |

| Режекторный фильтр | 1986 |

|

SU1417180A2 |

| Система автоматического контроля параметров электронных схем | 1989 |

|

SU1700538A1 |

1

Изобретение относится к аналоговой вычислительной технике и .может быть использовано в устройствах автоматики, измерительной и вычислите-тьной техники.

Известно аналоговое запоминающее устройство, содержапдее накопите ть, блок выбора адреса, устройство записи, и выходное устройство, включающее в себя два интегрирующих усилителя, фильтр нижних частот, выходной усилитель и генератор тактовых импульсов, причем вход каждого интегрируюи его усилителя соединен с отдельной ВЕЯходиой шиной накопителя, выходы интегркруюпдих усилителей соединены с входами фильтра, выход фильтра соединен с входо.м выходного усилителя 1.

Данное устройство имеет ограниченные функциональные возможности и усложненную конструкцию в связи с наличием двух независимых выходных щин накопителя.

Известно также аналоговое запоминающее устройство, выполненное на накопителе из элементов памяти, построег;ных на трансфлюксорах, содержащее блок выбора адреса, устройство записи, блок поочередной выдачи адресов элементов памяти, по которым осуществляется сложение или вычитание, и выходное устройсгво. причем вход блока поочередной выдач : адресов соединен с выходо.м генератора тактовых и.мнульсов паpa,.4e, ОДНОМ) входу блока выбора адреса, другой Bxo.i подк.1Ючен параллельно вхо :iy уггравления указанного выше генератора :; лвляется в.чодо.м управления устройства, остальные ихо/глые иины являются шинами ггрие.ма адресов, а выходные щины соединены с блоком выбора адреса, выходное же ХСтоойство содержит схему стробирования, а)ильтр ниж1-;(х частот, усилитель и генераTQp ra.KTOBbix импульсов, один выход которо о iipHcoejinHCt к блоку выбора адреса, а л;;, .-ой к члй.-мо стробирования 2.

1 едостатк1.-м такого устройства является

новг.З.можиость реализации множительноделитсльных опорзц1 Й над считываемыми чнс iaMii.

Полью t;:...6peTeiuiH яв.тяется расширение и)нкциопальных возможностей устройства.

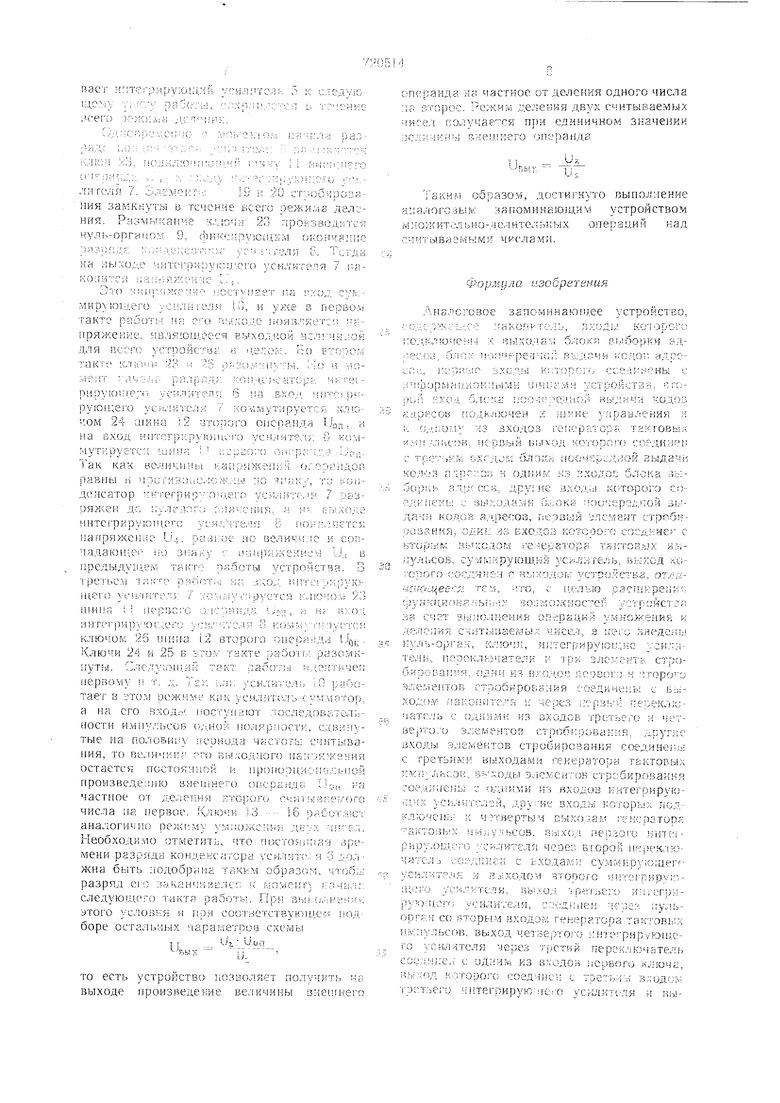

1Тостав,:11Ч;ная цель .хостигается те.м, что ц аналоговое з;;поминающее устройство, содержащее накопитель, входы которого кодключсны к выходам блока вырабокп

г. ,1

Рч

I,

к:.оче к ранда, вх елииен - :: ptii-iaa, Bi

СООТВО-Ч:Г;;

е;ч; и чет:

выходы Ч;

йена c;;Gj

BTOpOiO i-l .ЯЯК)111110 V

входами соотвргст;;

2 выбора адрес. бл;

кодов ядре;: OR. h;li;:

pi.pVKJiiisic vcii..:; чствер1Д)1Й, TiJCTHH. i op г ail 9. cvMMi-ijiviOij

:j: 0;f:j OU

о b;;,;i|v Hii ДрУГО ; iii:0::.la к(;к; ак;- 32, псрекдд

,;:jOiiiaTej5b ЗУ Зг,) 2; -- 36 р 13о:у;к::ут режима умнс жсния. На вход устройство поступают сигналы от импульсов счктыБй1ь.1Я и подготовки двух поочередно считываемых чисел, что с-существляется при помощи блока 3 поочередной выдачи кодов адресов, режим работы которого задается от гспс раторз 27 тактовых импульсов. В результате комм тации элементов 17 и 18 стрибировакия на входы интегрирующих усилигелей 5 и 6 поступают последовательности импульсов, причем в первглй такт работы Hiirei рирующий усилитать 5 интегрирует сигнал к э-ом ,iCiMe iV времени соединен через ,1.-.:емект 20 строОировгния с выxoдo 5 инте piipViOinero хсилнтеля 5. Момент окончания заркда фиксируется нуль-органом 9, а время : :iiv::;s одииаК-г- со феменем разряда кондс::сйто;К п у ,:; чте,1ей б и 7. Так как суммпpvK):i.uiH ус1 лите1ь 0 работает в этом режиме как усн,-гель разности двух сигналов, и его второй вход ссх-динен с выходом интегркр юшего зсилнтеля 8, то напряжение на его вь:ходе ге язменяетск. Далее процесс ряботь; периодичен. Ключи 13 - 16 испольот импульса считывания перво о числа, я интегрирую111.ий усилитель 6 интегрирует сигнал от импульса считывания второго числа и к моменту окончания интегрирования на конденсз оре интегрируюп,его уги.литена1 ряжеи1-1Я ib нь в/.ходе этого :л.п..

:,: п;.ОД i-s-; .; р-:Пу;о:иеГО ,КТ(;.-:, ;: ;iC.-кл омае ;:;-: ;-;гс ;. на ;ря;Кс ни;-; :,о;)т;;Т: опепянд;;; : ЗПряК:-;1 ; коток ; ..,

flpOTHRO)i;.OJK;i УЮ IKj.ifipHOCl Ь ГКТ О ;:-M-trinO к ВХОДНОлГ, ;;Я; рЯ--ЧОНИЮ 1 ЯТ;:;1;И| -;ЮИ еГ :

усилите;:/ с, vi ачинаетси разряд, лонденсатора э:-ого .еля.

Момент окопч ; ;; разряда ф;- ;-:сиру: сн нудь-орг-иол: 9. 0,,Л 0 :ременно с Зс;- Гь;ка::ме:ключа 22 открь:вг е1-ся элемент 19 - -роби рованик, ко;:.а,ч:сатор vuiTerpupviouio: о усилители 7 ;;;Ч::нае1 зйряжаться от - ; зд;;огс. напряжения Ui интегрирующего ye;--:,inrc:;;- 5

Zl,0 БЫХОД; О;Ч МаИрЯЖеНИЯ и,; ;ib: -:pii;3V;Oпдего Усилите Я 7.

как д,т под1Ч)товки ус1 лителеи по

тактам работы, так и для ликвидации дрейфа

НУЛЯ интегриру О1Цих усилителей 5 - 8.

Необходимо отметить, что постоянная

л;1 ;-;- Ч :кзяг :дг кончемсагопа мчвторолу такту оаботы. Элемент 20 с ровапик в течени первого такта г ря-пм;-:i-,i. я ci-n-:-.: па выхо/ч- нн-ге-; шеги ,.1;гге,1я и (JTCV гствует. Ьа1 ряжеь - е с Bi)Xv),.ui :нте:р;-;рулу1д2го уср лителй 7 ПС. jTioro cч iтьioae ;oгo

сключате.чь 28 рсжилов

3;. переключатель 29

к л ЧЬ 30 замкнут на

такте счит1 вани ::;:яь аяется cvii игл. язляю иийся выходным длк устройства в целол:. Во втором работы в -уножения и;(тогр1:-руО:кий усыите ь Ь интегрирует сигиал от импульса подготовки .то числа, ИНТ егрмпуюш.его усилитель о и ч, 19 стробк|х;п2:;--;; совместно с кл:очо1; 22 сохраняют свой режи, илботы, к в .-омент начала paspHzia конденсатора ч:илмтеля 6 начи1:лртся разряд заиоминаюи1;Гу кондеисаторв vcujiKTS.iK 7, напряжение на когором падке: до -.у.:к, т;;к как ему заряд, p43;hin ю Ft.,Ho Г:рстччочоло;хный по 3i-i;: v. V),н- -,Гемен о с г а:оЧ:.л; оззОЯДа ;;,)i /ifiiC:: rOiJd J-il-iTerpHtU -;:i.Jiтеля 7 начинается заряд конденсйторы инте-рируюлл -с усилители S, ихо,- хотс;ро:о

ПЭСТ iiTPrp;4pv:oi;j;-;ii /{И.)};ТСЛ f-. , К С.ТеД/10

- л-ч-С p:j ;Cii-Ji; с ;оо ч;гл О:; .;;... я Ba:v

лигсдя ;. с/лемекг:;: 19 я 20 ст обчрозяния замкнуты в течение всего )ежи;ла деле ния. Размьгканче ключи 23 производится ну.ль-оргямо:л 9, Фикеарую;),-;, окончапко ;-- 1 -.- ::,:;т;:::л;;гпг-:;;- ур- г;.гедя П. Тсгда на ныхо.,е чнтсч рипукисгс си.;ктеля 7 (г; o;iHTC:i :;й:;;;я ::енчс .--;.

Это м пп-чх-; ::;;-;- i;ccTVi 2eT lia сход сурлмир)ющего усмлыгелм (, и уже s пеоБО) такте раоотьг на г-л;;оде 1|()яа,-;кет;п :п;гфяжепие, являющееся выходкой всл;-шсой для псего устройс:-иа в Д2;:ок. по столом такте Kcrhv.H-; и /5 р соу-пугы. с;о в УЮруюи;его уси.лнтели : ; ол;мутаруетсй кл;ачом 24 ашна 2 второго О 1ера1)да на 1зход Hicrerocnvioiiicro yeiijiHre.u: 8 К(см

S ак как вели1-д1Ны кааонжеис;: ос, равны 11 лосгязоиолс.жлы ло -змагл/, т;.) )деисатор ;нтегрир-; он.|,есс) уе л;5тел:- 7 лазряже - дс :;улслп т.; заа-лаик, а, н- .с KHTcrpHpyioiiiecc леи.Слтц д В :10гЛ;дпртс ; напряженнее Lc;. paijcoe по величине и coiv надаюн ес j;o знаку с панр;ихениел IJ,; в предь ду11лем паботы устройства. 3 -ретьем так-г;-. ряги-ут,-: на .злод. iHcrc; р: руюHi,eio уси.пите.-л. / л( i pjyeTcn i-ЛОчО:,; ИЗ тина М н(р;зсго )лс;аи;:,а .JT-T, а н; вход интегрн15 О1 лего :(:.-, л -чомсл гн 1У;- л: ключом 25 Н1ина 12 аторосо онер 1:;да Ujij;. Ключи 24 н 25 в тахте paSoTfc разол/нснутг. Слел,у;он1ий такт pacoihi идент чег; первому н т, д. Т.; i.;.a; ;силитедь л) lyao;:тае в етом РСЖИУС как уси;иг1ч тьл .млиггор, а на есо зход;Л HOCTysiaiOT лоследоватсл;;ноети нмнульеов од.ной 1К)ляраое и, СД.ВИНУтые на половнш аеииода частоть; (считывания, то величяис (лт) Быход;- осо наадк кения остается ностоянной и роноонил ад л ой нроизведеамю внешнего огкранда 1);,, на частное от деления CTOI;OCO счат,:в,аег/т)со числа на первое. Ключи ;3 16 работают аналогично рен;пм хсусктжонии . лие:,. Необходимо отметить, что чоетон|Н а: i peмени разряда конденсатора (:я G должна быть лодобрана таким образом. чтоб;л разряд его саканчква.чсг: к моменг (ClHa.ic следующего такта работе;. При В 1 ;Л; сне:-ал: этого сло; ня И НОИ соотнетствун н.сЛ подборе остальных параметров схемы S..4 Uon

операнда на частное от деления одного числа :;R згсрое. Режим де ;екия ДВУХ считываемых чисе.л 1;;о ;учае ся пт)и единичном значении ; слкчквь1 .кего операнда

ТакйИ образом, доетиснуто выполнение аналосодыг : нйпомикающим устройством м:южительно-де.штельиых операций над считываемыми чр сдамн.

сгл., неп:гл с дход,;Д которого еоелка ны i;

ООН сход бл( iJOOTC: e,:.UiOa выдачи кодос. асоссон подключен л |и-:не хсфайления н к о,-лнол лз входов renepaiopa тактовых ;cvoK/.;ihc; B. иервый выход которОТ) е; диае1;

ко.с(;в адресов н одним из ходос ньл ооркс адресов, другие вхо.:о ;(;то-рого еос, с зыс.о.а,али б.-хтка ноонерес,ной .;1й-:м кодс;в а.чресов, rieoauft олсмеит стробирозания, мз входов котсоого еосдннео с втирь К вы;;о;лО1з ге--ерагоря тантов лх ис,ayjit coB, ey;vjM;-ipyioui;- ft усйд;-сге., выход ко:Орого .-осд-1;:е:1 с устро.чстБа, о сл1-1.К ЩеС:: :: -Гл, НТО, С ЦеЛЫО paCiiiHpeUJ:::;

за счет вьнюлнениН оп-срацин умножения и .телолйл счкт;:. чнсел. в него внедеи н нулъ-ор1-ан, ключн, и:;тегрир 1оил;е cctrca1-ели.. г;ереклв}натедк v ipn зделента строзлемептов стробярования с оединены с В; :ходоу аанопптегя н неоез :дл;ввн неоеключателв с ;дннми кз входов третьего и четверто.о элеме - тов стробнровання, двугне ВХОДВ1 элементов стробированкя соединен с третьими выходами генератора тактовв1х .;iBcoB, )ды элементов стробкрования coe.THHejiB с о.д|;ил;и из входов интегоируюнрчх ЗСилителей, .роугие входьг :оторь л jiocклочень: н чгтвертвч ввгхо.сам ген(;паторй ляктовво; н„1::у . Вл;Х(л1 первого интем риру.овлгсо ;-с %титедд чеоез второй нереклюHaTeJij вОе..-Д;н;;::.; Q ГХО.талЛ СуМНИру О;цеГ

усилнтсл;; и в л ходом второго ннтегриргчоUeiO усс-1лвтелк, ввС:о;. ингег);-;орган со BTopBiM входом генератора тактоввв-; Нунг сльсов. вь1ход четве;5тог-о ннте -рипуюн;(:iX) усилителя через третий нерекг;ючйтел; coy;j.:ii-e.i с одним КЗ входов неувого ключа. -нл-н)д которого соедн ;ен с згодоь: тостзего Н1 те1д ируюн его усгшкт;-дя н вы

Авторы

Даты

1980-03-05—Публикация

1977-05-12—Подача