(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТТОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1977 |

|

SU723686A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU750569A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU866577A2 |

| Аналоговое запоминающее устройство | 1980 |

|

SU945903A1 |

| Аналоговое запоминающее устройство | 1977 |

|

SU720514A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| УСТРОЙСТВО СОПРОВОЖДЕНИЯ ТРАЕКТОРИИ ДВИЖУЩИХСЯ ОБЪЕКТОВ | 1994 |

|

RU2079150C1 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ ИЗОБРАЖЕНИЙ | 1990 |

|

RU2006942C1 |

1

Изобретение относится к области аналоговой вычислительной техники н может найти применение в устройствах автоматики, измерительной и вычислительной техники.

Известны аналоговые запоминающие устройства, построенные на трансфлюксорах, прошитые обмотками записи, считывания и выходными обмотками 1.

В Известном устройстве осуществляется операция сложения аналотовых сигналов при одновременном считывании информации с трансфлюксоров, расположенных на одной выходной обмотке, при этом необходимо осуществлять одновременное считывание информации с нескольких элементов памяти на трансфлюксорах При этом сшнал на выходной обмотке будет определяться как сумма сигналов, считываемых с выбираемых одновременно элементов памяти. Однако невозможно осуществить суммирование информации, считываемой одновременно с двух элементов памяти, расположенных нэ разных координатных шинах как по X координате, так и по У, поскольку при этом считывается информация не с двух, а с четырех элементов

памяти одаовременно. Например, при о.цновременном считывании информации с элементов памяти, расположенных в пересечении первой по X и первой по У координат и вторым по X и по У координат будет считыг аться информация с элементов, расположенных в пересечении первой по X и второй по У координат, а также второй по X и первой по У координат.

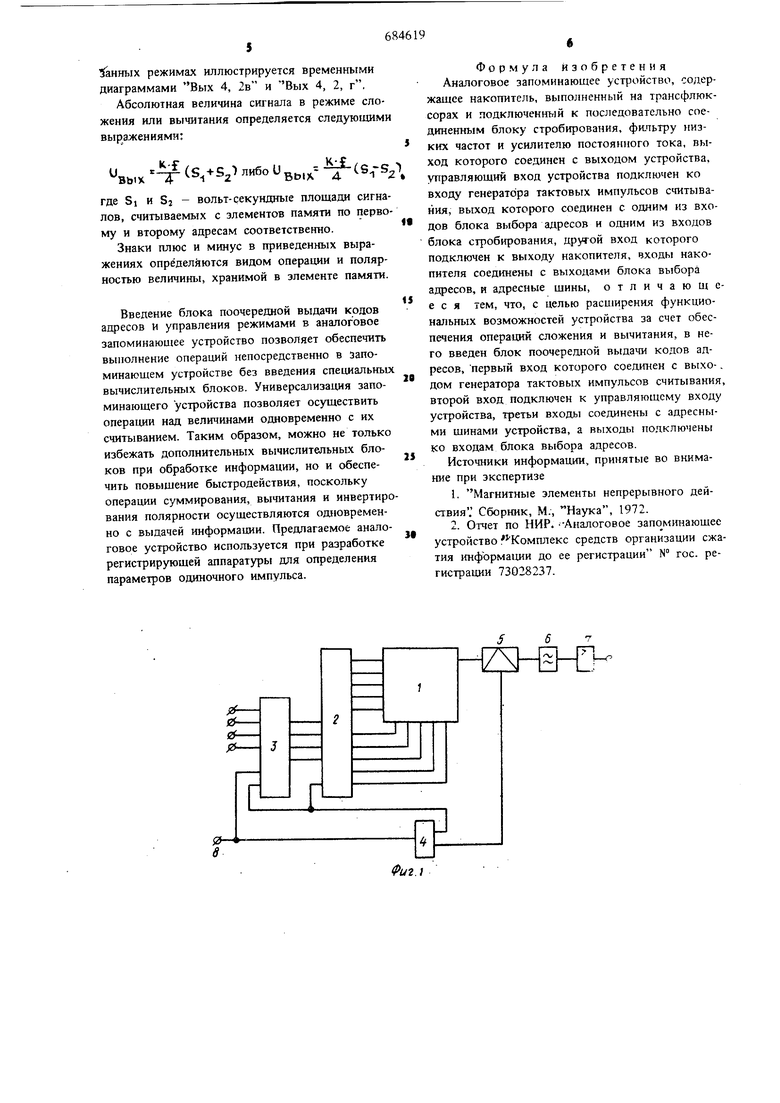

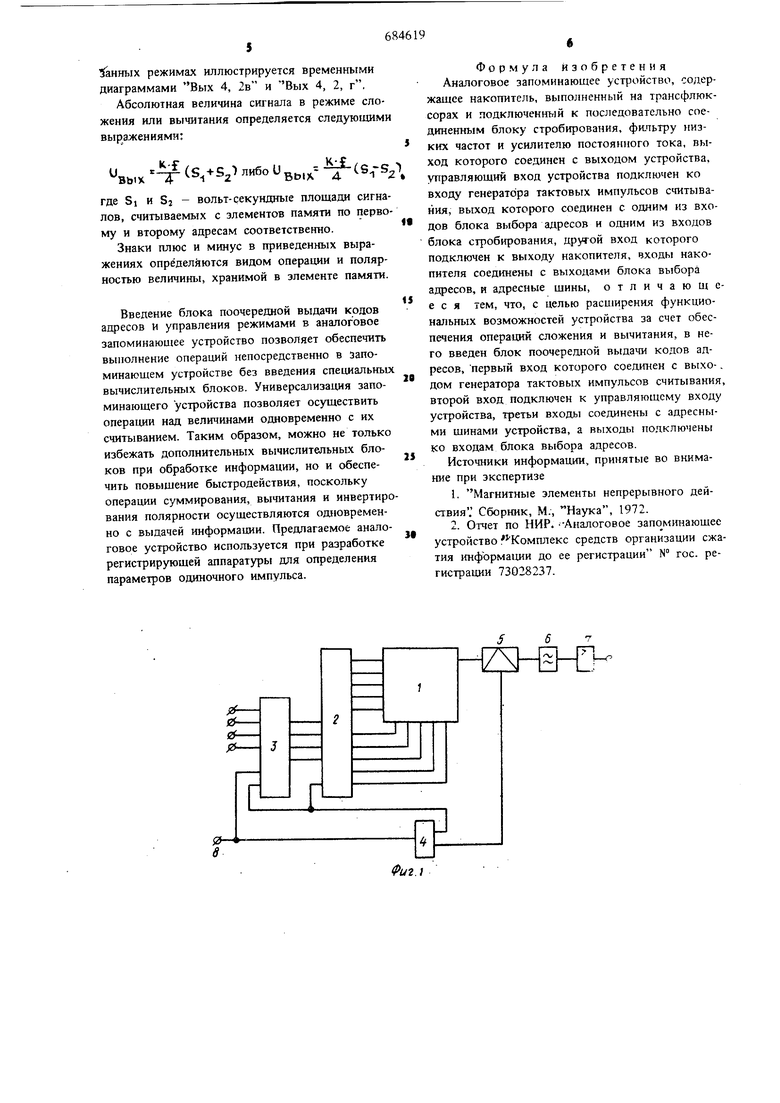

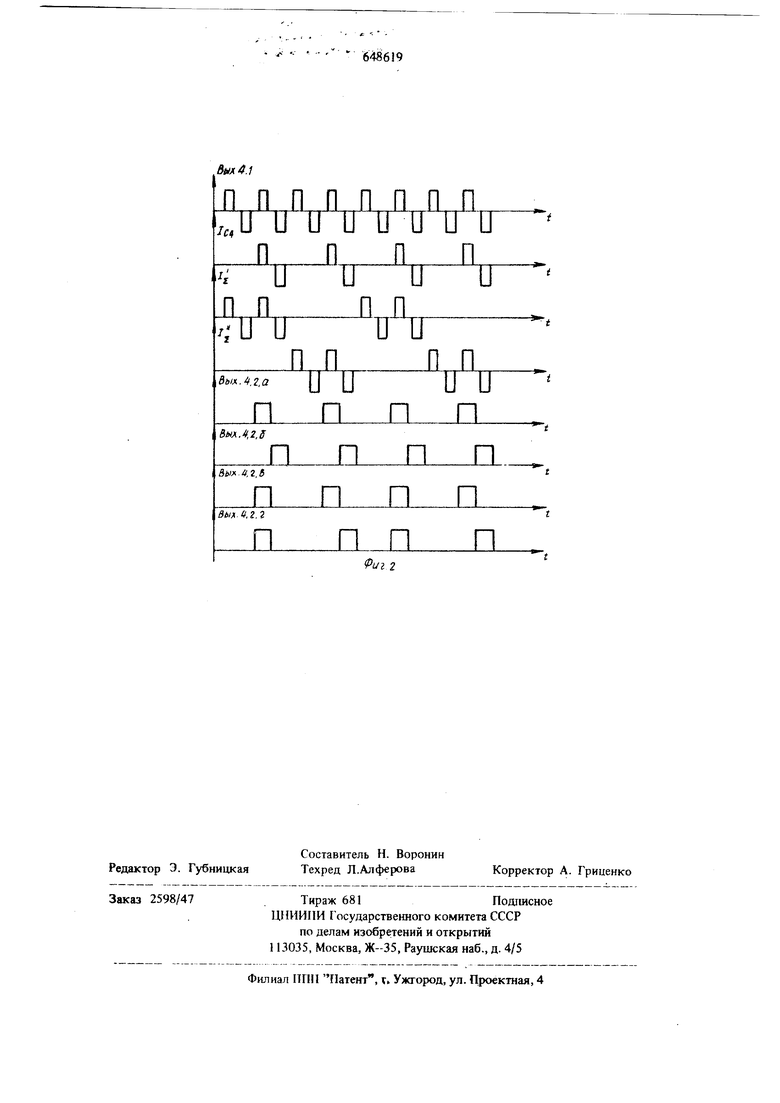

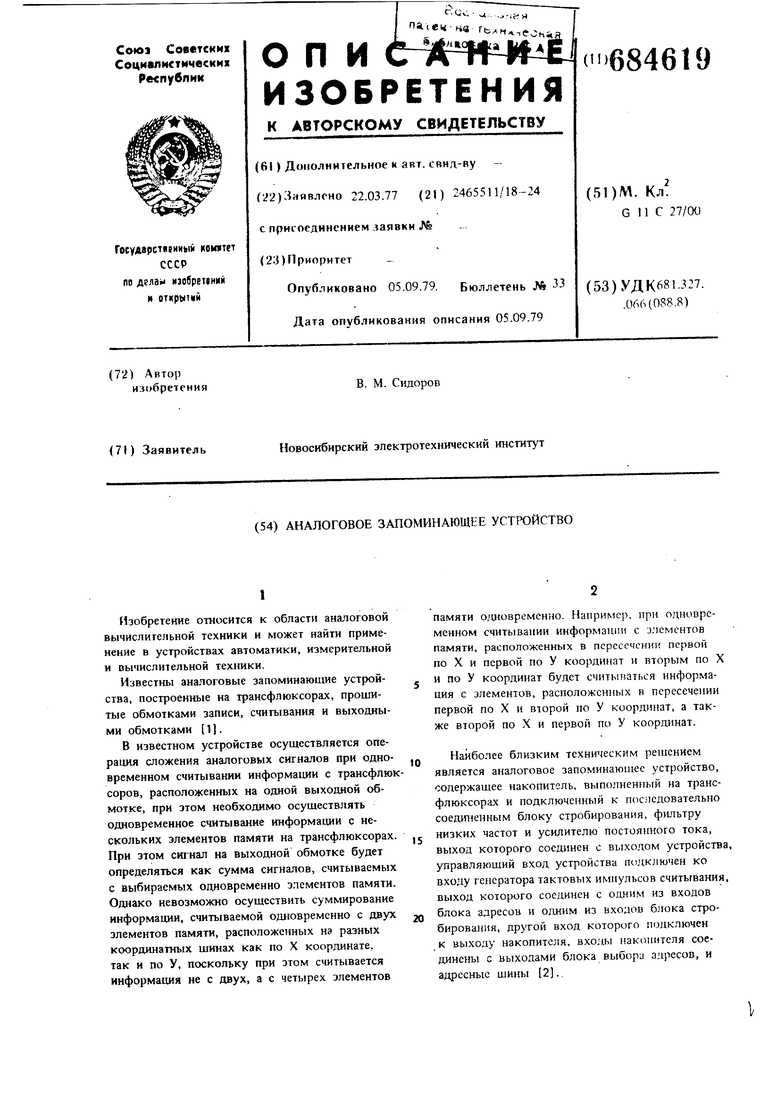

Наиболее близким техническим решением является аналоговое запоминающее устройство, содержащее накопитель, выпо тненный на трансфлюксорах и подключенный к последовательно соединенным блоку стробирования, фильтру низких частот и усилителю постоянного тока, выход которого соединен с Bbixo.rjoM устройства, управляющий вход устройства подключен ко входу генератора тактовых импульсов считывания, выход которого соединен с одним из входов блока адресов и одним из входов блока стробирования, другой вход которого подключен к выходу накопителя, входы накопителя соединены с выходами блока выбори адресов, и адресные щины 2. К недостаткам известного устройства относятся огран гченные функциональные возможнос ти, то есть устройство может выполнять только операцию запоминания информаили. Целью изобретения является расширение функциональньЕХ возможностей устройства, за счет обеспечения операций сложения и вычитания. Поставленная цель достигается тем, что в него введен блок поочередной выдачи кодов адресов, первый вход которого соединен с выходом генератора тактовых импульсов считывания второй вход подключен к управляющему входу устройства, третьи входы соединены с адресными шинами устройства, а выходы подклю чены ко входам блока выбора адресов. На фиг. 1 изображена его функциональная схема, а на фиг. 2 - временная диаграмма его работы. Аналоговое запоминающее устройство содержит накопитель 1, выполненный на трансфлюксорах; блок выбора адреса 2, выходные шины которого являются координатными шинами выборки накопителя 1; блок 3 поочередной выдачи кодов адресов, в котором осуществляется сложение и вычитание, генератор 4 тактовых импульсов считывания, выходы которого присоединены к блоку выбора адреса 2, блоку 3 поочередной выдачи кодов адресов и бло ку стробирования 5, который в свою очередь соединен с одной стороны с выходной шиной накопителя, с другой через фильтр нижних частот 6 с усилителем постоянного тока 7. Кроме того, устройство имеет управляющий вход 8, который является входом блока 3 поочередной выдачи кодов адресов и генератора 4 тактовых импульсов считывания. Выходные шины блока 3 соединены с блоком выбора адреса 2. Запоминающее устройство при считывании работает в следующих четырех режимах: а)режим считывания информации; б)режим считывания с инверсией полярности выходного сигнала элемента памяти; в)сложение сигналов, считываемых с неско ких элементов памяти; г)вычитание сигналов. При считывании информаш1и адрес считываемого числа запоминается в блоке 3 поочередной выдачи кодов адресов и блок выбора адре са 2 возбуждает координатные шины накопителя 1, соответствующие данному .адресу. Генера тор тактовых импульсов считывания 4 постоян но вырабатывает по своему первому выходу импульсы, как показано на временной диаграм ме Вых. 4, 1, (фиг. 2). При зтом блок выбора адреса вырабатывает на координатных ши нах импульсы тока таким образом, что на выбранный элемент памяти накопителя будут действовать импульсы тока переменной полярности, последовательность которых изображена на сре.менной диаграмме Лсч зтом на выходаой обмотке вырабатываются импульсы напряжения, вольт-секущшая плошадь которых пропорциональна информации, записан1гой в элементы памяти. При обычном считывании генератор тактовых импульсов считывания по своему второму выходу вырабатывает импульсы строба таким образом, что стробируются только импульсы напряжения одной полярности, такой, которая соответствует полярности считываемого сигнала. Эта последовательность, соответствующая режиму считывания изображена на временной диаграмме Вых. 4, 2, а. При считывании с инверсией полярности стробируюшие имгульсы соответствуют импульсам напряжения полярностью противоположной полярности считываемого сигнала, как это показано на временной диаграмме Вых 4, 2, б. В режиме считывания как прямого, так и с инверсией выходного сигнала, абсолютная величина считываемого сигнала УВЫХ определяется следующим выражением: -вых -2 / где S - вольт-секундная площадь сигнала, считываемого с элемента памяти, f - частота следования импульсов на первом выходе генератора тактовых импульсов, а К - коэффициент усилителя постоянного тока. В режиме вьшолнения операш{й сложения и вычитания в блоке 3 поочередной кодов выдачи адресов запоминаются адреса элементов, по которым осушествляется операции, и адреса выдаются на блок выбора адреса 2 таким образом, что за время очередного возбуждения координатных шин выбранных элементов через них проходят не менее двух пар импульсов считывания, как зто показано на временных ( т ti диаграммах jj и dy, при выполнении операции над двумя числами. Такая последовательность импульсов считывания необходима в накопителе на основе трансфлюксорной матрицы с геометрическим совпадением токов, поскольку первая пара импульсов тока осуществляет подготовку всех злементов по выбранным адресам, а только вторая обеспечивает выходной сигнал, соответствующий е/1инственному выбранному элементу памяти. Генератор 4 тактовых импульсов считывания вырабатывает в режиме сложения и вычитания по всему второму выходу импульсы строба выходных сигналов соответствующей полярности только по вторым парам импульсов, следующих через выбранные элементы. Режим вычитания отличается от ре.жима сложения тем, какой полярности импульс стробируется при обращении к вычитаемому. Стробирование в укаДанных режимах иллюстрируется временными диаграммами Вых 4, 2в и Вых 4, 2, г. Абсолютная величина сигнала в режиме сложения или вычитания определяется следующими вырэл ениями: V.X V 6° БЬ,х S-T V где Si и Sj - вольт-секундные площади сигна лов, считываемых с элементов памяти по перво му и второму адресам соответственно. Знаки плюс и минус в приведенных выражениях определяются видом операции и полярностью величины, хранимой в элементе памяти. Введение блока поочередной выдачи кодов адресов и управления режимами в аналоговое запоминающее устройство позволяет обеспечить выполнение операций непосредственно в запоминающем устройстве без введения специальных вычислительных блоков. Универсализация запоминающего устройства позволяет осуществить операции над величинами одновременно с их считыванием. Таким образом, можно не только избежать дополнительных вычислительнььх блоков при обработке информации, но и обеспечить повыщение быстродействия, поскольку операции суммирования, вычитания и инвертиро вания полярности осуществляются одновременно с выдачей информации. Предлагаемое аналоговое устройство используется при разработке регистрирующей аппаратуры для определения параметров одиночного импульса. Фор.мула изобретения Аналоговое запоминающее устройство, содержащее накопитель, выполненный на трансфлюксорах н подключенный к последовательно соединенным блоку стробирования, фильтру низких частот и усилителю постоянного тока, выход которого соединен с выходом устройства, управляющий вход устройства подключен ко входу генератора тактовых импульсов считывания, выход которого соединен с одним из входов блока выбора адресов и одним из входов блока стробирования, другой вход которого подключен к выходу накопителя, входы накопителя соединены с выходами блока выбора адресов, и адресные щины, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения операций сложения и вычитания, в него введен блок поочередной выдачи кодов адресов, первый вход которого соединен с выхо-, дом генератора тактовых импульсов считывания, второй вход подключен к управляющему входу устройства, третьи входы соединены с адресными щинами устройства, а выходы подключены ко входам блока выбора адресов. Источники информации, принятые во внимание при экспертизе 1. Магнитные элементы непрерывного действия. Сборник, М., Наука, 1972. 2.Отчет по НИР. --Аналоговое запо минающее устройство Комплекс средств организации сжатия информации до ее регистрации № гос. регистрации 73028237.

-

Авторы

Даты

1979-09-05—Публикация

1977-03-22—Подача