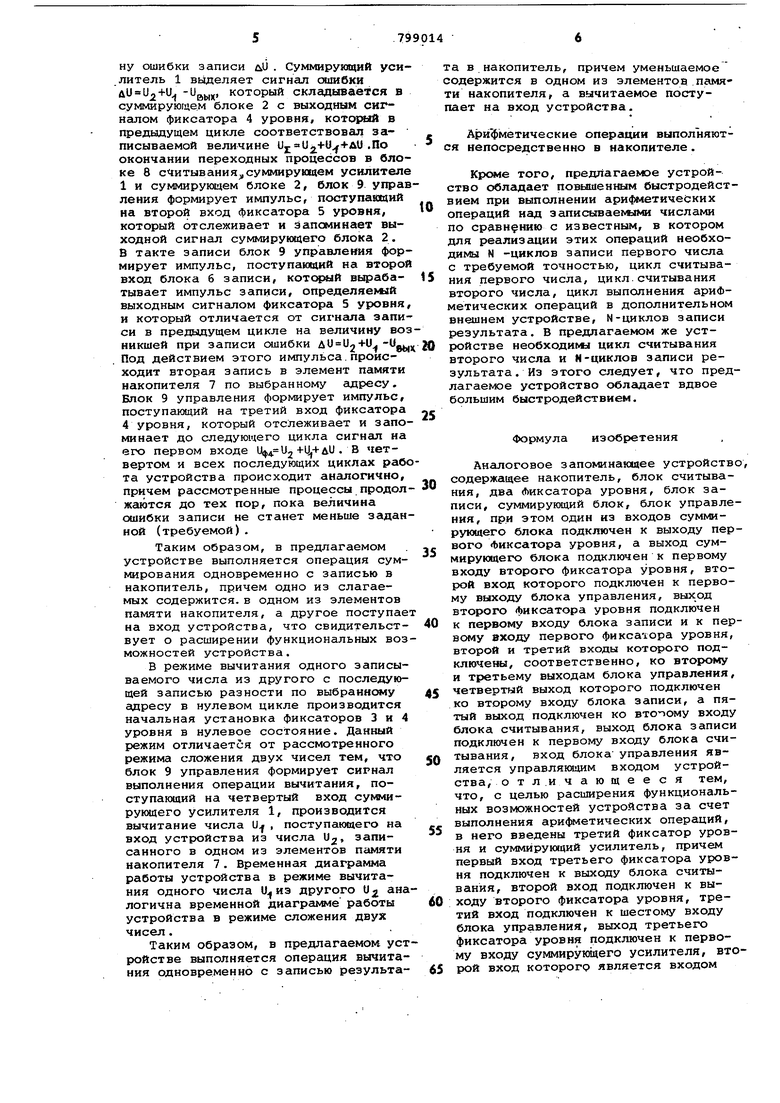

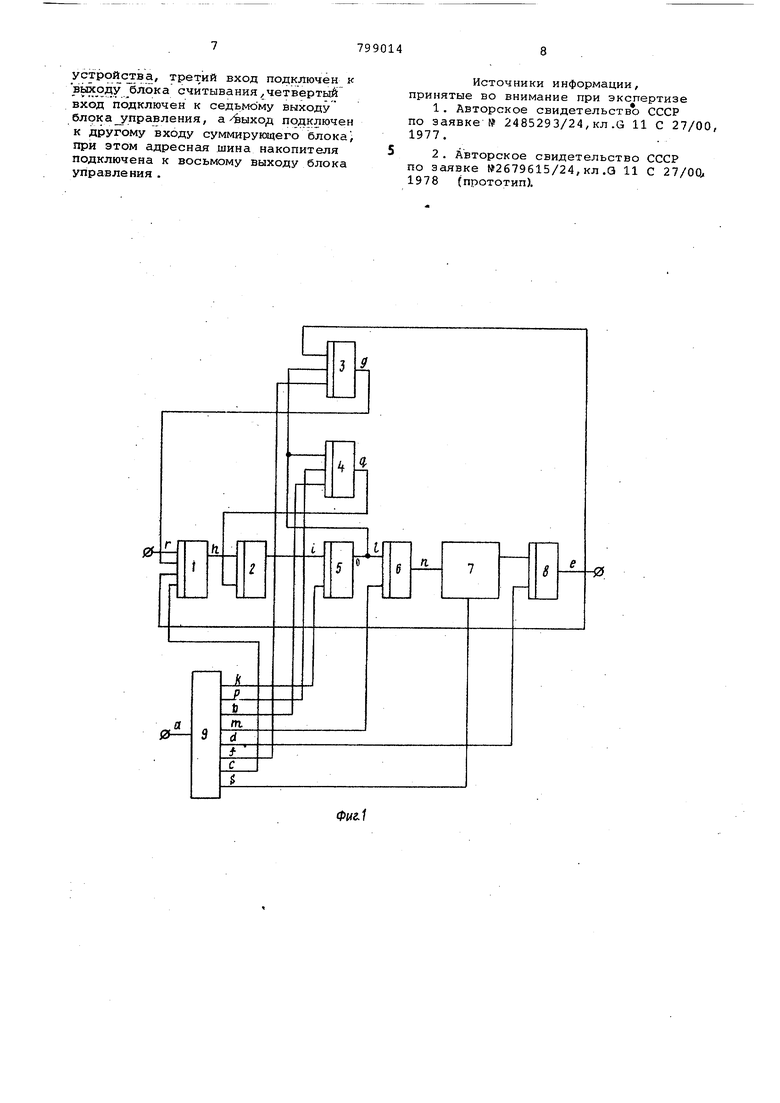

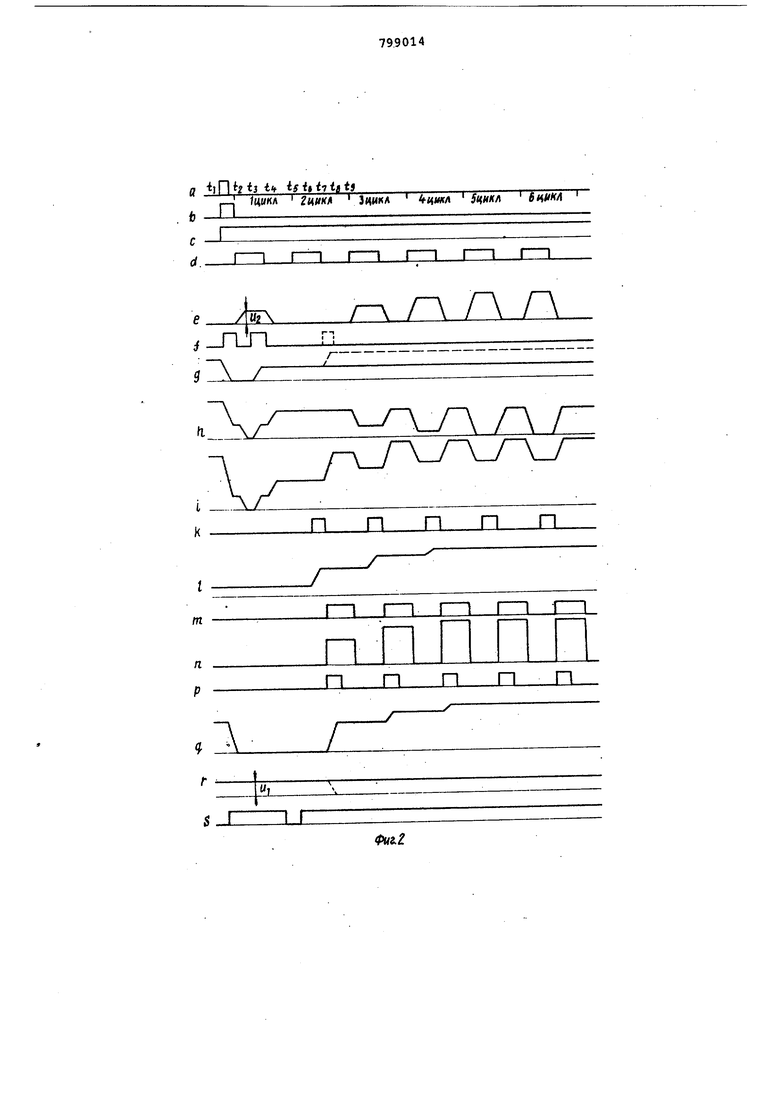

Изобретение относится к аналогово вычислительной технике и может быть использовано в устройствах автоматики , измерительной и вычислительной технике. Известно аналоговое запоминаю1т,ее устройство, содержащее накопитель, блок поочередной выдачи кодов адресов, генератор тактовых импульсов, блок выборки адресов, два блока стро бирования, интегрирующие усилители, дифференциальный усилитель 1JОднако устройство может быть реализовано только на аналоговых элементах памяти с неразрушаницим считыванием инЛормации. Наиболее близким техническим решением к предлагаемому является аналоговое запоминаюгдее устройство, содержащее вычитатацие и суммирующие устройства, два Фиксатора уровня, устройство записи, запоминагадий элемент с разрушающим считыванием инфор мации, устройство считывания, устройство управления 2. Однако устройство имеет ограничен ные функциональные возможности, так как не позволяет выполнять арифметические операции над записываегллми ве личинами непосредственно в накопител Цель изобретения - расширение функциональных возможностей устройства за счет выполнения арифметических операций . Поставленная цель достигается тем, что в известное устройство, содержащее накопитель, блок считывания, два фиксатора уровня, блок записи, суммирующий блок, блок управления, при этом один из входов сумкмрующего блока подключен к выходу первого фиксатора уровня, а выход суммирующего блока подключен к первому входу второго фиксатора уровня, второй вход которого подключен к первому выходу блока управления, выход второго фиксатора уровня подключен к первому входу блока записи и к первому входу первого фиксатора уровня, второй и третий входы которого подключены, соответственно, ко второму и третьему выходам блока управления, четвертый выход которого подключён ко второму входу блока записи, а пятый выход подключен ко второму входу блока считывания, выход блока записи подключен к первому входу накопителя, выход которого подключен к первому входу блока считывания, вход блока управления является управляющим входом устройства, введены третий фиксатор уровня и суммирующий усилитель причем первый вход третьего фиксатора уровня подключен i выходу блока считывания, второй вход подключен к вьаходу второго фиксатора уровня, тре тий вход подключен к шестому выходу блока управления, выход третьего фик сатора уровня подключен к первому входу суммирующего усилителя, второй вхол которого является входом устройства, третий вход подключен к выходу блока считывания, четвертый вхо подключен к седьмому выходу блока уп равления, а выход подключен к другому входу суммирующего блока, при это адресная шина накопителя подключена к восьмому выходу блока управления. На фиг. 1 приведена схема устройства; на фиг. 2,3- временные диаграммЫг поясняющие работу устройства в режимах сложения двух записываемых чисел с последующей записью суммы в накопитель, соответственно. Устройство содержит суммирукяций усилитель 1, суммирующий блок 2, фик саторы 3, 4 и 5 уровняублок б записи накопитель 7, блок 8 считывания, бло 9 управления. Устройство работает следующим образом. Процесс работы устройства во все режимах состоит из нескольких временных интервалов, называемых циклами, каждый из которых состоит из двух тактов - разрушающего считывани и записи. В режиме записи одного чис ла в нулевом цикле производится начальная установка фиксаторов 3 и 4 уровня в нулевое состояние, причем фиксатор 3 уровня в течение всего процесса записи не изменяет своего состояния. В режиме сложения двух записываемых чисел с последующей записью суммы в нулевом цикле производится начальная установка Фиксаторов 3 и 4 уровня в нулевое состояние. В первом цикле в момент времени t блок 9 управления формирует импульс, поступёиощий на блок 8 считывания и одновременно Обеспечивает выбор адреса второго числа. При этом на выходе блока считывания формируется напряже ние U2.1 соответствующее величине счи танного числа. В момент времени t 3 блок управления формирует импульс, поступающий на фиксатор 3 уровня, ко торый в интервале отслеживает и запоминает до конца процесса работы величину Uj. При необходимости ,считанная по второму адресу информация может быть восстановлена, причем процесс восстановления аналогичен процессу записи одного числа. Во втором цикле в.момент времени tj блок управления формирует импульс, поступающий на блок считывания, и одновременно обеспечивает выбор адреса того элемента памяти накопителя, в который производится запись сумкы двух чисел. Элемент памяти находится в,нулевом состоянии. На первый вход суммирующего усилителя 1 поступает первое слагаемое U, а на второй вход с выхода фиксатора 3 уровня - второе слагаемое, на четвертый вход поступает сигнал Uj. управления, обеспечивающий выполнениеопераций сложения, (в дальнейшем режим записи суммы двух чисел аналогичен режиму записи одного числа). Во втором цикле в интервале на выходе блока 8 считывания формируется выхгцное напряжение UnyjO. Cy «flиpyющий усилитель 1 выделяет сигнал ошибки, равный разности суммы двух величин U и выходной вели-, чины . Суммирукяций блок 2 выполняет операцию сложения сигнала ошибки и выходного сигнала Фиксатора 4 уровня, формируя сигнал U.j,U2+ U , поступающий на первый вход фиксатора 5 уровня . По окончании переходных процессов в блоке 8 считывания, суммирующем усилителе 1 и суммирующем блоке 2, соответствующему моменту времени 1,блок 9 управления вырабатывает импульс, поступающий на второй . вход фиксатора 5 уровня, который в интервале времени отслеживает и с момента t- запоминает значение сигнала на первом входе (}(f(i (i2 8такте записи блок 9 управления формирует импульс, поступающий на второй вход блока 6 записи, который вырабатывает импульс записи, пропорциональный (обычно равный по амплитуде) сигналу на его первом входе, и производится первая запись в выбранный элемент памяти накопителя 7. Одновременно с этим в интервале t-j-tg блок 9управления Формирует импульс, поступающий на третий вход фиксатора 4 уровня, который в интервале отслеживает и с момента времени tg запоминает до следующего цикла сигнал на его первом входе, равный 4i,, Если время существования первого слагаемого Щ на первом входе суммирующего усилителя 1 ограничено, то предусмотрена возможность хранения суммы двух чисел 1) и на время ее записи в фиксаторе 3 уровня . Для этого в момент времени -t блок 9 управления формирует импульс, поступающий на третий вход фиксатора 3 уровня, который в интервале отслеживает и с момента времени tg. запоминает Ui+ и/( до конца процесса записи. В третьем цикле, в такте считывания блок 9 управления формирует имг1ульс, поступающий на блок 8 считывания, и производится считывание с элемента памяти накопителя 7 который при этом устанавливается в нулевое состояние. Блок 8 считывания формирует выходной сигнал, который отличается от запи- санного в предыдущем цикле на величину ошибки записи . Сумкмрующий уси.литель 1 ввделяет сигнал ошибки который складывается в суммируюгдем блоке 2 с выходным сигналом фиксатора 4 уровня, кото1Я:1й в предыдущем цикле соответствовал записываемой величине .По окончании переходных процессов в блоке 8 считывания,суммирующем усилителе 1 и суммирующем блоке 2, блок 9 управления формирует импульс, поступающий на второй вход фиксатора 5 уровня, который отслеживает и запоминает выходной сигнал суммирунхцего блока 2. В такте записи блок 9 управления формирует импульс, поступающий на второй вход блока 6 записи, вырабатывает импульс записи, опраделяекый выходным сигналом фиксатора 5 уровня, и который отличается от сигнаша записи в предыдущем цикле на величину возникшей при записи ошибки AU . Под действием этого импульса.происходит вторая запись в элемент памяти накопителя 7 по выбранному гщресу. Блок 9 управления формирует импульс.

поступающий на третий вход фиксатора

4 уровня, который отслеживает и запоминает до следующего цикла сигнал на его первом входе . ,+uU. В четвертом и всех последующих циклах рабта устройства происходит аналогично, причем рассмотренные процессы продол жаются до тех пор, пока величина ошибки записи не станет меньше заданной (требуемой).

Таким образом, в предлагаемом . устройстве выполняется операция суммирования одновременно с записью в накопитель, причем одно из слагаемых содержится.в одном из элементов памяти накопителя, а другое поступае на вход устройства, что свидительствует о расширении функциональных возможностей устройства.

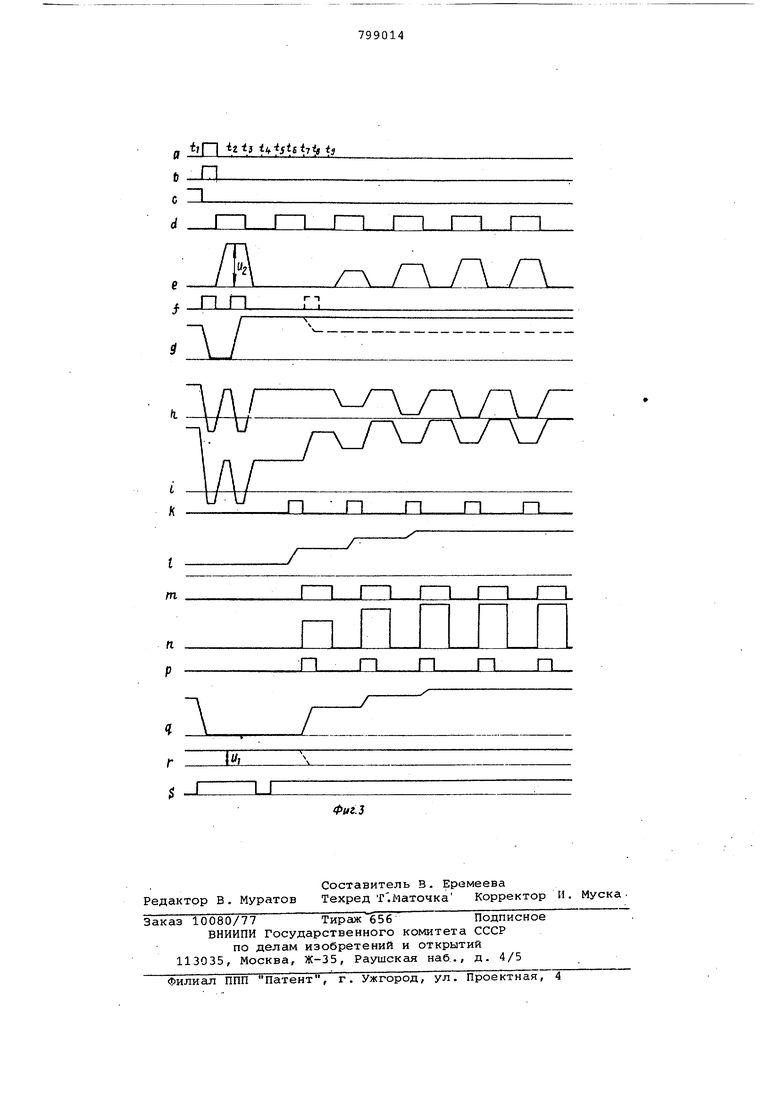

В режиме вычитания одного записываемого числа из другого с последующей записью разности по выбранному адресу в нулевом цикле производится начальная установка фиксаторов 3 и 4 уровня в нулевое состояние. Данный режим отличается от рассмотренного режима сложения двух чисел тем, что блок 9 управления формирует сигнал выполнения операции вычитания, поступающий на четвертый вход суммирующего усилителя 1, производится вычитание числа U, поступающего на вход устройства из числа U, записанного в одном из элементов памяти накопителя 7. Временная диаграмма работы устройства в режиме вычитания одного числа другого U аналогична временной диагра1 е работы устройства в режиме сложения двух чисел.

Таким образом, в предлагаемом устройстве выполняется операция вычитания одновременно с записью результата в накопитель, причем уменьшаемое содержится в одном из элементов памяти накопителя, а вычитаемое поступает на вход устройства.

Арифметические операции выполняются непосредственно в накопителе.

Кроме того, предлагаемое устройство облгщает повышенным быстродействием при выполнении арифметических операций над записываемыми числами по сравнению с известным, в котором для реализации этих операций необходимы N -циклов записи первого числа с требуемой точностью, цикл считывания первого числа, цикл.считывания второго числа, цикл выполнения арифметических операций в дополнительном внешнем устройстве, N-циклов записи результата. В предлагаемом же устройстве необходим: цикл считывания второго числа и N-циклов записи результата. Из этого следует, что предлагаемое устройство облащает вдвое большим быстродействием.

Формула изобретения

Аналоговое запоминающее устройств содержащее накопитель, блок считывания, два Фиксатора уровня, блок записи, суммирующий блок, блок управления, при этом один из входов суммирующего блока подключен к выходу первого Фиксатора уровня, а выход суммирующего блока подключен к первому входу второго фиксатора уровня, второй вход которого подключен к первому выходу блока управления, выход второго фиксатора уровня подключен к первому входу блока записи и к первому входу первого фиксагора уровня, второй и третий входы которого подключены, соответственно, ко второму и третьему выходам блока управления, четвертый выход которого подключен ко второму входу блока записи, а пятый выход подключен ко втопому входу блока считывания, выход блока записи подключен к первому входу блока считывания, вход блока управления является управляющим входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет выполнения арифметических операций, в него введены третий фиксатор уровня и суммирующий усилитель, причем первый вход третьего фиксатора уровня подключен к выходу блока считывания, второй вход подключен к выходу второго фиксатора уровня, третий вход подключен к шестому входу блока управления, выход третьего фиксатора уровня подключен к первому входу суммирующего усилителя, второй вход которогр является входом устройства, третий вход подключен к вьйоду блока считывания, четвертый вход подключен к седьмому выходу блока управления, а IBHXO I подключен к другому входу суммирующего блокаj при этом адресная шина накопителя подключена к восьмому выходу блока управления . 8 Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР по заявке 2485293/24,кл.G 11 С 27/00, 1977.. 2 . Авторское свидетельство СССР по заявке №2679615/24, кл .3 11 С 27/00. 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU951403A2 |

| Аналоговое запоминающее устройство | 1978 |

|

SU765880A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU903985A2 |

| Устройство для регистрации информации | 1979 |

|

SU864138A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| УСТРОЙСТВО ДЛЯ СТАТИСТИЧЕСКОЙ ОБРАБОТКИ ИНФОРМАЦИИ | 1972 |

|

SU357565A1 |

| Динамическое запоминающее устройство | 1982 |

|

SU1065886A1 |

а u isittittt

t«WKA ЗЧИКЛ 4«М(/1 f((NA/l бцИКЛ

n

С

d..

i-TLin

/-.1

п п п п

m

п Р

П п п п п

sj

и:

г ГЛ А А

п.

У

t

m

ft

П n П n П

p

л

Авторы

Даты

1981-01-23—Публикация

1979-04-02—Подача