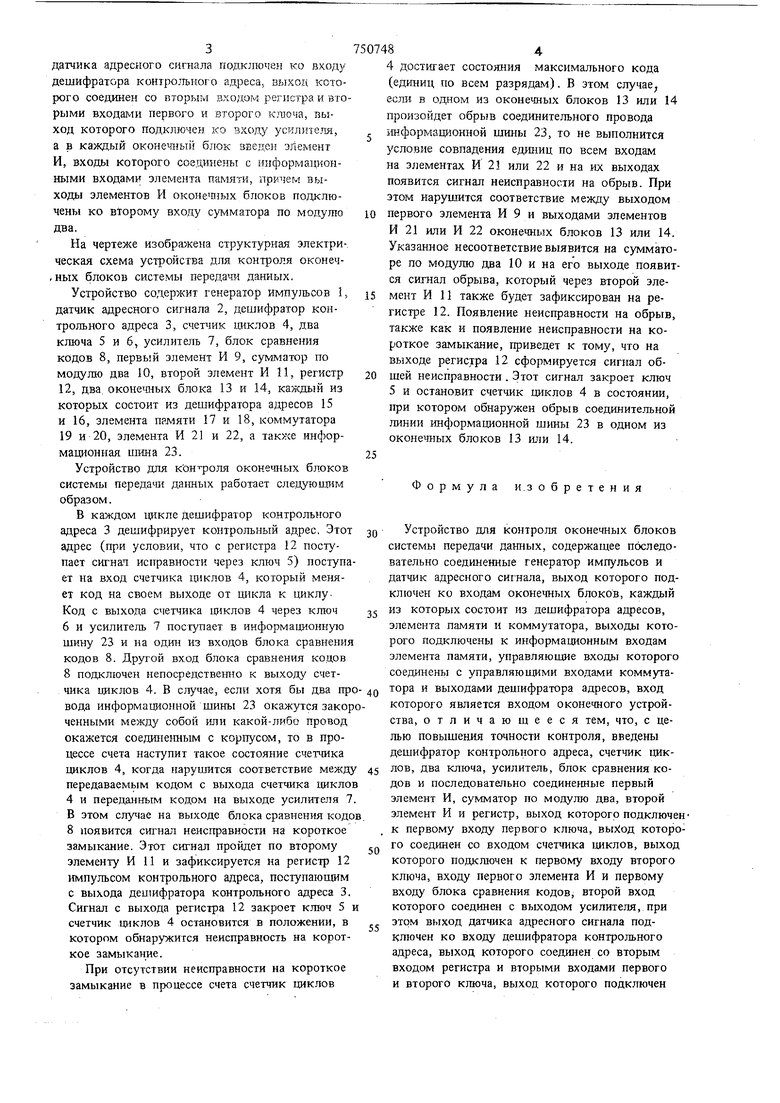

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОКОНЕЧНЫХ БЛОКОВ СИСТЕМЫ ПЕРЕДАЧИ ДАННЫХ Изобретение относится к радиотехнике и м жет использоваться для обмена информацией между блоками радиотехнических систем и процессорами. Известно устройство для контроля оконечных блоков системы передачи данных, содержащее последовательно соединенные генератор импульсов и датчик адресного сигнала, выход которого подключен ко входам оконечных блоков, каждый из которых состоит из дешифратора адребов, элемента памяти и коммутатора, выходы которого подключены к ин формационным входам элемента памяти, управ ляющие входы которого соединены с управляющими входами коммутатора и выходами дешифратора адресов, вход которого является входом оконечного устройства 1. Однако известное устройство не обеспечивает точность ксштроля целостности соединительных линий и информационной шины как на короткое замыкание, так и на обрыв. Цель изобретения - повышение точности контроля. Для этого в устройство для контроля оконечных блоков системы передачи данных, содержаш.ее последовательно соединенные генератор импульсов и датчик адресного сигнала, выход которого подключен ко входам оконечных блоков, каждый из которых состоит из дешифратора адресов, элемента памяти и коммутатора выходы которого подключены к информационным входам элемента памяти, управляющие входы которого соединены с управляющими входами коммутатора и выходами дешифратора адресов, вход которого является входом оконечного устройства, введены дешифратор контрольного адреса, счетчик циклов, два ключа, ус1шитель, блок сравнения кодов и последовательно соединенные первый элемент И, сумматор по модулю два, второй элемент И и регистр, выход которого подключен к первому входу первого ключа, выход которого соединен со входом счетчика циклов, выход которого подключен к первому входу второго ключа, входу первого элемента И и первому входу блока сравнения кодов, второй вход которого соединен с выходом усилителя, при этом выход датчика адресного сигнала подключен ко входу дешифратора контрольного адреса выход которого соединен со вторым входо у| регистра и вто рыми входами первого и второго ключа, выход которого Подключен ко входу усилителя, а в каждый оконевдый блок введен элемент И, входы которого соединены с информационными входами элемента пакшти, прячем выходы элементов И оконеиых блоков подключены ко второму входу сумматора по модулю два. На чертеже изобра кена структурная электрическая схема устройства для контроля оконеч,ных блоков системы передачи данных. Устройство содержит генератор импульсов I, датчик адресного сигнала 2, дешифратор контрольного адреса 3, счетчик циклов 4, два ключа 5 и 6, усилитель 7, блок сравнения кодов 8, первый элемент И 9, сумматор по модулю два 10, второй элемент И 11, регистр 12, два. оконечных блока 13 и 14, каждый из которых состоит из дешифратора адресов 15 и 16, элемента памяти 17 и 18, коммутатора 19 и 20, элемента И 2 и 22, а также информационная шина 23. Устройство для кон роля оконечных блоков системы передяШ данных работает сладуюидим образом. В каждом цикле Дешифратор контрольного адреса 3 дешифрирует контрольный адрес. Это адрес (нри условии, что с регистра 12 поступает сшнал исправности через ключ 5) поступ ет на вход счетчика циклов 4, который меняет код на своем выходе от цикла к циклуКод с выхода счетчика циклов 4 через ключ 6 и усилитель 7 поступает в информационную шину 23 и на один из входов блока сравнени кодов 8. Другой вход блока сравнения кодов 8 подключен непосредстветю к выходу счетчика циклов 4. В , если хотя бы два пр вода информационной шины 23 окажутся зако ченными межру собой или какой-либо провод окажется соедине}шым с корпусом, то в процессе счета наступит такое состояние счетчика циклов 4, когда нарушится соответствие между передаваемь1м кодом с выхода счетчика циклов 4 и переданным кодом на выходе усилителя 7. В этом случае на выходе блока сравнения кодов 8 появится сигнал неисправности на короткое замыкание. Этот сигнал пройдет по второму элементу И 11 и зафиксируется на регистр 12 импульсом контрольного адреса, поступаюшим с выхода дешифратора контрольного адреса 3. Сигнал с выхода регистра 12 закроет ключ 5 и счетчик циклов 4 остановится в положении, в котором обнаружится неисправность на короткое замыкание. При отсутствии неисправности на короткое замыкание в процессе счета счетчик циклов 4достигает состояния максимального кода ( по всем разрядам). В этом случае, ес.ш1 в одном из оконечных блоков 13 или 14 произойдет соединительного провода 1шформационной шины 23, то не выполнится условие совпадения ед1шиц по всем входам на э))ементах И 21 или 22 и на их выходах появится сигнал неисправности на обрыв. При этом нарушится соответствие между выходом первого элемента И 9 и выходами элементов И 21 или И 22 оконечных блоков 13 или 14. Указанное несоответствие выявится на сумматоре по модулю два 10 и на его выходе появится сигнал обрыва, который через второй элемент И 11 также будет зафиксирован на регистре 12. Появление неисправности на обрыв, также как и появление неисправности на короткое замыкание, приведет к тому, что на выходе регистра 12 сформируется сигнал обшей неисправности. Этот сигнал закроет ключ 5и остановит счетчик циклов 4 в состоянии, при котором обнаружен обрыв соединительной линии информационной Ш1шы 23 в одном из оконечных блоков 13 или 14. Формула и.з обретения Устройство для контроля оконечных блоков системы передачи данных, содержащее пскледовательно соединенные генератор импульсов и датчик адресного сигнала, выход которого подключен ко входам оконечных блоков, каждый из которых состоит из дешифратора адресов, элемента памяти и коммутатора, выходы которого подключены к информационным входам элемента памяти, управляющие входы которого соединены с управляющими входами коммутат°Р выходами дешифратора адресов, вход которого является входом оконечного устройства, отличающееся тем, что, с целью повышения точности контроля, введены дешифратор контрольного адреса, счетчик цик ключа, усилитель, блок сравнения кодов и последовательно соединенные первый элемент И, сумматор но модулю два, второй элемент И и регистр, выход которого подключен к первому входу первого ключа, которого соединен со входом счетчика циклов, выход которого подключен к первому входу второго ключа, входу первого элемента И и первому входу блока сравнения кодов, второй вход которого соединен с выходом усилителя, при этом выход датчика адресного сигнала подключен ко входу дешифратора контрольного адреса, выход которого соединен со вторым входом регистра и вторыми входами первого и второго ключа, выход которого подключен

ко входу усилителя, а в каждый оконечный блок введен элемент И, входы которого соединены с информацио1шыми входами элемента памяти, причем выходы элементов И оконечных блоков подключены ко второму входу сумматора по модулю два.

7507486

Источники информации, принятые во внимание при экспертизе 1. Нику И. Д. Стандартные сопряжения внешних устройств микропроцессоров сборник ТИИЭР Техника и применение микропроцессоров, т. 64, 1976, с, 82-85 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство для контроля высоковольтного тиристорного вентиля | 1983 |

|

SU1153374A1 |

| Устройство магнитной записи сигналов цифровой информации | 1983 |

|

SU1157566A1 |

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля | 1985 |

|

SU1295421A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Устройство управления последовательностью операций цифрового вычислителя | 1984 |

|

SU1198521A1 |

| Двухканальное запоминающее устройство | 1982 |

|

SU1023394A1 |

Авторы

Даты

1980-07-23—Публикация

1978-04-17—Подача