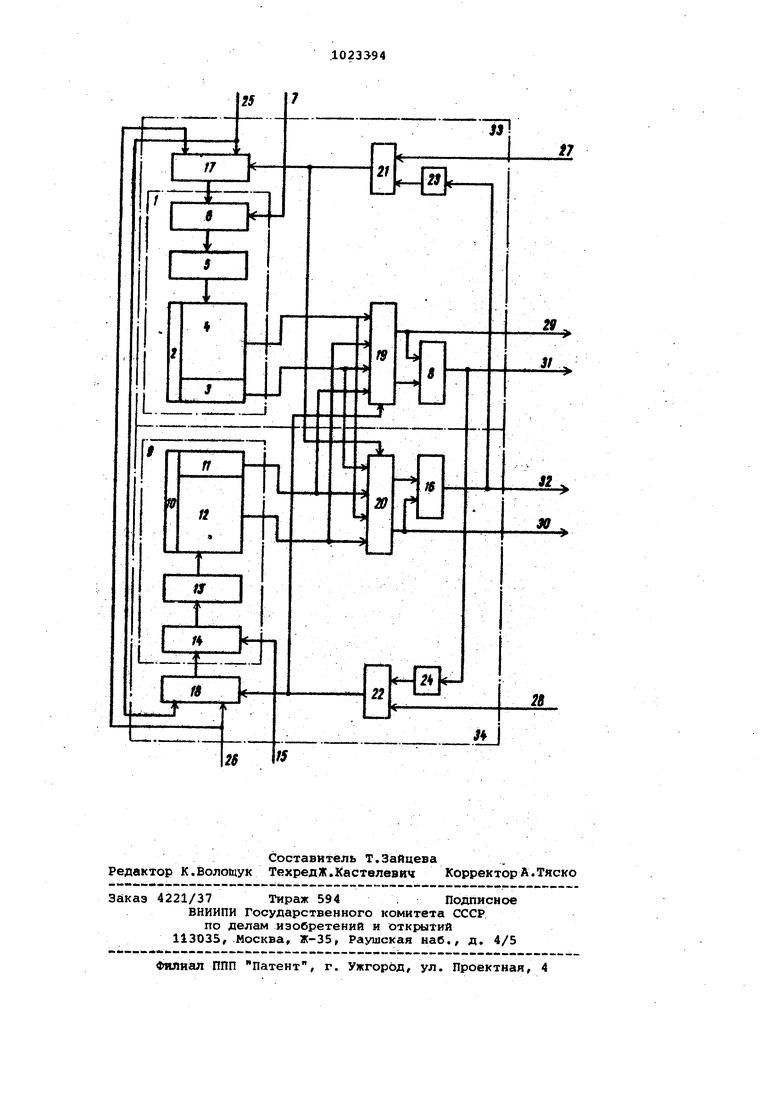

Изобретение относится к вычислительной технике и может быть исполь зовано в ЦВМ и-устройствах обработки информации для хранения информации. Известно двухканальное запоминаю шее устройство содержащее регистр адреса, дешифратор номера модуля, несколько однотипных модулей с регистрами, две группы ИЛИ, блок коммутации моделей, корректируюкий блок со схемами контроля, ре гистр слова и блок управления lj . Недостатком этого устройства является низкая надежность. Наиболее близким техническим решением к данному изобретению являет ся двухканальное запоминающее устро ство, содержащее два блока контроля и два блока памяти, каждый из которых состоит из накопителя с контрол ной и с информационной частями, де1лифратора адреса, регистра адреса, элемент И и группу элементов И, причем адресные шины накопителя подклю чены к выходам дешифратора адреса, соединенного с выходами регистра адреса, аршины информационной части накопителя подключены к входам блока контроля, вторые входы которого соединены с шинами контрольной части второго накопителя, выходы блоков контроля подключены к соответствующим входам элемента И, соединенного с управляющим входом группы элементов И, информационные входы которой подключены к шинам информационных частей обои-х накопителей, выходы рруппы элементов И являются выходами запоминающего устройства, входы кото рого подключены параллельно к входам регистров адреса обоих блоков памяти 2.. Недостатками известного устройств является низкая надежность, так Как оно не позволяет заменять неисправную ячейку памяти, а также то, что это устройство нельзя использовать для нескольких одновременно работающих внешних блоков, измеющих отличаю щиеся друг от друга адреса, что огра ничивает область его применения. Цель изобретения - расширение области применения устройства за счет обеспечения одновременной работы его с внешними устройствами с различной сдцресацией, а также повышение надежности устройства. Поставленная цель достигается тем, что в двухканальное запоминающее устройство, содержащее блоки контроля, первый элемент И и блоки памяти, каждый из которых состоит из накопителя, дешифратора адреса и регистра адреса,причем адресные входы первого и второго накопителей подключены соответственно к выходам первого и второго дешифраторов адреса, входы которых соединены соответственно с выходами первогорегистра адреса и с выходами второго регистра адреса, управляющие входы первого и BTopofo регистров адреса являются соот- , ветственно первым и вторым адресными входами устройства, введены второй элемент И, коммутаторы и элементы НЕ, причем выходы первого коммутатора подключены к входам первого регистра адреса, .а первый и второй входы - соответственно к второму и к первому входам второго коммутатора, выходы которого соединены с входами второго регистра адреса, информационные выходы первого накопителя подключены к одним из информационных входов третьего и четвертого коммутаторов, другие информационные входы которых соединены с информационными выходами второго накопителя, контрольные выходы которого подключены к одним из контрольных входов третьего и четвертого коммутаторов, другие контрольные входы.которых соединены с контрольными выходами первого накопителя, управляющие входы первого и четвертого коммутаторов, подключе ны к выходу первого элемента И, первый вход которого соединен с выходом первого элемента НЕ, управляющие входы второго и третьего коммутаторов подключены к выходу второго элемента И, первый вход которого соединен с выходом элемента НЕ, первый и второй выходы третьего коммутатора подключены к входам первого блока контроля, выход которого соединен с входом второго элемента НЕ, первый и второй выходы четвертого коммутатора подключены к входам второго блока контроля, выход которого соединен с входом второго элемента НЕ, первый вход первого коммутатора, первый выход третьего коммутатора, второй вход первого элемента И и выход первого блока контроля являются соответственно информационными входом и выходом и управляющими входом и выходом первого канала устройства, первый вход второго коммутатора и первый выход четвертого коммутатора, второй вход второго элемента И и выход второго блока контроля являются соответственно информационЕшми входом и выходом и управляющими входом и выходом, второго канала устройства. На чертеже представлена функциоНсшьная схема устройства. Устройство содержит первый блок 1 памяти, состояюий из первого накопителя 2 с контрольной частью 3 и информационной частью 4, первого дешифратора 5 адреса и первого регистра б адреса с управляющим входом 7,первый блок 8 контроля, второй блок 9 памяти, состоящий из второго накопи- теля 10 с контрольной частью 11 и информационной частью 12, второго дешифратора 13 адреса и второго регистра 14 адреса с управляющим входо :15, второй блок 16 контроля, первый 17 и второй 18 коммутаторы, предназначенные для коммутации адресов, тре тий 19 и четвертый 20 коммутаторы, предназначенные для коивдутации выход кых сигналов, первый 21 и второй 22 элементы И, первый 23 и второй 24 элементы НЕ. На чертеже обозначены информационные 25 и 26 и управляюшие 27 и 26 входы устройства, информационные 29 и 30 и управляющие 31 и 32 выхо;гд устройства, первый 33 и второ 34 каналы устройства. Накопители 2 и 10 выполняются идентичными. Устройство работает следующим обраэом. В исходном состоянии при Hcnpaatod каналах 33 и 34 устройства входы регистров 6 и 14 через коко утаторы 1 и 18 подключены соответственно к входам 25 и 26 устройства, а выходы накопителя 2 и 10 через коммутато|ш 19 и 20 подключены соответственно к выходам 29 и 30 и через блоки 8 и 16 .к выходги 31 и 32. В этом случае каж дый из каналов 33 и 34 работает само стоятельно на свое внешнее устройств При этом по адресам, поступаютим на входы 25 (или 26), из накопителя 2(10) выбирается заданное слово с информационными и контрольными сигна лами, которое, пройдя через коммута;.тор 19 (20), поступает непосредственн на выходы 29 {ЗО) и через блок 8(;1б)на выходы 31 (32) устройства, связанные с входа1ии соответствующего внешнего устройства. Блоки 8 и 16 в этом слуЧа:е вырабатывают сигналы, характеризующие исправность работы каналов 33 и 34 устройства. При неисправной работе, например, первого 33 (или второго 34) кэ(нала устройства на выходе 31 (32) формируется сигнал ошибки, который фиксирует адрес на входе 25(26) неисправного канала 33 (34) и разрешает формирование сигнала БП 1I своб. на входе 28 (или сигнала БП 1 своб. - на входе 2) . При наличии сигнала на входе 28 (27) зафиксированный адрес с входа 25(26) поступает;через коммутатор 18(17) на входы регистра 14(6) По этому адресу из накопителя 10(2) выбирается необходимей информация и передается через кемимутатор 19 (20) на выходы 29 (30) запоминающего устройства (при этом информация с выходов 30(29) и 32(31) не используется, так как в этот момент формируется сигнал БП Нсвоб. - на входе 2В или БП1СВО6. - на входе 27), На выходе 31 2) формируется сигнал Ошибки нет, который снимает блокировку адреса на входе 25(26) и блокирует формирование сигнала БП 1 своб. на входе 28 или сигнала БП 1 свое. - на входе 27), после чего каналы 33 и 34 вновь работают самостоятельно, каждшй 1на свое устройство. Таким образом,.расширяется область применения устройства вследствие возможности использования его для двух одновременно работающих внешних устройсо-в, имеющих различную адресацию, а также повыиается надежность устройства благодаря обеспечению , возможности замены любой из неисправных ячеек исправной ячейкой из другого, неработакяаего в данныймомент канала..

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1056274A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU957277A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Оперативное запоминающее устройство с контролем по Хэммингу | 1983 |

|

SU1127011A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Постоянное запоминающее устройство с резервированием | 1986 |

|

SU1372363A1 |

| Устройство для контроля оперативных запоминающих блоков | 1980 |

|

SU890442A1 |

| Резервированное оперативное запоминающее устройство | 1982 |

|

SU1137538A1 |

ДВУХКАНАЛЬНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее блоки контроля, первый элемент И и блоки памяти, казадилй из которых состоит кз накопителя , дешифратора адреса и регистра адреса, причем-адресные входы первого и второго накопителей подключены соответственно к выходам первого и второго дешифраторов адреса, входы которых соединены соответственно с, выходами первого регистра адреса и с выходами второго регистра адреса, управляющие входы первого и второго регистров адреса являются соответственно первым и вторым адресными входами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет обеспечения одновременной работы его с внешними устройствами с различной адресацией, в него ввейены второй элемент И, коммутаторы и элементы НЕ, причем выходы первого коммутатора подключены к входс1м первого регистра адреса, а первый и второй входы - соответственно к вторсэму и к первому входам второго коммутатора, выходы которого соединены с входами второго регист раГ адреса, информационные выходы первого накопителя подключешл к одним из инфо1.1ационных входов третьего и четвертого коммутаторов, другие информационные входы которых соединены с информационными выходами второго накопителя, контрольные выходы которого подключены к одним из контрольных входов третьего и четвертого коммутаторов, другие крнтрольные входы которых соединены с контрольными выходсц ш первого накопителя, управляюшие входы первого и четвертого коммутаторов подключены к выходу первого элемента И, первый вход которого соединен с выходом первого элемента НЕ, управляюшие вхо-в ды второго и третьего коммутаторов (Л подключены к выходу второго элекгента И, первый вход которого соединен с выходом элемента НЕ, первый и второй выходы третьего коммутатора под3 ключены к входам первого блока конт- роля, выход которого .соединен с входом -второго элемента НЕ, первый и второй выходы четвертого коммутатора подключены к входам блока 1C контроля, выход которого соединен с входом второго элемента НЕ, первый ОО СО вход первого коммутатора, первый выход третьего коммутатора, второй вход первого элемента И и выход со первого блока контроля являются со4iiii ответственно информационными входом. и выходом и управляющими входом и выг ходом первого канала устройства, первый вход второго коммутатора и первый выход четвертого коммутатора, второй вход второго элемента И и выход второго блока контроля являются соответственно информационными входом и выходом и управляющими входом и выходом второго кангша устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Самофалов К.Г | |||

| и лр | |||

| Структурно-логические методы повьшения надежности запоминающих устройств | |||

| М,, Машиностроение, 1976, с | |||

| Парный автоматический сцепной прибор для железнодорожных вагонов | 0 |

|

SU78A1 |

| Способ очистки нефти и нефтяных продуктов и уничтожения их флюоресценции | 1921 |

|

SU31A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР по заявке В 2931121/18-24, кл.G 11 С 29/00, 1980.(прототип). | |||

Авторы

Даты

1983-06-15—Публикация

1982-01-06—Подача