Изобретение относится к вычислительной технике и может быть исполь зовано в специализированных вычисли тельных машинах. Известно арифметическое устройUTBO, содержащее приемный регистр, сумматор, регистр результата, регис множителя, два дополнительных регис тра 1. Однако в этом устройстве отсутствует контроль выполняемых операций, что снижает надежность его работы. Наиболее близким к предлагаемому по технической сущности является . арифметическое устройство, содержащее регистр первого операнда, элементы И, блок сверток, сумматор, ре гистр результата, регистр второго операнда, сдвиговый регистр множите ля, дополнительный сумматор, схему кодирования, схему сравнения и блок формирования признаков ошибок, первый вход которого соединен с выходо сдвигового регистра множителя, второй - с первым выходом второго операнда, а третий - с выходом блока сверток, выходы первого и второго сумматоров соединены соответственно с первым и вторым входами схемы кодирования, а также через первый и второй вентили соответственно с пер- вым и BTOpbiM входами регистра результатов и схемы сравнения, выход которой соединен с четвертым входом блока формирования признаков, выход схемы кодирования соединен с третьим входом регистра результатов, первый выход которого соединен через третий вентиль с первым входом, второй через четчеотый и пятый вентили соединен с вторым и -третьим входом регистра второго операнда, выходы которого через шестой, седьмой, восьмой и девятый- вентили соединены соот ветственно со вторыми входами первого и второго сумматоров и первым и вторым входами блока сверток, третий выход регистра второго операнда соединен с входом регистра множителя 12 . Недостатком известного устройства является сложность формирования контрольных кодов результата и операнда сдвигаемого вправо, что снижает быстродействие устройства и требует большого объема аппаратуры. Наличие четырех сверток и схемы сравнения не гарантирует правильности результата, так как контроль регистра реэул1}тата по окончании выполнения one.рации отсутствует. Операция Сдвиг влево осу1цествляется сложениемчисла с самим собой/ что ограничивает функциональные возможности и также снижает быйтродействие устройства.

Цель изобретения - упрощение устройства и повышение быстродействия.

. Поставленная цель достигается тем,

что в устройство, содержащее регистр первого операнда, два сумматора, регистр второго операнда, регистр результата, узлы свертки, схему сравнения, коммутаторы, причем выход регистра первого операнда соединен .с первым входом первого коммутатора и через узел свертки - с первым входом первой схемы сравнения, второй вход которой является входом контрольного кода устройства, а выход - входом сигнала ошибки приема операнда устройства, второй и третий входы первого коммутатора являются соответственно управляющими

входами прямого и инверсного кода устройства, выход первого коммутатора соединен с первыми входами первого и второго сумматоров, выход первого сумматора соединен с первым входом регистра результата, введены два дополнительных регистра и схема сравнения, причем выход второго сумматора соединен с первым входом регистра второго операнда, второй вход которого и второй вход регистра результата соединены со входом управлякяцего сигнала переписи устройства, выходы регистра результата.и регистра второго операнда соединены соответственно с первыми входами второго и третьего коммутаторов, вторые, третьи и четвертые входы которых . являются соответственно управляющими входами Тип операции , Сдвиг влевои Сдвиг вправо устройства, выходы второго и третьего коммутаторов через первый и второй дополнительные регистры соединены соответственно со вторыми входами первого и второго сумматоров, выход регистра результата соединен с иервым входом схемы сравнения, через второй узел свертки - с выходом контрольного кода устройства и является .информационным выходом устройства, выход регистра второго операнда соединен с пнтым входом второго коммутатора и вторым входом схемы сравнения, выход которой является выходом правильности выполнения операции устройства, соединены соответ;ственн6 с третьим, четвертым и пятым входами третьего коммутатора

и пятым, шестым и седьмым входами устройства.

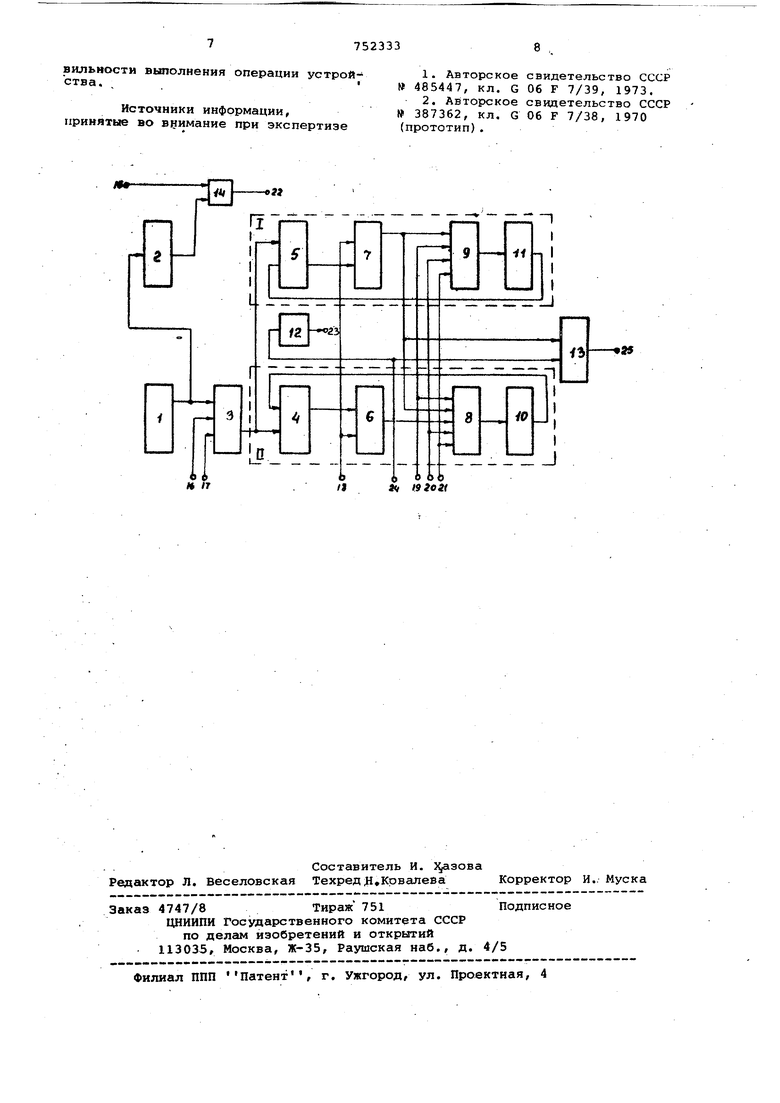

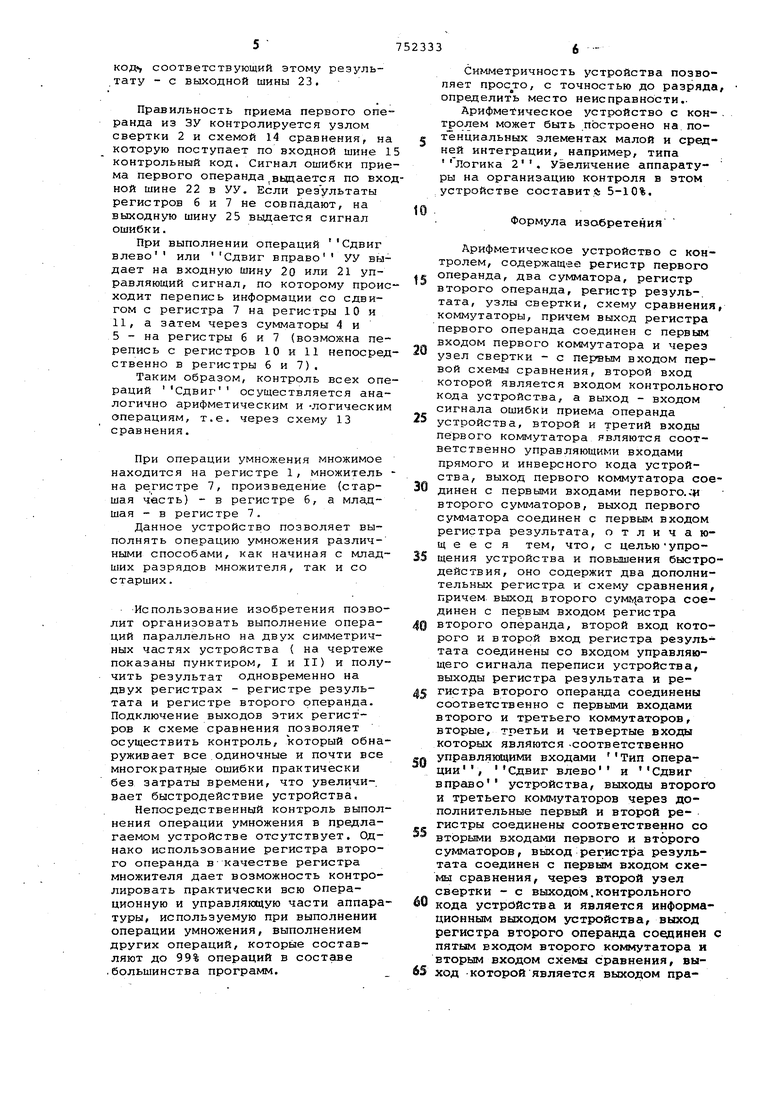

На чертеже приведена схема уйтройства.

Устройство содержит регистр 1 первого операнда, узел 2 свертки, коммутатор 3, комбинационные сумматоры 4 и 5, регистр 6 результата, регистр 7 второго операнда, коммутаторы 8, 9, дополнительные регистр 10, 11, узел 12 свертки, схемы 13, 14 сравнения, входы 15-21 устройства, выходы 22-25 устройства.

Выход регистра 1 соединен с уз-лом 2 свертки и через первый коммутатор 3 с входом первого 4 и второг

5сумматоров, выходы сумматоров соединены с входами регистра 6 результата и регистра 7 второго операнда,

выходы которых через второй 8 и третий 9 коммутаторы соединены с входами первого 10 и второго 11 дополнтельных регистров, выходы регистров 10 и 11 соединены соответдтвенно с входами первого и второго сумматоров, выход регистра

6результата соединен со входом узла 12 свертки и входом схемы 13 сравнения второй вход которой соединен с выходом регистра 7 второго

.операнда, выход узла 2 свертки соединен со второй схемой 14 сравнения

Входные шины 15-21 служат для приема управляющих сигналов. Выходные шины 22-25 служат для выдачи результатов операции и правильности ее выполнения.

icтройство работает следующим образом.

Перед выполнением операции один из операндов считывается на регистр 1 из ЗУ, другой, являющийся результатом предьщущей операции, находится на регистре 7. Выполнение операции начинается подачей ( в зависимости от типа операции) управляюцих сигналов на входные шины 16 или 17 и 19, в результате чего первый операнд через коммутатор 3 в прямом или инверсном виде подается на первый вход первого 4 и второго 5 сумматоров.Одновременно второй операнд из регистра 7 через коммутаторы 8 и 9 поступает на вход первого 10 и второго 11 дополнительных регистров а затем на второй вход сумматоров 4 и 5. Полученные на выходах сумматоров 4 и 5 результаты операции по синалу из устройства управления, поступающему на входную шину 18, переписываются на регистр результата 6 и регистр второго операнда 7.

С выходов регистров б и 7 результаты параллельно поступают на входы схемы 13 сравнения. При совпаден результатов с выхода 25 схемы 13 сравнения выдается сигнал правильности выполнения операции. В этом .случае результат операции снимается с выходной шины 24, а контрольный

код, соответствующий этому результату - с выходной шины 23.

Правильность приема первого операнда из ЗУ контролируется узлом свертки 2 и схемой 14 сравнения, на которую поступает по входной шине 1 контрольный код. Сигнал ошибки приема первого операнда вьщается по вхоной шине 22 в УУ, Если результаты регистров 6 и 7 не совпадают, на выходную шину 25 выдается сигнал ошибки.

При выполнении операций Сдвиг влево или Сдвиг вправо УУ выдает на входную шину 20 или 21 управляющий сигнал, по которому происходит перепись информации со сдвигом с регистра 7 на регистры 10 и 11, а затем через сумматоры 4 и 5 - на регистры 6 и 7 (возможна перепись с регистров 10 и 11 непосредственно в регистры б и 7).

Таким образом, контроль всех операций Сдвиг осуществляется аналогично арифметическим и -логическим операциям, т.е. через схему 13 сравнения.

При операции умножения множимое находится на регистре 1, множитель на регистре 7, произведение (старшая честь) - в регистре б, а мла,ц шая - в регистре 7.

Данное устройство позволяет выполнять операцию умножения различными способами, как начиная с младших разрядов множителя, так и со старших.

Использование изобретения позволит организовать выполнение операций параллельно на двух симметричных частях устройства ( на чертеже показаны пунктиром, I и II) и получить результат одновременно на двух регистрах - регистре результата и регистре второго операнда. Подключение выходов этих регистров к схеме сравнения позволяет осуществить контроль, который обнаруживает все одиночные и почти все многократн 1е ошибки практически без затраты времени, что увеличи-. вает быстродействие устройства.

Непосредственный контроль выполнения операции умножения в предлагаемом устройстве отсутствует. Однако использование регистра второго операнда в качестве регистра множителя дает возможность контролировать практически всю операционную и управляющую части аппаратуры, используемую при выполнении операции умножения, выполнением других операций, которые составляют до 99% операций в составе .большинства программ.

Симметричность устройства позвопяет , с точностью до разряда, определить место неисправности..

Арифметическое устройство с кон-. тролем может быть построено на потенциальных элементах малой и средней интеграции, например, типа Логика . Увеличение аппаратуры на организацию контроля в этом устройстве составите 5-10%.

Формула изобретения

Арифметическое устройство с контролем, содержащее регистр первого g операнда, два сумматора, регистр второго операнда, регистр резуль-. тата, узлы свертки, схему сравнения, коммутаторы, причем выход регистра первого операнда соединен с первым входом первого коммутатора и через узел свертки - с первым входом первой схемы сравнения, второй вход которой является входом контрольного кода устройства, а выход - входом сигнала ошибки приема операнда

5 устройства, второй и третий входы первого коммутатора являются соответственно управляющими входами прямого и инверсного кода устройства, выход первого коммутатора сое0динен с первыми входами первого.:и второго cy 1мaтopoв, выход первого сумматора соединен с первым входом регистра результата, отличающееся тем, что, с цельюупро5щения устройства и повышения быстродействия, оно содержит два дополнительных регистра и схему сравнения, причем выход второго сумь атора соединен с первым входом регистра второго операнда, второй вход которого и второй вход регистра результата соединены со входом управляющего сигнала переписи устройства, выходы регистра результата и регистра второго операнда соединены соответственно с первыми входами второго и третьего коммутаторов, вторые, третьи и четвертые входы которых являются -соответственно управляющими входами Тип операции, Сдвиг влево и Сдвиг вправо устройства, выходы второго и третьего коммутаторов через дополнительные первый и второй регистры соединены соответственно со

5 вторыми входами первого и второго сумматоров, выходрегистра результата соединен с первым входом схеЛЫ сравнения, через второй узел свертки - с выходом.контрольного

0 кода устройства и является информационным выходом устройства, выход регистра второго операнда соединен с пятым входом второго коммутатора и вторым входом схемы сравнения, выход которой является выходом правильности вьтолнения операции устройства.

Источники информации, принятые во В1нимание при экспертизе

свидетельство СССР Об F 7/39, 1973.

свидетельство СССР 06 F 7/38, 1970

| название | год | авторы | номер документа |

|---|---|---|---|

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО С КОНТРОЛЕМ И КОРРЕКЦИЕЙ ОШИБОК | 1973 |

|

SU387362A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Устройство для умножения с контролем | 1989 |

|

SU1741128A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для контроля умножения по модулю три | 1986 |

|

SU1361556A1 |

| Арифметико-логическое устройство связного процессора | 1978 |

|

SU765808A1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Процессор быстрого преобразования Фурье | 1986 |

|

SU1388892A1 |

| Процессор быстрого преобразования Фурье | 1985 |

|

SU1247891A1 |

/7

/ att 19 ген

Авторы

Даты

1980-07-30—Публикация

1978-07-13—Подача