арифметико-логического устройства подключен к первому входу регистра кода заявки, первый выход которого подключен к первому входу блока формирования запроса,первый выход которого соединен с первым входом блока формирования сигналов сопровождения,выход которого подключен к первому входу блока выдачи,в торой вход .которого соединен со вторым выходом арифметико-логического устройства, третий выход которого подключен к первому входу блока формирования сигналов состояния, второй вход которого соединен с первым выходом блока приема, второй выход которого соединен с первым входом арифметикологического устройства, выход блока синхронизации подключен ко второму входу блока формирования сигналов сопровождения, второму входу блока формирования запроса и Первому входу блока приоритета, выход которого соединен с третьим входом блока формирования сигналов сопровождения, второй выход блока формирования запрсов соединен со вторым входом блока приоритета, входы блоков синхронизации всех процессоров являются синхронизирующим входом системы, первые входы блоков приема и выходы блоков выдачи всех процессоров являются входами-выходами системы,выход блока формирования сигналов состояния одного процессора соединен с соответствующим входом группы входов блоков формирования запросов других процессоров, второй вход блока формирования запроса одного процессора соединен с соответствующим входом группы входов блока приоритета других процессоров, введены в каждый процессор формирователь сигнала квитанции и блок сравнения сигналов квитанции, первый выход которого подключен к третьему входу блока формирования запроса, второй выход регистра кода заявки соединен с первым входом блока сравнения сигналов квитанции, второй выход которого соединен со вторым входом регистра кода заявки, третий вь1ход блока приема соединен с первым входом формирователя сигнала квитанции, выход которого соединен с третьим входом блока формирования сигнала состояния и вторым входом арифметико-логического устройства, выход блока синхронизации подключен ко второму входу формирователя сигнала квитанции и третьему входу блока сравнения сигналов квитанции, при этом выход формирователя сигнала квитанции одного процессора соединен с соответствующим входом группы входов блока сравнения сигналов квитанции других процессоров, а второй вход блока приема одного процессора подключен к соответствующему выходу

группы выходов блока формирования сигналов сопровождения других процесоров, выход блока приоритета соединен со вторым входом блока сравне сигналов квитанции.

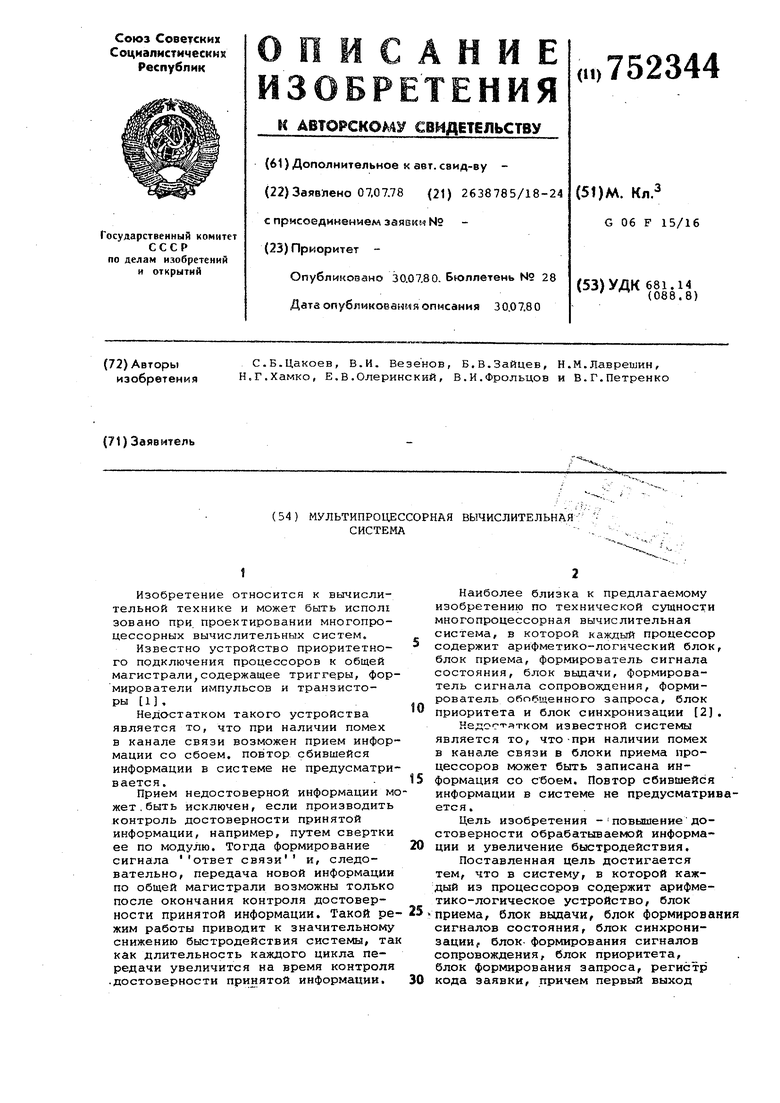

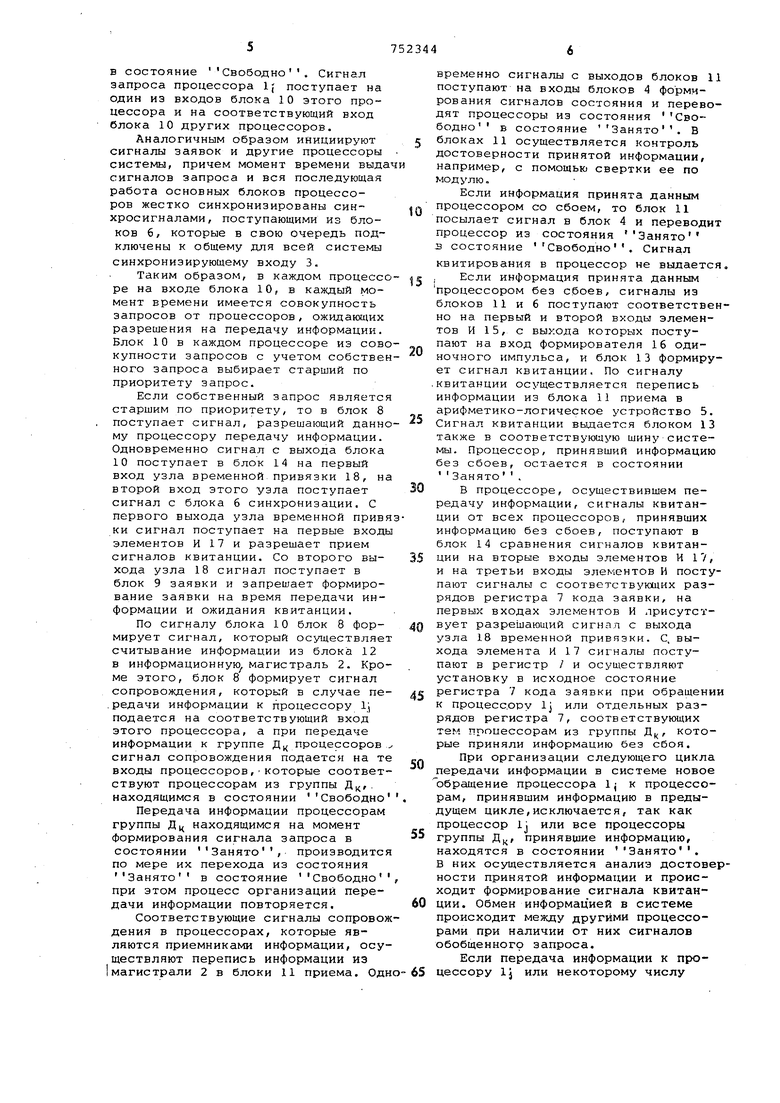

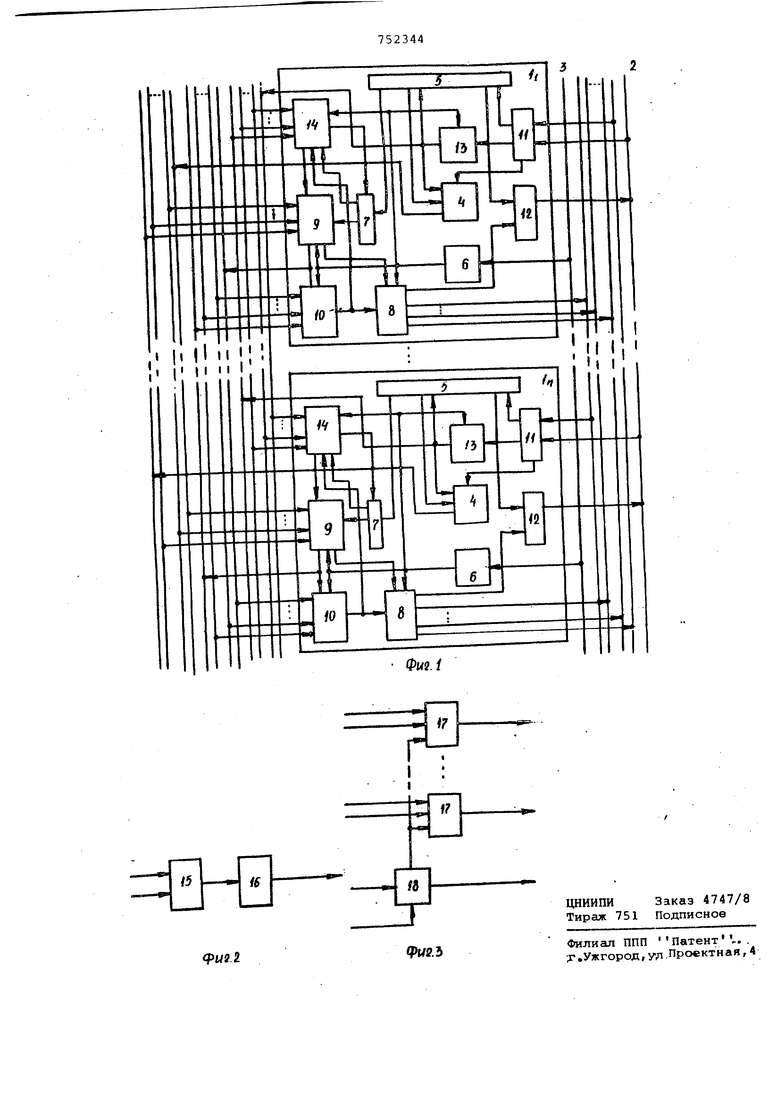

На фиг. 1 показана структурная схема системы и каждого процессора; на фиг. 2 - возможная реализация структурно-логического блока формирния сигнала квитанции; на фиг.З структурно-логическая схема блока сравнения сигналов квитанции.

Мультипроцессорная вычислительна система содержит процессоры li - If информационную магистраль 2, синхронизирующий вход 3, а каждый процессор содержит блок 4 формирования синалов состояния, арифметико-логическое устройство 5, блок б синхронизации, регистр 7 кода заявки, бло 8 формирования сигналов сопровождения, блок 9 формирования запроса, блок 10 приоритета, блоки приема, блок 12 выдачи, формирователь 13 сигнала квитанции, блок 14 сравнени сигналов квитанции.

Блок 13 формирования сигналов квитанции состоит из элемента 15 И и формирователя одиночного импульса 16.

Блок 14 сравнения сигналов квитанции состоит их трехвходовых элементов 17 И по числу устройств в системе и узла временной привязки 1

Мультипроцессорная вычислительная система работает следукмдим образом.

При необходимости передачи информации от про-цессора 1, к любому процессору Ij 1 i | , j 1-п или к некоторой группе процессоров Д; с д ij , 1р,...,1 ,п где Д li,l2f...rln3 , при этом 12, п - 1 и и , из блока 5 в регистр 7 кода заявки поступает код, соответствующий адресу процессора, или код, соответствующий дизъюнкции кодов всех адресов процессоров, входящих в группу Д|.

Одновременно в блок 12 выдачи из блока 5 поступает информация, которая должна быть передана в процессор Ij или всем процессорам группы Дц. С выхода регистра 7 кода заявки процессора 1 код заявки поступает в блок 9 этого процессора

На группу входов блока 9 процессора 1« поступают сигналы состояния других процессоров. Блок 9 формирует сигнал заявки только в том случае, если процессор Ij , или хотя бы один из процессоров группы Дц, находится в состоянии Свободно, в противном случае сигнал обобщенной заявки не формируется до момента перехода процессора Ij , или хотя бы Одного процессора из группы Д, из состояния Занято в состояние Свободно, Сигнал запроса процессора Ij поступает на один из входов блока 10 этого процессора и на соответствующий вход блока 10 других процессоров. Аналогичным образом инициируют сигналы заявок и другие процессоры системы, причем момент времени выда сигналов запроса и вся последующая работа основных блоков процессоров жестко синхронизированы синхросигналами, поступающими из блоков 6, которые в свою очередь подключены к общему для всей системы синхронизирующему входу 3. Таким образом, в каждом процесс ре на входе блока 10, в каждый момент времени имеется совокупность запросов от процессоров, ожидаюашх разрешения на передачу информации. Блок 10 в каждом процессоре из сов купности запросов с учетом собстве ного запроса выбирает старший по приоритету запрос. Если собственный запрос являетс старшим по приоритету, то в блок 8 поступает сигнал, разрешающий данн му процессору передачу информации. Одновременно сигнал с выхода блока 10 поступает в блок 14 на первый вход узла временной привязки 18, н второй вход этого узла поступает сигнал с блока 6 синхронизации. С первого выхода узла временной прив ки сигнал поступает на первые вход элементов И 17 и разрешает прием сигналов квитанции. Со второго выхода узла 18 сигнал поступает в блок 9 заявки и запрещает формирование заявки на время передачи информации и ожидания квитанции. По сигналу блока 10 блок 8 формирует сигнал, который осуществляе считывание информации из блока 12 в информационную магистраль 2. Кро ме этого, блок 8 формирует сигнал сопровождения, который в случае пе .редачи информации к процессору Ц подается на соответствующий вход этого процессора, а при передаче информации к группе Д процессоров сигнал сопровождения подается на т входы процессоров,которые соответ ствуют процессорам из группы Д,, . находящимся в состоянии Свободно Передача информации процессорам группы Д находящимся на момент формирования сигнала запроса в состоянии Занято, производитс по мере их перехода из состояния Занято в состояние Свободно при этом процесс организаций передачи информации повторяется. Соответствующие сигналы сопрово дения в процессорах, которые являются приемниками информации, осу ществляют перепись информации из I магистрали 2 в блоки 11 приема. Од временно сигналы с выходов блоков 11 поступают на входы блоков 4 формирования сигналов состояния и переводят процессоры из состояния Свободно в состояние Занято. В блоках 11 осуществляется контроль достоверности принятой информации, например, с помощью свертки ее по модулю. Если информация принята данным процессором со сбоем, то блок 11 посылает сигнал в блок 4 и переводит процессор из состояния Занято а состояние Свободно. Сигнал квитирования в процессор не выдается, , Если информация принята данным процессором без сбоев, сигналы из блоков 11 и 6 поступают соответственно на первый и второй входы элементов И 15, с выхода которых поступают на вход формирователя 16 одиночного импульса, и блок 13 формирует сигнал квитанции. По сигналу квитанции осуществляется перепись информации из блока 11 приема в арифметико-логическое устройство 5. Сигнал квитанции выдается блоком 13 также в соответствующую шину системы. Процессор, принявший информацию без сбоев, остается в состоянии Занято. В процессоре, осуществившем передачу информации, сигналы квитанции от всех процессоров, принявших информацию без сбоев, поступают в блок 14 сравнения сигналов квитанции на вторые входы элементов И 17, и на третьи входы элементов И поступают сигналы с соответствующих разрядов регистра 7 кода заявки, на первых входах элементов И присутствует разрешающий сигнал с выхода узла 18 временной привязки. С, выхода элемента И 17 сигналы поступают в регистр / и осуществляют установку в исходное состояние регистра 7 кода заявки при обращении к процессору 1 или отдельных разрядов регистра 7, соответствующих тем процессорам из группы Д, которые приняли информацию без сбоя. При организации следующего цикла передачи информации в системе новое обращение процессора Ij к процессорам, принявшим информацию в предыдущем цикле,исключаете я, так как процессор Ij или все процессоры группы Д, принявшие информацию, находятся в состоянии Занято. В них осуществляется анализ достоверности принятой информации и происходит формирование сигнала квитанции. Обмен информацией в системе происходит между другими процессорами при наличии от них сигналов обобщенного запроса. Если передача информации к процессору 1J или некоторому числу процессоров из группы Д произошла со сбоем, то установка соответствую щих разрядов регистра 7 в исходное состояние не произойдет. По окончании сигнала-,, блокирующего формирование заявки и поступающего с узл i8 временной привязки, процессором if будет организована повторная передача информации. Использование предлагаемого устройства позволяет исключить возможность приема недостоверной инфор ции в арифметико-логическое устрой.ство за счет аппаратной организации повторного цикла передачи информации, если предыдущая передача произошла со сбоем, следовательно, позволяет расширить функциональные возможности данной многопроцессорной системы, а также повышает прои водительность ее. Формула изобретения .Мультипроцессорная вычислительн система, в которой каждый из проде соров содержит арифметико-логическое устройство, блок приема, блок в дачи, блок формирования сигналов состояния, блок синхронизации, блок формирования сигналов сопровож дения, блок приоритета, блок формир вания запроса, регистр кода заявки причем первый выход арифметико-логического устройства подключен к первому входу регистра кода заявки первый выход которого подключен к первому входу блока формирования запроса, первый выход которого соединен с первым входом блока формирования сигналов сопровождения,выхо которого подключен к первому входу блока выдачи,второй вход которого сое/1инен со вторым выходом арифмети ко-логического устройства,, третий выход которого подключен к первому входу блока формирования сигналов состояния, второй вход которого сое динен с первым выходом блока приема второй выход которого соединен с первым входом арифметико-логического устройства, выход блока синхронизации подключен ко второму входу блока формирования сигналов сопровождения, второму входу блока формирования запроса и первому входу Ьлока приоритета, выход которого соединен с третьим входом блока формирования сигналов сопровождени второй выход блока формирования запросов соединен со вторым входом блока приоритета, входы блоков синхронизации всех процессоров являются синхронизирующим входом системы, первые входы блоков приема и выходы блоков вьщачи всех прэцзссоров являются входами-выходами системы, выход блока формирования сигнала состояния одного процессора соединен с соответствующим входом группы входов блоков формирования запросов других процессоров, второй выход блока формирования запроса одного процессора соединен с соответствующим входом группы входов блока приоритета других процессоров, отличающаяся тем, что, с целью повышения достоверности обрабатываемой информации и увеличения быстродействия, в нее введены в каждый процессор формирователь сигнала квитанции и блок сравнения сигналов квитанции, первый выход которого подключен к третьему входу блока формирования запроса, второй выход регистра кода заявки соединен с первым входом блока сравнения сигналов квитанции, второй выход которого соединен со вторым входом регистра кода заявки, третий выход блока приема, соединен с первым входом формирователя сигнала квитанции, выход которого соединен с третьим входом блока фо4змирования сигнала состояния и вторым входом арифметико-логического устройства, выход блока синхронизации подключен ко второму входу формирователя сигнала квитанции и третьему входу блока сравнения сигналов квитанции, при этом выход формирователя сигнала квитанции одного процессора соединен с соответствующим входом группы входов блока сравнения сигналов квитанции других процессоров , а второй вход блока приема одного процессора подключен к соответствующему выходу группы выходов блока формирования сигналов сопровождения других процессоров, выход блока приоритета соединен со вторым входом блока сравнения сигналов квитанции. Источники информации, принятые во внимание при. экспертизе 1.Авторское свидетельство СССР № 317064, кл. G 06 F 9/18, 1971. 2.Авторское свидетельство СССР № 588900, кл. G 06 F 15/16, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивная система обработки данных | 1984 |

|

SU1241250A1 |

| Адаптивная система обработки данных | 1985 |

|

SU1312596A1 |

| Микропрограммируемый векторный процессор | 1987 |

|

SU1594557A1 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| Микропрограммное устройство управления | 1988 |

|

SU1649540A1 |

| Адаптивная система обработки данных | 1987 |

|

SU1455342A1 |

| Многоуровневое устройство для коммутации процессоров в многопроцессорной вычислительной системе | 1984 |

|

SU1187174A1 |

| Устройство для обмена информацией междуэлЕКТРОННОй ВычиСлиТЕльНОй МАшиНОй(эВМ) и уСТРОйСТВАМи ВВОдА и ВыВОдА | 1979 |

|

SU809140A1 |

| Микропроцессор | 1984 |

|

SU1242975A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

Авторы

Даты

1980-07-30—Публикация

1978-07-07—Подача