другим выводом соответствующего резистора.

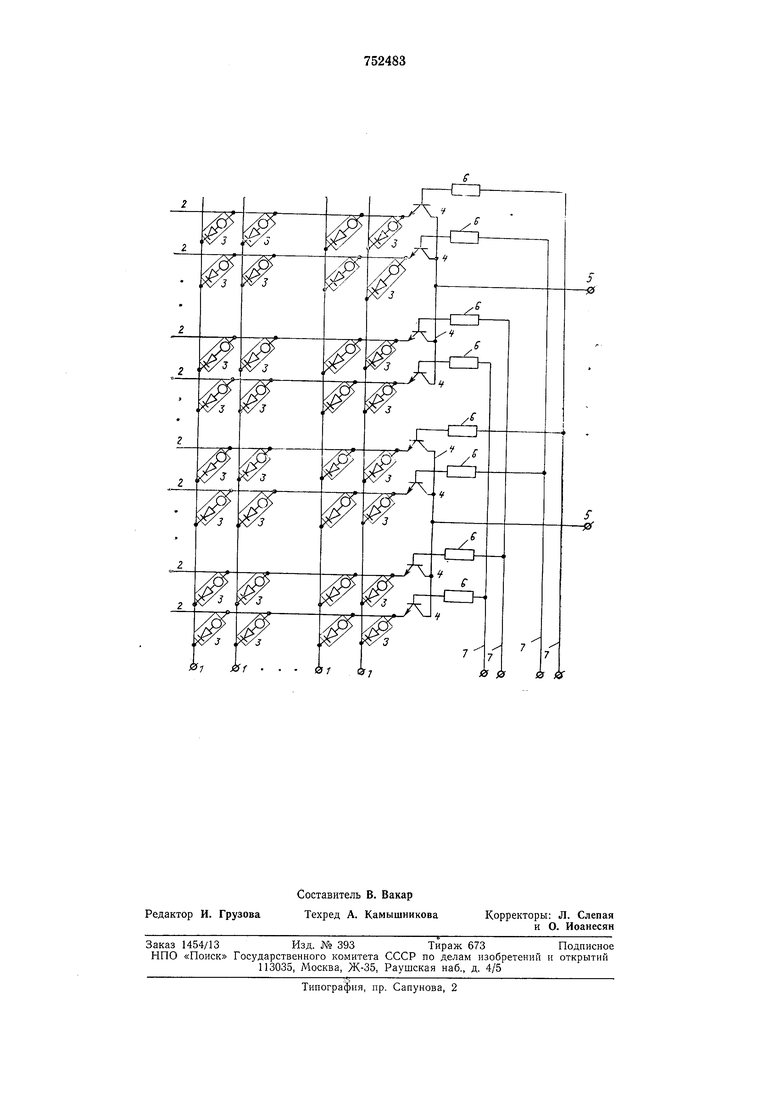

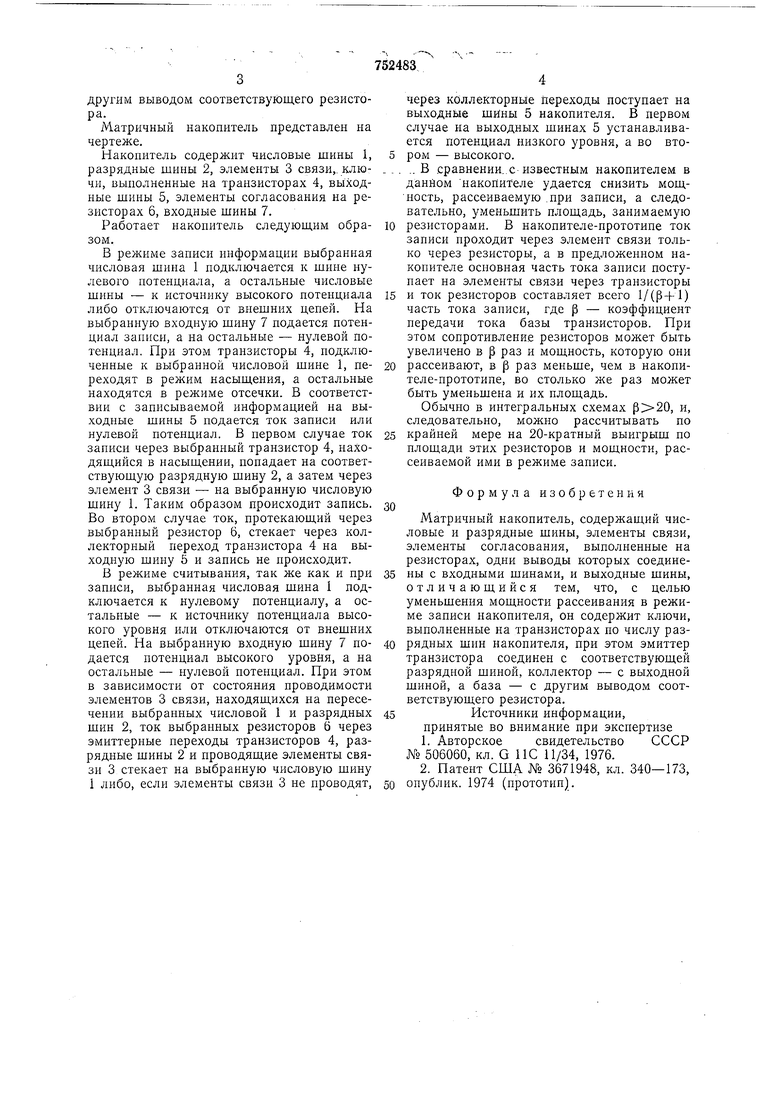

Матричный накопитель представлен на чертеже.

Накопитель содержит числовые шины 1, разрядные шины 2, элементы 3 связи,, ключи, выполненные на транзисторах 4, выходные шины 5, элементы согласования на резисторах 6, входные шины 7.

Работает накоиитель следуюш,им образом.

В записи информации выбранная числовая шина 1 подключается к шипе нулевого потенциала, а остальные числовые шины - к источнику высокого потенциала либо отключаются от внешних цепей. На выбранную входную шину 7 подается потенциал записи, а на остальные - нулевой потенциал. При этом транзисторы 4, иодключенные к выбранной числовой шине 1, переходят в режим насыш,ения, а остальные находятся в режиме отсечки. В соответствии с записываемой информацией на выходные шины 5 подается ток записи или нулевой потенциал. В первом случае ток записи через выбранный транзистор 4, находяш ийся в насыщении, попадает на соответствующую разрядную шину 2, а затем через элемент 3 связи - на выбранную числовую шину 1. Таким образом происходит запись. Во втором случае ток, протекающий через выбранный резистор 6, стекает через коллекторный переход транзистора 4 иа выходную шину 5 и запись не происходит.

В режиме считывания, так же как и при записи, выбранная числовая шина 1 подключается к нулевому потенциалу, а остальные - к источнику потенциала высокого уровня или отключаются от внешних цепей. На выбраиную входную шину 7 подается потенциал высокого уровня, а на остальные - нулевой потепциал. При этом в зависимости от состояния проводимости элементов 3 связи, находяшихся на пересечении выбранных числовой 1 и разрядных шин 2, ток выбранных резисторов и через эмиттерные переходы транзисторов 4, разрядные шины 2 и проводящие элементы связи 3 стекает на выбранную числовую шину 1 либо, если элементы связи 3 не проводят.

через коллекторные переходы поступает на выходные шины 5 накопителя. В первом случае на выходных шинах 5 устанавливается потенциал низкого уровня, а во втором - высокого.

В сравнении, с известным накопителем в

данном накопителе удается снизить мощпость, рассеиваемую .при записи, а следовательно, уменьшить площадь, занимаемую

0 резисторами. В накопителе-прототипе ток записи проходит через элемент связи только через резисторы, а в предложеииом накопителе основная часть тока записи поступает на элементы связи через транзисторы

5 и ток резисторов составляет всего 1/(|3+1) часть тока записи, где р - коэффициент передачи тока базы транзисторов. При этом сопротивление резисторов может быть увеличено в р раз и мощность, которую оии

0 рассеивают, в р раз меньше, чем в накоиителе-прототипе, во столько же раз может быть уменьшена и их площадь.

Обычно в интегральных схемах , и, следовательно, можно рассчитывать по

5 крайней мере на 20-кратный выигрыш по площади этих резисторов и мощности, рассеиваемой ими в режиме заииси.

Формула изобретения

Матричный накопитель, содержащий числовые и разрядные шины, элементы связи, элементы согласования, выполненные на резисторах, одни выводы которых соединены с входными шинами, и выходные шины, отличающийся тем, что, с целью уменьшения мощности рассеивания в режиме записи накопителя, он содержит ключи, выполненные на транзисторах по числу разрядиых шин накопителя, при этом эмиттер транзистора соединен с соответствующей разрядной шипой, коллектор - с выходной шиной, а база - с другим выводом соответствующего резистора.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 506060, кл. G ПС 11/34, 1976.

2.Патент США № 3671948, кл. 340-173, опублик. 1974 (ирототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный накопитель | 1979 |

|

SU799007A1 |

| Матричный накопитель | 1979 |

|

SU773728A1 |

| Постоянное запоминающее устройство | 1978 |

|

SU752482A1 |

| Устройство для записи и считывания информации | 1972 |

|

SU499584A1 |

| Запоминающее устройство | 1976 |

|

SU597006A1 |

| Устройство для формирования разрядных токов записи | 1975 |

|

SU546016A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для записи и считывания | 1973 |

|

SU469989A1 |

| Матричный накопитель | 1986 |

|

SU1343443A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

Авторы

Даты

1980-07-30—Публикация

1978-12-18—Подача