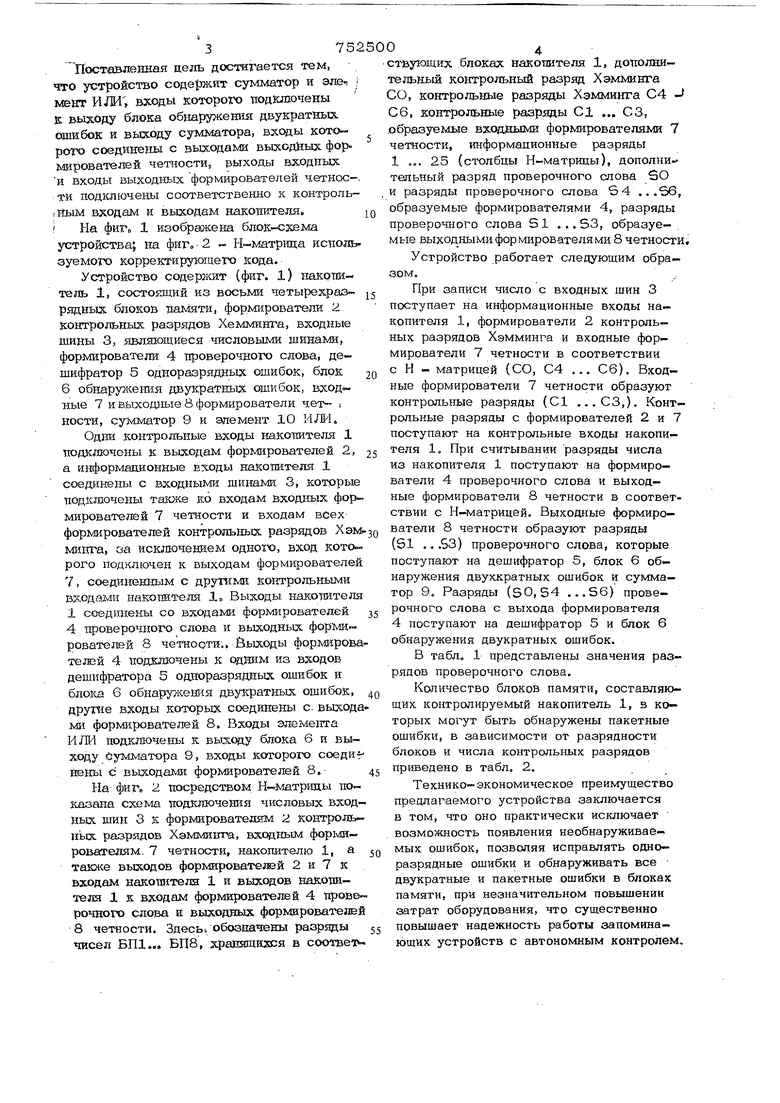

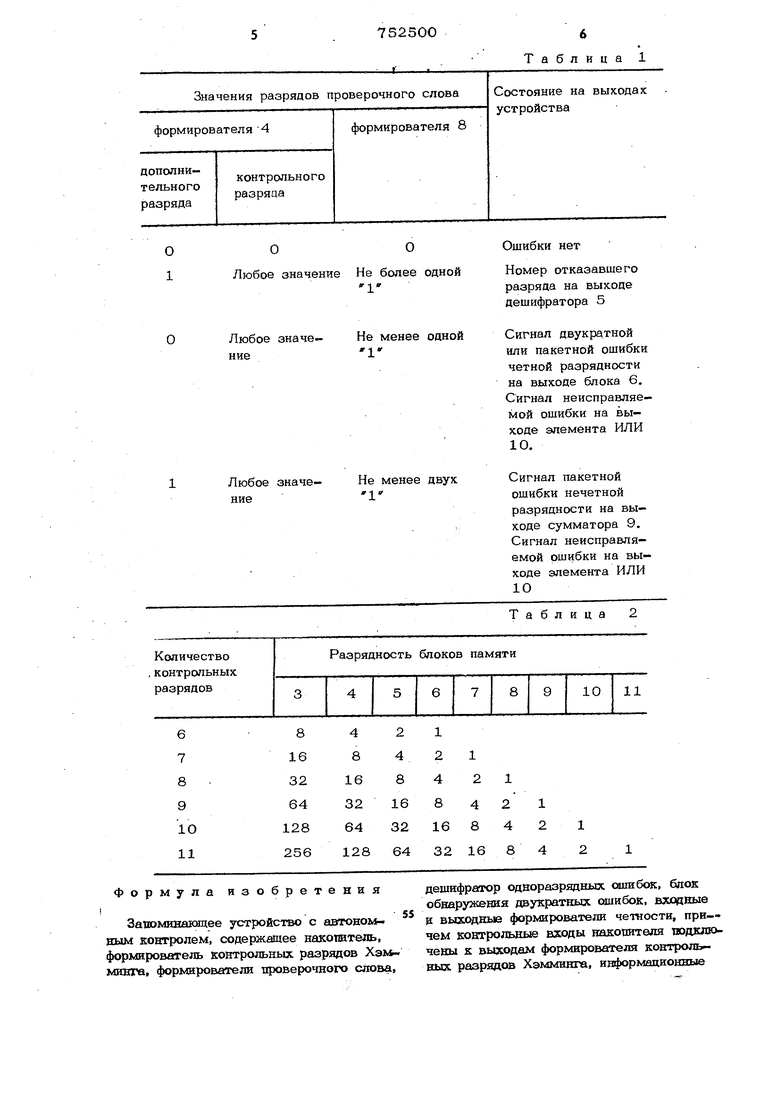

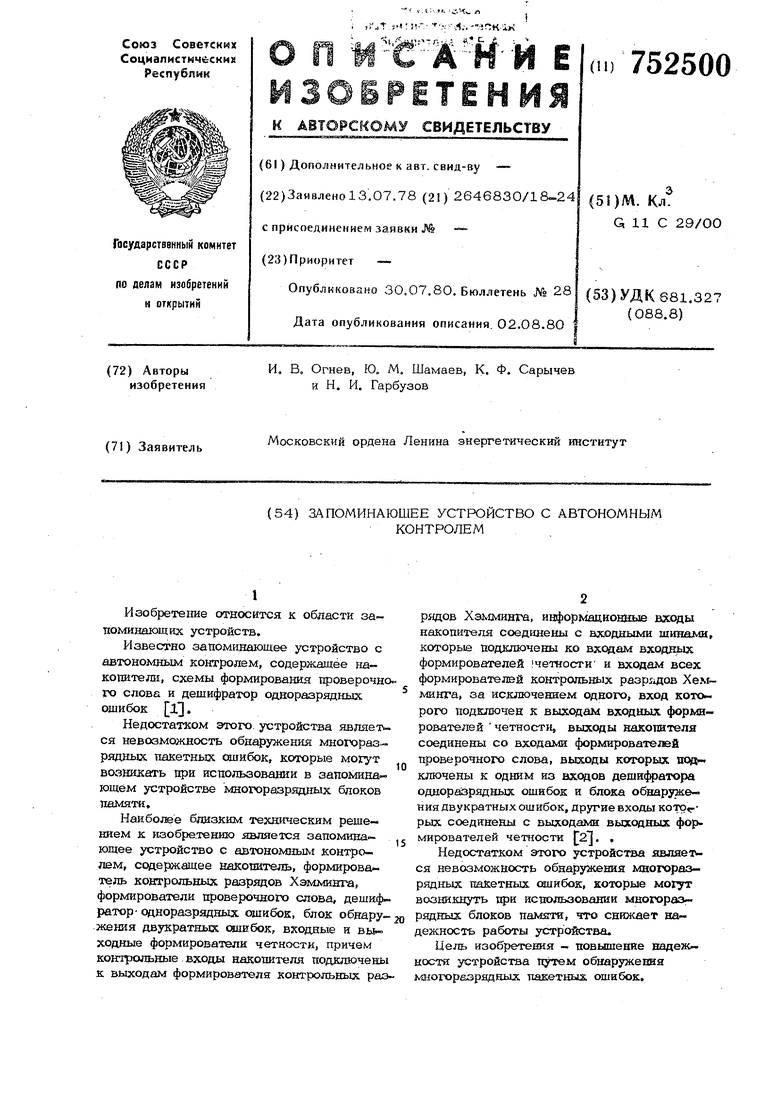

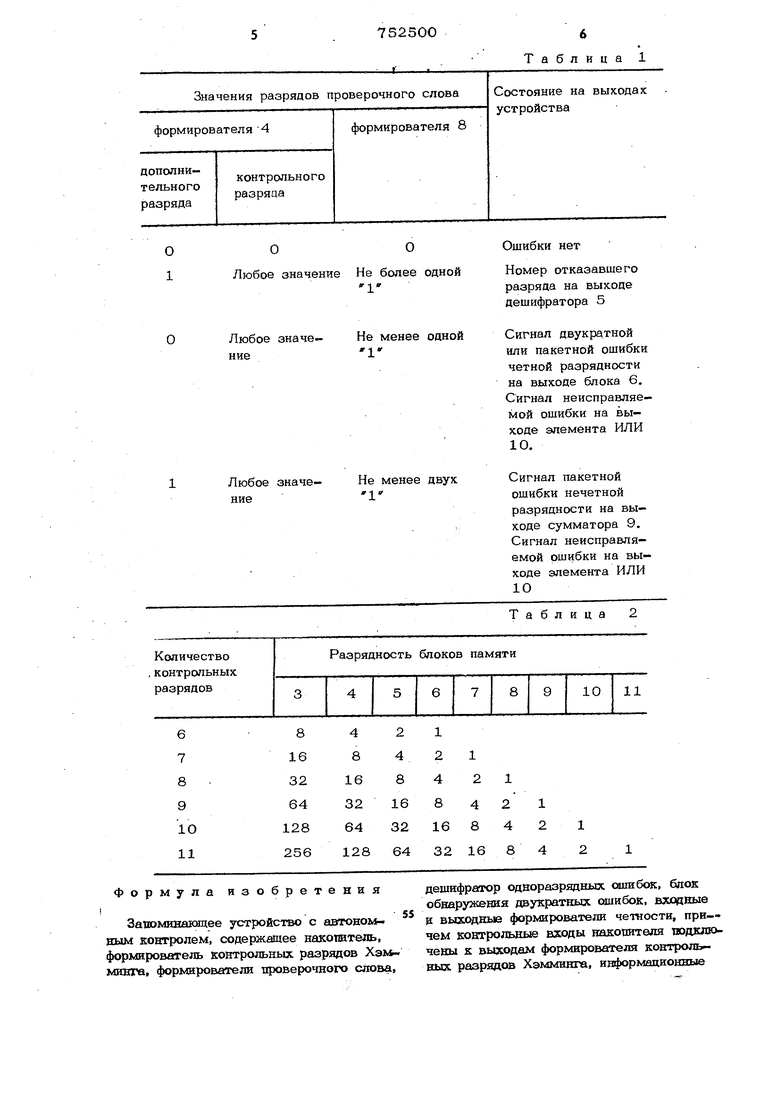

Изобретение относится к области за тюминающих устройств. Известно запоминающее устройство с автономным контролем, содержащее накопители, схемы формирования проверочн го слова и дешифратор одноразрядных ошибок l3« Недостатком этого, устройства являет ся невозможность обнаружения многоразрядных пакетных ошибок, которые могут возникать при использовании в запоминающем устройстве многоразрядных блоков памяти. Наиболее близким техническим решением к изобре.тенкю является запоминающее устройство с автономным контролем, содержащее накопитель, формирователь контрольных разрядов Хэмминт, формирователи проверочного слова, дешиф ратор-одноразрядных ошибок, блок обнару женин двукратных сшибок, входные и вы« ходные формирователи четности, причем контрольные входы накопителя подключены к выходам формирователя контрольных раз рядов Хэмминга, информационные входы накопителя соединены с входными шинами, которые подключены ко входам входных формирователей четности и входам всех. формирователей контрольных Хемминга, за исключением одного, вход которого подключен к выходам входных формирователей четности, выходы накопителя соединены со входами формирователай проверочного слова, выходы которых подключены к одним из входов дешифратора одноразрядных ошибок и блока обнаружения двукратных ошибок, другие входы соединены с выходами выходных формирователей четности 2. . Недостатком этого устройства являет ся невозможность обнаружения многоразрядных пакетных ошибок, которые Moiyr возникнуть при использовании многоразрядных блоков памяти, что снижает надежность работы устройства. Цель изобретения - повышение надежности устройства путем обнаружения многоразрядных пакетных ошибок. Поста&ЛйВНая цель достигается тем, что устройство содержит сумматор и эле мент ИЛИ, входы которого подключены К выходу блока обнаружения двукратных ошибок и выходу сумматора, входы которого соединены с выходами выходных фор. мирователей четности, рыходы входных и входы выходных формирователей четноети подключена соответственно к контроль1Йым входам и выходам накотштеля. I На фиг. 1 изображе блок-схема устройства; на фиг. - 2 - Н-матршоса исполь зуемого корректирующего кода. Устройство содержит {фиг. 1) накотш- тель 1, состоящий из восьми четырехразрядных блоков памяти, формирователи 2 контрольных разрядов Хемминга, входные шины 3, 5шляющиеся числовыми шинами, формирователи 4 Т1роверочного слова, дешифратор 5 одноразрядных ошибок, блок 6 обнарулсення двухкратных ошибок, вход ные 7 и выходные 8 формирователи чет- i ности, сумматор 9 и элемент 1О ИЛИ. Одни контрольные входы накопителя 1 тгодключены к выходам формирователей 2, а инфор1 1ааионные ЕХОДЫ накотштеля 1 соединены с входными шинами 3, которые подключены тшсже ко входам ВХОДЕ ЫХ формирователей 7 четности и входам всех формирователей контрольных разрядов Хэм минга, за исключением одного, вход которого подключен к выходам формирователей 7, соединенным с другими контрольными входш ги накопителя I, Выходы, накотштеля 1 соединены со входами формирователей 4 тфоверочного слова и выходных форгушроватепей 8 четности,. Выходы формарова телЕй 4 подключены к одним из входов дешифратора 5 одноразрядных ошибок и бло1са 6 обнару 1сения двукратных ошибок, другие входы которых соединены с. выхода ми формирователей 8. Входы элемента ИЛИ подключены к выходу блока 6 и выходу йумматора 9, входы которого соедит Нены с выходами формирователей 8,На фиГо 2 посредством Н матриды по казана схема тюдключения числовых вход ных шин 3 к формирователям 2 контроль- нЬк разрядов Хэмминга, входным фор1ин рователям. 7 четности, накопителю 1, а такисе выходов формирователей 2 и 7 к входам накопителя 1 и выходов накотштеля 1 к входам формирователей 4 TipoBe рочного слова а выходных формирователей 8 четности. Здесьь обозначены разряды чисел БП1.« БП8, храЕхшигся в соотвеч ствующих блоках накотштеля 1, дополнительный контрольный разряд Хэмминга СО, контрольные разряды Хэмминга С4 - С6, контрольные разрады С1 ... СЗ, .образуемые входными формирователями 7 четности, информационные разряды 1 ,,. 25 ( Н-матрины), дополнительный разряд проверочного слова SO и разряды проверочного слова S4 ...Зб, образуемые формирователями 4, разряды нроверочного слова S1 ...53, обраауе мые выходными формирователя ми 8 четности; Устройство работает следующим образом. При записи число с входных шин 3 поступает на информационные входы накопителя 1, формирователи 2 контрольных разрядов Хэмминга и входные формирователи 7 четности в соответствии с Н - матрицей (СО, С4 ,,, С6). Входные формирователи 7 четности образуют контрольные разряды (С1 ...СЗ,). Контрольные разряды с формирователей 2 и 7 поступают на контрольные входы накопителя 1о При считывании разряды числа из накопителя 1 поступают на формирователи 4 проверочного слова и выходные формирователи 8 четности в соответствии с Н-матрицей. Выходные формиро и четности образуют разряды (61 ...53) проверочного слова, которые поступают на дешифратор 5, блок 6 обнаружения двухкратных ошибок и сумматор 9. Разряды (SO, 54 ...S6) проверочного слова с выхода формирователя 4 поступают на дешифратор 5 и блок б обнаружения двукратных ошибок. В табл. 1 представлены значения разрядов проверочного слова. Количество блоков памяти, составляющих контролируемый накопитель 1, в которых могут быть обнаружены пакетные ошибки, в зависимости от разрядности блоков и числа контрольных разрядов приведено в табл. 2. Технико- экономическое преимущество предлагаемого устройства заключается в том, что оно практически исключает возможность появления необнаруживаемых ошибок, позволяя исправлять одноразрядные ошибки и обнаруживать все двукратные и пакетные ошибки в блоках памяти, при незначительном повышении затрат оборудования, что существенно повышает надежность работы запоминающих устройств с автономным контролем. Значения разрядов проверочного слова формирователя 4

контрольного разряаа Л н Л н формирователя 8

Таблица Таблица 1 Состояние на выходах устройства Ошибки нет Номер отказавшего разряда на выходе дешифратора 5 Сигнал двукратной или пакетной ошибки четной разрядности на выходе блока 6. Сигнал неисправляе- мой ошибки на выходе элемента ИЛИ 10. Сигнал пакетной ошибки нечетной разрядности на выходе сумматора 9. Сигнал неисправля- емой ошибки на выходе элемента ИЛИ 10

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с авто-НОМНыМ КОНТРОлЕМ | 1979 |

|

SU809403A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU881877A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU888203A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1115107A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

Формула изобретения

Запоминающее устройство с автономным контролем, содержашее накопнтель, формирователь контрольных разрядов Хэкьмннга, формирователи проверочного слова,

дешифраячзр одноразрядных сшибок, блок обнаружения двукратных ошибок, входные в выходные формирователи четаости, причем контрольные входы накотштеля подключены к выходам формирователя контрольных разрядов Хэкоганга, информационные

входы накопителн соедивевы с входными ., soTOpbte водЕлючевы о входам входных формирователей четности и входам ВО8Х формнроватепэй контрольных разрядов Хэмминга, за нсключешем одного, вход которого подключен К выходам входных формирователей четности, выходы накойителя соединены со входами формирователей проверочного слова, выходы которых подключены к одним из входов дешифратора одноразрядных-сяиибок и блока обнаружения двукратных ошибок, другие входы которых соединены с выходами выходных формирователей четности, : отличающееся тем, что, с целью повышения надежности устройства, оно содержит

сумматор и элемент ИЛИ, входы которого подключены к выходу блока обн ужения двукратных ошибок и выходу сумматора, входы которого соединены с выходами выходных формирователей четности, выходы: входЕсых и входы выходных формирователей четности подключены соответственно к контрольным входам и выходам накопителя.

Источники информации, принятые во внимание при экспертизе

Sat вт йпл $л«

Cfcfttftct M Cf4 f f f i e iotifinn, ts

6nS 6nS

snf set

Авторы

Даты

1980-07-30—Публикация

1978-07-13—Подача