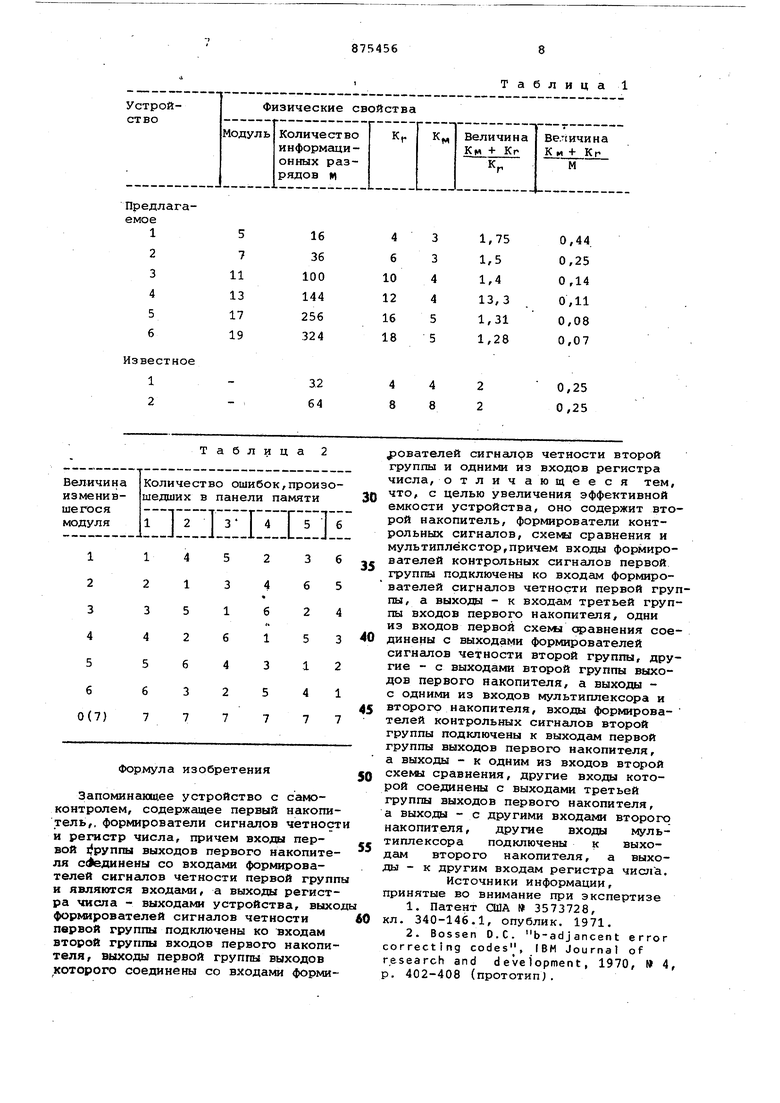

Изобретение относится к запоминаю цим устройствам. Известно устройство , содержащее панели памяти, формирователи контрол ,ных разрядов кода Хэмминга, формирователи проверочного слова, дешифратор одноразрядных ошибок, схему обна ружения двухразрядных ошибок 13 . Недостатком этого -устройства явля ется невозможность устранения пакетных ошибок. Наиболее близким техническим решением к данному изобретению являетс запоминающее устройство с самоконтро лем, содержащее многоразрядные панел памяти, cxeNiy обнаружения отказавшей панели памяти, схему обнаружения отказавших разрядов в панели памяти и позволяющее исправлять 4-х разрядные пакеты ошибок с помощью 8-ми контрол ных разрядов в 32 информационных раз рядах (или 8-ми разрядных ошибок с помощью 16 контрольных разрядов при 64 информационных разрядах) 2 . Недостатком зтого устройства является низкая зффективная емкость вследствие избыточности в контрольных разрядах, приходящихся на один исправляемой разряд с ошибкой, а также высокой избыточности в проверочных разрядах по отношению к количеству ийформгщионных разрядов. Цель изобретения - увеличение зффективной емкости устройства. Поставленная цель достигается тем, что в запоминающее устройство с самоконтролем, содержащее первый накопитель, формирователи сигналов четкости и регистр числа, причем входы первой группы входов первого накопителя соединены со входами формирователей сигналов четности первой группы и являются входами, а выходы регистра числа - выходами устройства, выходы формирователей сигналов четности первой группы подключены ко входам второй группы входов первого накопителя, выходы первой группы выходов которого соединены со входги ш формирователей сигналов четности второй группы и одними из входов регистра числа, введены второй накопитель,формирователи контрольных сигнгшов, схекы сравнения и мультиплексор, причем входы формирователей контрольных сигналов первой группы подключены ко входам формирователей сигналов четности первой группы, а выходы - к входам третьей группы входов первого накопителя. один из входов .первой группы сравнения соединены с выходами формирователей сигналов четности второй группы, другие - с выходами второй группы выходов первого, накопителя, а выходл - с одними из входов мультиплек сора и второго накопителя, входы фор мирователей контрольных сигналов вто рой группы подключены к выходам первой группы выходов первого накопи теля, а выходы - к одним из входов в рой схемы сравнения, другие входы ко торой соединены с выходами третьей группы выходов первого накопителя, а выходы - с другими входами второго накопителя, другие входы мультиплексора подключены к выходам второго накопителя, а выходы - к другим входам регистра числа. На чертеже изображена функциональ ная схэма предлагаемого устройства. Устройство содержит первый 1 и вт рой 2 накопители, являющийся накопителем постоянного типа, первую групп формирователей 3 сигналов четности, первую группу формирователей 4 контрольных сигналов, мультиплексор 5, регистр б числа, вторую группу форми рователей 7 сигналов четности, вторую группу формирователей 8 контроль еых сигналов, первую 9 и йтррую 10 cxeMJ сравнения. Входы первой группы входов первог накопителя -1 соединены со входами формирователей 3 сигналов четности первой группы и являются входами, а выходы регистра числа 6 - выхода устройства. Выходы формирователей 3 сигналов четности первой группы подключены ко входам второй группы вход первого накопителя 1, первая группа выходов которого соединена со входам формирователей 7 сигналов четности второй группы .и одними из входов рег стра б числа. Входы формирователей 4 контрольных сигналов первой группы подключены ко входам формирователей 3 сигналов четности первой группы, а выходы - к выходам третьей группы выходов первого накопителя 1. Одни из входов первой cxeNH 9 сравнения соединены с выходами формирователей 7 сигналов четности второй группы, другие - с выходами второй группы выходов первого накопителя 1, а выходы - с одними из входов мультиплек сора 5 и второго накопителя 2 .Входы формирователей 8 контрольных сигналбв« второй группы подключены к выходам первой группы выходов первого накопителя 1, а выходы - к одним иэ входов второй схемы 10 сравнения, другие входы которой соединены с выходами третьей группы выходов первого накопителя 1, а выходы - с другими входами второго накопителя входы мультиплексора 5 подключены к выходам второго накопителя 2, а выходы - к дру;им входам регистра 6 числа. Первый накопитель 1 выполнен из многоразрядных панелях памяти. Формирователи контрольных сигналов первой 4 и второй В групп явлй1бтся формирователями сигналов по нечетному модулю. Устройство работает следующим образом. На входы устройства в очередном цикле записи поступают двоичные коды чисел, которые записываются в информационные разряды первого накопителя 1 непосредственно через входы первой группы входов, а в контрольные разряды первого накопителя 1 записываются коды чисел соответственно с выходов формирователей 3 сигналов четности первой группы и с выходов формирователей 4 контрольных сигналов первой группы (по нечетному модулю). Если А - нечетный выбранный модуль, то выбираемая разрядность панели памяти первого накопителя 1 равна (А-1)-разрядов, количество формирователей сигналов четности первой 3 и второй 7 групп также равно А-1 и количество контрольных разрядов для записи контрольных сигналов четности в первом накопителе 1 равно К А-1. При этом первый формирователь 3 сигналов четности первой группы вырабатывает признак четности для всех первых разрядов всех панелей первого накопителя 1 и записывает его в первый контрольный разряд. Второй формирователь 3 сигналов четности первой хруппы вырабатывает признак четности для всех вторых разрядов всех панелей памяти первого накопителя 1 и записывает его во второй контрольный разряд. И так далее. Формирователь 3 сигналов четности первой группы вырабатывает признак четности дпя всех (A-l)-x разрядов со всех панелей памяти и записывает его в (А-1) контрольный разряд первого накопителя 1. Для выбранного модуля А количество контрольных разрядов, вырабатываемых формирователями контрольных сигналов первой группы 4 определяется из выражения Кц 1 + tlog А , где log А целая часть числа. Количество панелей памяти первого накопителя с разрядностью (А-1) для выбранного модуля А определяется величиной модуля А, и ПРИ этом одна панель памяти первого накопителя 1 отводится для записи контрольных разрядов по четности. Общая информационная разрядность числа для выбранного модуля А может быть не более величины М (Л-1)(А-1). В табл. 1 приведены различные харак.теристики, которые позволяют выбрать нужный юдyль для коррекции ошибок.

Таким образом, при выбранном нечетном модуле Л можно иметь панели памяти в первом накопителе 1 с разрядностью (А-1).

Выработка М, контрольных разрядов производится следукхцим образом,

Всем 1А-1) разрядам с первой панели памяти первого накопителя 1 придается вес 1. Всем (А-1)-разрядам со второй панели памяти придается вес 2. Всем (А-1)-разрядам с третьей панели памяти придается вес 3 и так далее, всем (А-1) разрядам с А-1 панели памяти придается вес А. Указанные разряды в соответствии с присвоенными номерами (весами) поступают на формирователь 4 контрольных сигналов. Известно, что формирователи по нет1етному модулю имеют входы -с весами 1,2,4... т.е. равными степени двойки. Поэтому, для того, чтоб иметь вес не равный степени двойки, необходимо разряды с такими весами подать одновременно на несколько входов с различными весами формирователей 4 контрольных сигнашо по нечетному модулю 4. Это позволяет закодировать все А-панелей памяти первого накопителя 1.

При считывании работа устройства происходит следующим образом.

Информационные разряды из панелей памяти первого накопителя 1 поступают в выходной регистр Б числа, на входы формирователей 7 сигналов четности второй группы, входы формирователей контрольных 8 сигналов второй группы. В формирователях 7 .сигналов четности второй группы производится клработка (А-1)-признака четиости по аналогичному,описанного выше, алгоритму. Полученные признаки четиости поступают на входы первой группы первой схемы 9 сравнения, на входы второй группы которой по ступают Кф контрольных разрядов из первого накопителя 1. Первая схема 9 сравнения сравнивает коды и вырабатывает признак нестравнения для тех из (А-1)-разрядов первого накопителя 1, в которых произошла ошибка, если таковая имеется. Таким обр1азом, в группе из (А-1)-ра,зрядов мл узиаем номера отказавших разрядов первого накопителя 1

Для исправления необходимо знать еще и номер отказавшей панели памяти первого накопителя 1. Этот номер находится следующим образом.

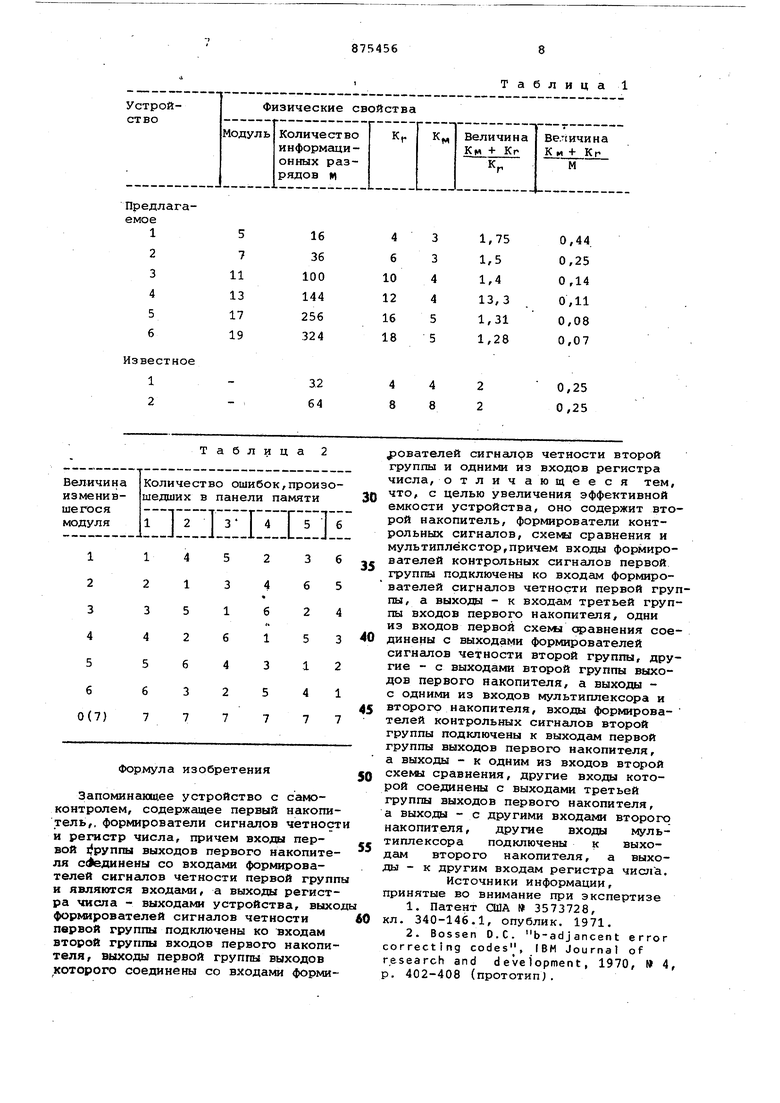

По алгоритму, аналогичному для выработки Кщ контрольных разрядов с помощью формирователей 4 контрольных сигналов первой группы (по нечетному модулю), формирователями 8 контрольных сигналов второй группы .производится выборка К контрольных разрядов из информационных и К4 контрольных разрядов. Полученные К,« конт0рольных разрядов поступают на одни из входов второй схемл-10 сравнения, на другие входы которой поступают контрольные К„ разрядов из первого накопителя 1. Вторая схема 10 срав5нения позволяет определить, на сколько изменился модуль, если произошла ошибка в панелях памяти первого накопителя 1. На одном или нескольких выходах второй схемы 10 сравнения по0явятся признаки несравнения, соответствующие произошедней ошибке. Выходы первой 9 и второй 10 .схем сравнения поступают на соответствующие входы второго накопителя 2, где и вырабатывается номер отказавшей панели па5мяти первого накопителя 1. Это происходит следующим образом. Возьмем для определенности величину модуля А-7. Для понимания принципа определения номера отказавшей панелк памяти

0 составляется таблица 2 однозначного соответствия между количеством отказавших разрядов в панели памяти, величиной изменившегося из-за отказа модуля и кодом номера отказавшей панели

5 памяти первого накопителя 1.

Аналогичные таблицы нетрудно построить и для других модулей А. Данная таблица зашивается во второй накопитель 2 (постоянного типа), на вы0ходе KOTOpoixD будем иметь двоичный код номера-отказавшей панели памяти первого накопителя 1. v

Затем с помощью мультиплексора 5 и регистра 6 числа производится исправление кода числа, соответствую- .

5 щего разрядам отказавшей панели памя ти накопителя 1.

Технико-экономическое преимущество предлагаемого устройства заключается в уменьшении количества конт0рольных разрядов, приходящихся на один разряд ошибки при одновременном увеличении количества информационных разрядов накопителя,за счет чего увеличена эффективная емкость устройства.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-14—Подача