(54) ЗАПОМИНАКХЦЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1978 |

|

SU752500A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU881877A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1115107A1 |

| Постоянное запоминающее устройствоС АВТОНОМНыМ КОНТРОлЕМ | 1979 |

|

SU832604A1 |

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с автономным контролем, содержащее накопители, схемы формирования контрольных разрядов, схемы формирования проверочного слова, дешифратор одноразрядных ошибок и схему обнаружения двухразрядных пакетных ошибок in.

Недостатком этого устройства является невозможность обнаружения многоразрядных ошибок.

Наиболее близким к предлагаемому является запоминающее устройство с. автономным контролем, содержащее накопители, формирователь контрольных разрядов кода Хэмминга, формирователи проверочного слова, дешифратор одноразрядных ошибок, блок обнаружения двухкратных ошибок, входные и выходные формирователи четности, сумматор и элемент ИЛИ. Информационные входы накопителей соединены с входными, а выходы - с выходными шинами, одни входы формирователей контрольных разрядов кода Хэмминга подключены к входным шинам, другие входы - к выходам входных формирователей четности и к одним

контрольным входам, а выходы - к другим контрольным входам накопителей, входы формирователей проверочного слова соединены с выходами накопителей, а выходы - с одними входами дешифратора одноразрядных ошибок и схемы обнаружения двухкратных ошибок,другие входы которых подключены к выходам выходных формирова0телей четности, входы сумматора соединены с выходами первой группы вь ходных формирователей четности, один из входов элемента ИЛИ подключен к выходу схемы обнаружения 5 двойных ошибок 2.

К недостаткам известного устройства следует отнести большое число контрольных разрядов при обнаружении многоразрядных пакетных оши1бок , которые могут возникнуть при использовании многоразрядных блоков памяти с разрядностью - 1, где г - число контрольных разрядов, необходимых для исправления одно5разрядных ошибок.

Цель изобретения - упрощение устройства за счет уменьшения числа контрольных разрядов накопителя.

Поставленная цель достигается тем, что в запоминающее устройство

0

с автономным контролем, содержащее накопитель, информационные входы и выходы которого являются информационными входами и выходами устройства, первый формирователь, выходы которого подключены к первым входам накопителя, а первые входы - к информационным входам устройства, второй формирователь, входы которого

подключены к информационным входам устройства, а выходы-ко вторым входам первого формирователя и ко вторым входам накопителя, третий формирователь, входы которого подключены к первым выходам накопителя а выходы - к первым входам дешифратора, четвертый формирователь, входы которого подключены ко вторым выходам накопителя, а выходы - ко вторым входам дешифратора и ко входам первого сумматора, блок контроля, первые входы которого подключены к выходам третьего формирователя вторые входы - к выходам четвертого формирователя, а выход блока контроля подключен к первому входу элемента ИЛИ, введены второй сумматор, входы которого подключены к выходам четвертого формирователя, и элемент И, первый и второй входы которого подключены соответственно к выходам первого и второго су1 1маторов, а его выход подключен ко второму входу элемента ИЛИ.

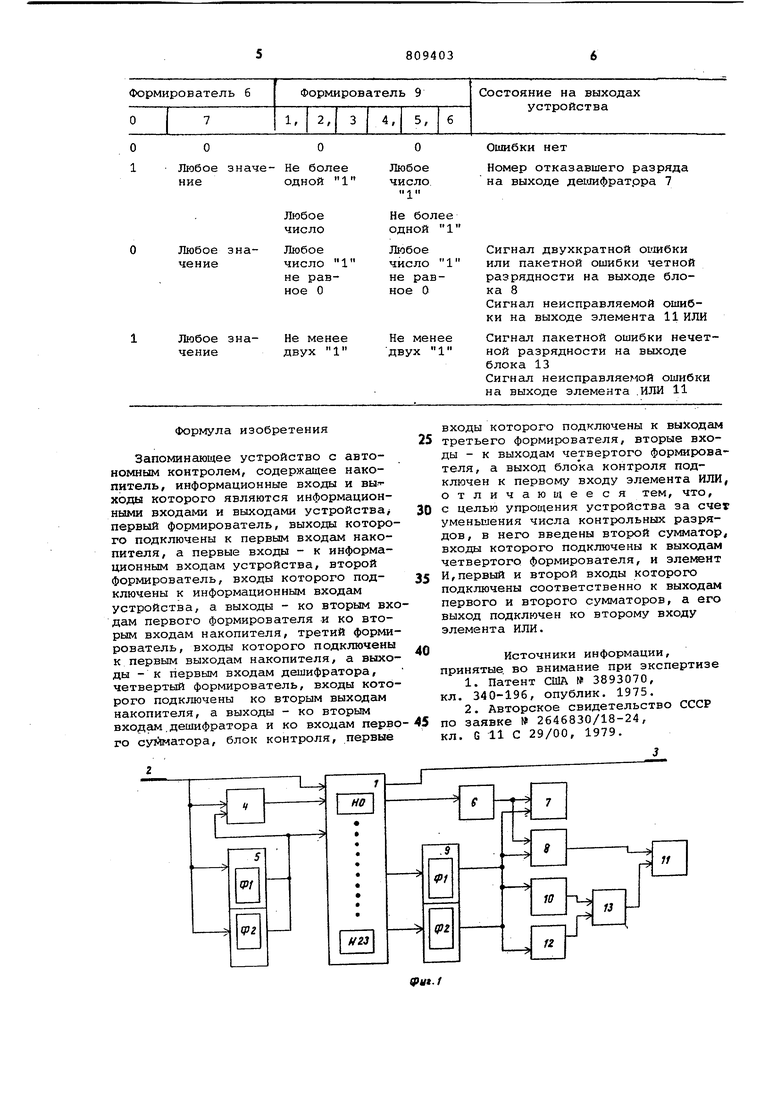

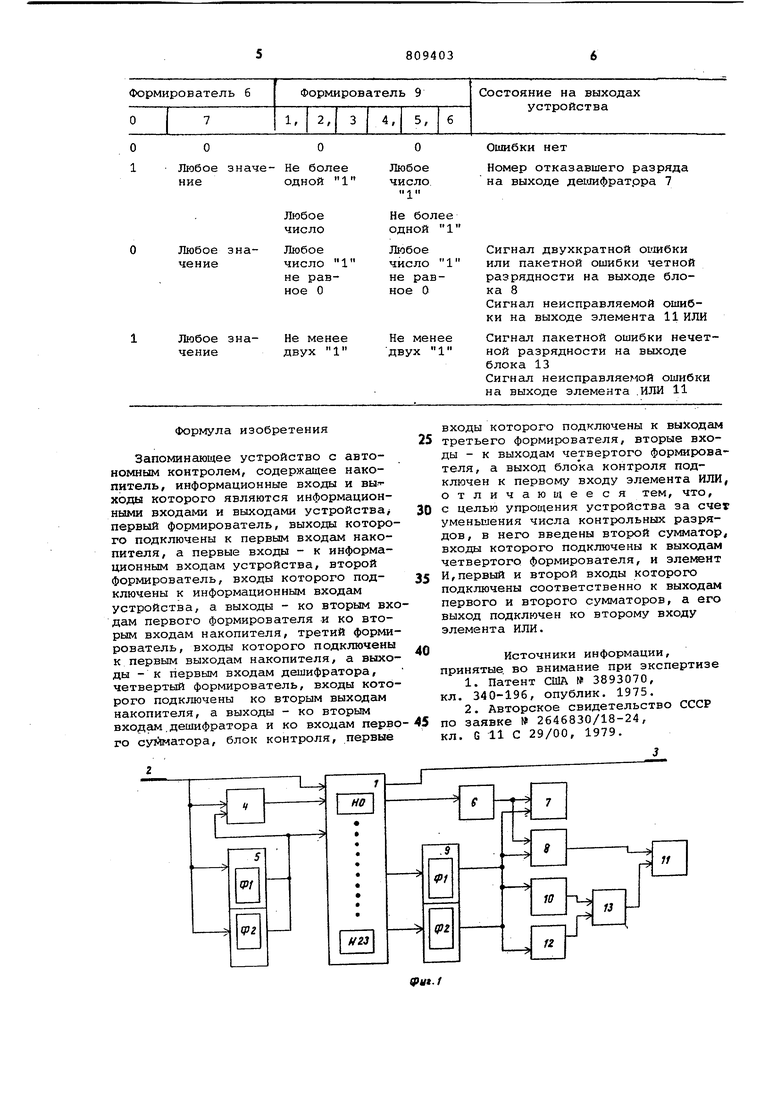

На фиг. 1 изображена схема устроства; на фиг. 2 - Н-матрица используемого корректирую1пего кода.

Устройство содержит накопитель 1, в данном случае состоящий из 24-х 4-х разрядных блоков памяти, входные и выходные шины 2 и 3 соответственно, первый формирователь 4, второй формирователь 5, третий формирователь 6, дешифратор 7, блок 8 контроля, четвертый формирователь 9, первый сумматор 10, элемент 11 ИЛИ, второй cy Iмaтop 12, элемент 13 И.

Схема подключения числовых входных шин 2 к первому формирователю 4 контрольных разрядов кода Хэмминга, ко вторым формирователям 5 четности, а также выходов формирователей 4 и 5 к входам накопителя 1 и выходов накопителя 1 к входам третьего 6 и четвертого 9 формирователей показана посредством Н-матрицы кода (фиг. 2). Цифрами 1,..88 обознчены информациннные разряды числа СО, С7, разряды кода Хэмминга, . С1 ... Сб.- контрольные разряды,

образуемые формирователями четности, О, 7 - разряды проверочного слова, образуемые формирователем 6 проверочного слова, 1 - 6 - разряды проверочного слова, образуемые выходными формирователями 9 чет5 нрсти.

Устройство работает следующим образом.

При записи число с входных шин 0 2 поступает на информационные входы накопителя 1, на входы первого формирователя 4, формирующего контрольные разряды Хэмминга, и на входы второго формирователя 5, формирующего разряда четности. Формирование контрольных разрядов происходит в соответствии с Н-матрицей (фиг. 2)

Контрольные разряды с формирователей 4 и 5 поступают на контрольные входы накопителей 1. при считывании разряды числа из накопителей 1 поступают на третий формирователь б, формирующий проверочное слово, и на четвертый формирователь 9, формирующий выходные разряды четности. Формирование происходит в соответствии с Н-матридей (фиг. 2). Формирователь б проверочного слова и выходные формирователи 9 четности

Q образуют разряды 0-6 проверочного слова, которые поступают на дешифратор 7, блок 8 контроля, обнаруживающий двухкратные ошибки, первый и второй сумматоры 10 и 12.

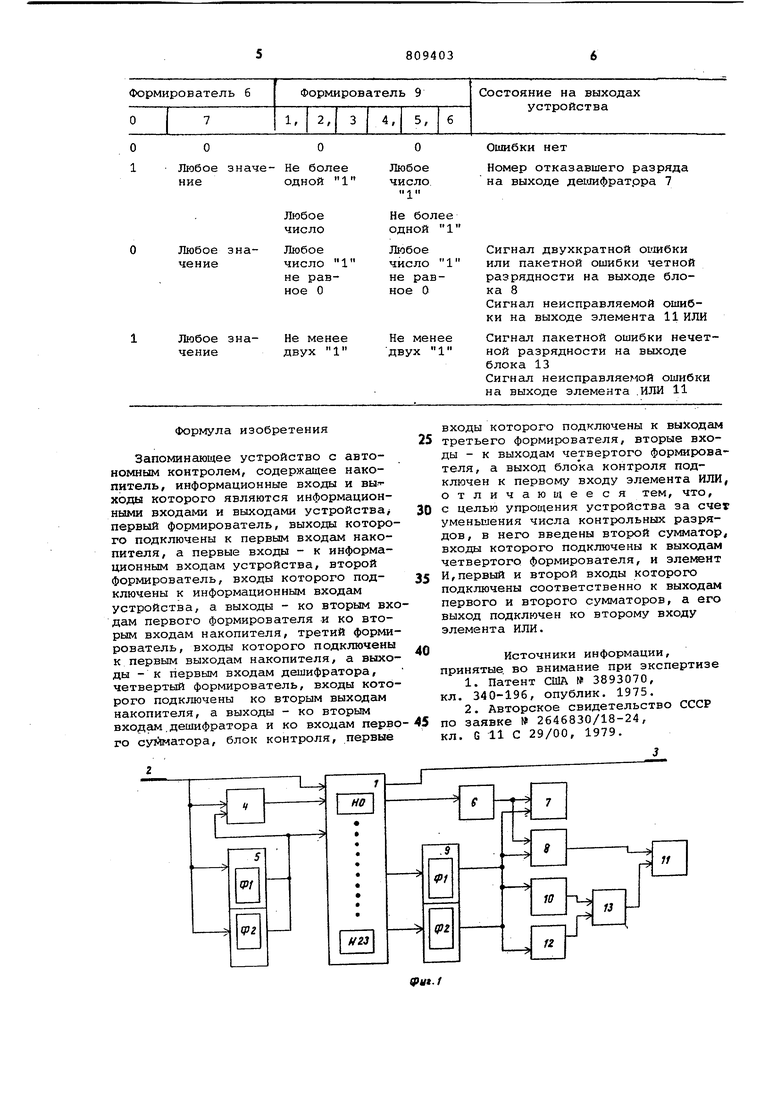

г Разряд О проверочного слова с выхода формирователя 6 поступает на дешифратор 7, а разряды О, 7 - на блок 8 контроля. В зависимости от значения разрядов проверочного слова возможны следующие случаи (таблица 1).

Преимущество предлагаемого устройства заключается в том, что оно позволяет уменьшить число контрольных разрядов по сравнению с известным.В ЗУ,

5 разрядность которого кратна четному числу байтов .(В, 16, 32, 64, 128....), предлагаемое изобретение позволяет при минимально возможном количестве контрольных разрядов, равном

Q количеству контрольных разрядов Хэмминга, обнаруживать пакетные ошибки разрядностью до 4 для 32, 64 и 128 разрядных слов и т.д.,в то время, как известное устройство требует для обнаружения пакетных ошибок с разрядностью 4 для 32, 64, 128 разрядных слов введения одного дополнительного контрольного разряда.

Любое число

знаЛюбоечисло не равное О

Любое знаНе менее двух 1 чение Формула изобретения Запоминающее устройство с автономным контролем, содержащее накопитель, информационные входы и вы ходы которого являются информационными входами и выходами устройства первый формирователь, выходы которого подключены к первым входам накопителя, а первые входы - к информационным входам устройства, второй формирователь, входы которого подключены к информационным входаи устройства, а выходы - ко вторым вхо дам первого формирователя и ко вторым входам накопителя, третий формирователь, входы которого подключены к первым выходам накопителя, а выходы - к первым входам дешифратора, четвертый формирователь, входы которого подключены ко вторым выходам накопителя, а выходы - ко вторым входам,дешифратора и ко входам перво го сут 1матора, блок контроля, первые

на выходе дешифратрра 7

Сигнал двухкратной оишбки или пакетной ошибки четной разрядности на выходе блока 8

Сигнал неисправляемой ошибки на выходе элемента 11 ИЛИ

Сигнал пакетной ошибки нечетной разрядности на выходе блока 13

Сигнал неисправляемой ошибки на выходе элемента .ИЛИ 11 входы которого подключены к выходам третьего формирователя, вторые входы - к выходам четвертого формирователя, а выход блока контроля подключен к первому входу элемента ИЛИ, отличающееся тем, что, с целью упрощения устройства за счет уменьшения числа контрольных разрядов , в него введены второй сумматор, входы которого подключены к выходам четвертого формирователя, и элемент И,первый и второй входы которого подключены соответственно к выходам первого и второго сумматоров, а его выход подключен ко второму входу элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3893070, кл. 340-196, опублик. 1975. 2.Авторское свидетельство СССР по заявке № 2646830/18-24, кл. G 11 С 29/00, 1979.

t .i-r r-es

Авторы

Даты

1981-02-28—Публикация

1979-06-14—Подача