1 Изобретение относится к вычислительной технике, в частности к запо минающим устройствам. Известны запоминающие устройства с самоконтролем .1 и 2 . Одно из известных устройств содержит блоки памяти, формирователи контрольных разрядов Хемминга, форм рователи проверочного слова, дешифр тор одноразрядных ошибок, схему обнаружения двухразрядных и пакетных ошибок СП . Недостатком этого устройства является невозможность устранения пакетньк ошибок. Наиболее близким техническим решением к предлагаемому является запоминающее устройство с автономным контролем, содержащее многоразрядны блоки памяти, первый и второй форми рователи четности, первый и второй формирователи проверочног о слова, первый блок элементов И, сумматорумножитель, второй блок элементов И мультиплексор и блок коррекции пакетных ошибок, причем входы первого и второго формирователей четности соединены с информационными входами устройства, а выходы с контрольными входами блоков памяти, входы первог и второго формирователей проверочного слова соединены с информационными и контрольными выходами блоков памяти, а выходы - с входами первог блока элементов И и выходами сумматора-умножителя, входы второго блок элементов И соединены с выходами су матора-умножителя, а выходы - с одними входами мультиплексора, другие входы которого соединены выходами первого формирователя проверочного слова, к одним входам блока коррекции пакетных ошибок подключены информационные выходы блоков памяти, а к другим - выходы мультиплексора 121. Недостатком известного устройств является невозможность обнаружения двойных пакетов ошибок, т.е. пакетов ошибок, возникающих одновременн в двух блоках памяти или в двух мно горазрядных микросхемах памяти, что снижает надежность устройства. Цель изобретения - повышение надежности устройства путем одновременного обнаружения ошибок в нескол ких блоках памяти. 72 Поставленная цель достигается тем, что в запоминающее устройство с автономным контролем, содержащее блоки памяти, первый и второй формирователи сигналов четности, выходы которых подключены к контрольным входам блоков памяти, информационные входы которых и входы формирователей сигналов четности объединены и являются входами устройства, блок коррекции пакетных ошибок, выходы которого являются информационными выходами устройства, 1-1ультиплексор, умножитель, группу элементов И, первый элемент И и формирователи сигналов контрольного слова, входы которых подключены соответственно к информационным и контрольным выходам блоков памяти, причем выходы первого формирователя сигналов контрольного слова соединены с одним из входов элементов И группы, умножителя и мультиплексора, другие входы которого соединены с выходом первого элемента И, входы которого подключены к выходам умножителя, другие входы которого и другие входы элементов И грруппы соединены с выходами второго формирователя сигналов контрольного слова, входы блока коррекции пакетных ошибок подключены соответственно к вьгходам мультиплексора и к информационным выходам блоков памяти, введены логический блок и элемент ИЛИНЕ, выход которого подключен к одному из входов логического блока, один из входов соединены с выходами элементов И группы, а другие входы с выходами мультиплексора, другие входы логического блока подключены к выходам формирователей сигналов контрольного слова, а выход является контрольным выходом устройства. Кроме того, логический блок содержит элемент ИЛИ и второй элемент И, nepBijrii вход которого является одним из входов блока, а второй вход подключен к выходу элемента ИЛИ, входы которого являются другими входами блока, выходом которого является выход второго элемента И. На фиг. 1 предоставлена функциональная схема устройства; на фиг.2 функциональные схемы логического блока и элемента ИЛИ-НЕ; на фиг. 3 функциональные схемы части умножителя, части мультиплексора и части блока коррекции пакетных ошибок;

311 1 S

а фиг. 4 - и -матрица исполь:)уемого

орректирующего кода.

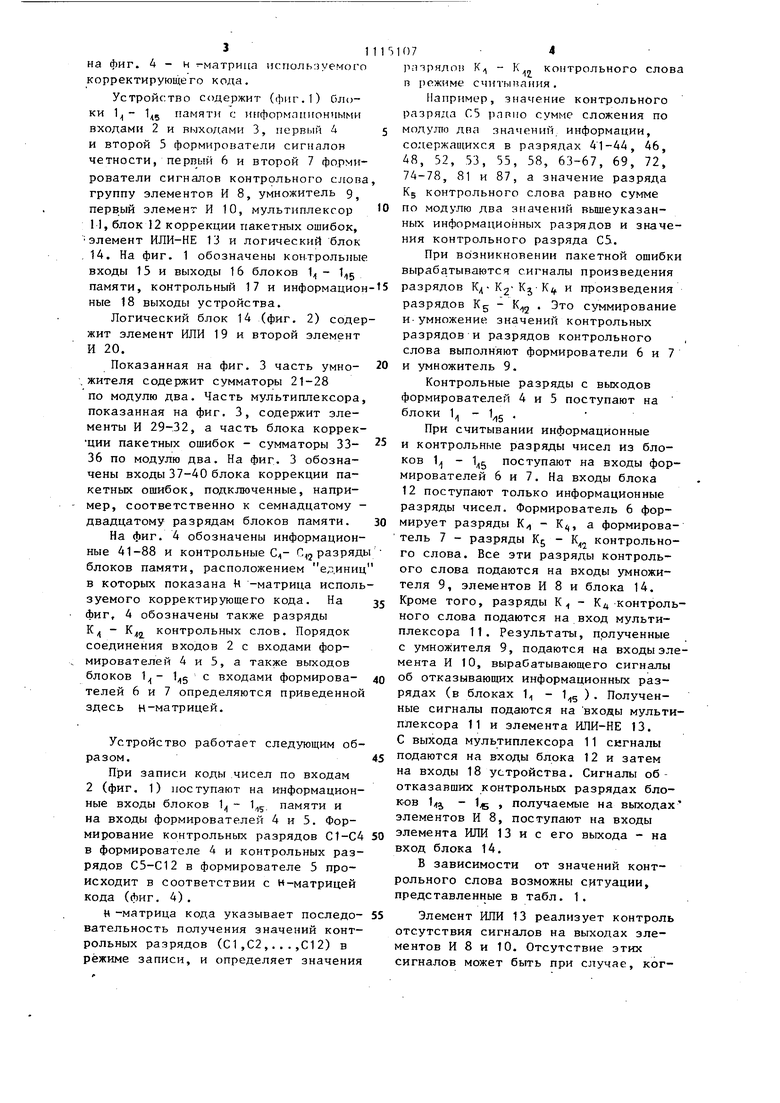

Устройство содержит (фиг.1) Олои 1 - памяти с информационными входами 2 и выходами 3, первый 4 5 второй 5 формирователи сигналов четности, первый 6 и второй 7 формирователи сигналов контррльного слова, группу элементов И 8, умножитель 9, первый элемент И 10, мультиплексор О 11, блок 12 коррекции пакетных ошибок,

элемент ИЛИ-НЕ 13 и логический блок

14. На фиг. 1 обозначены контрольные входы 15 и выходы 16 блоков 1;, - 1;,5 памяти, контрольный 17 и информацион-5 ные 18 выходы устройства.

Логический блок 14 (фиг. 2) содерит элемент ИЛИ 19 и второй элемент И 20.

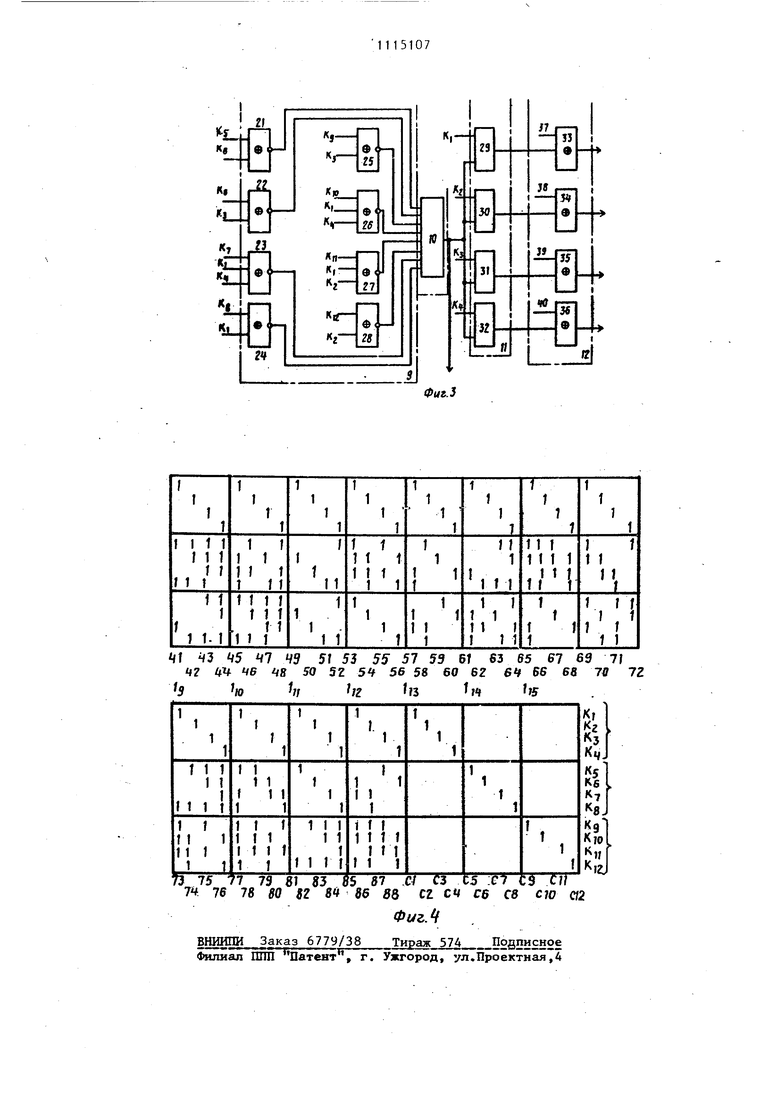

Показанная на фиг. 3 часть умно- 20

жителя содержит сумматоры 21-28 по модулю два. Часть мультиплексора, показанная на фиг. 3, содержит элеенты И 29-32, а часть блока коррекции пакетных ошибок - сумматоры 33- 5 36 по модулю два. На фиг. 3 обозначены входы 37-40 блока коррекции пакетных ошибок, подключенные, например, соответственно к семнадцатому двадцатому разрядам блоков памяти. 30

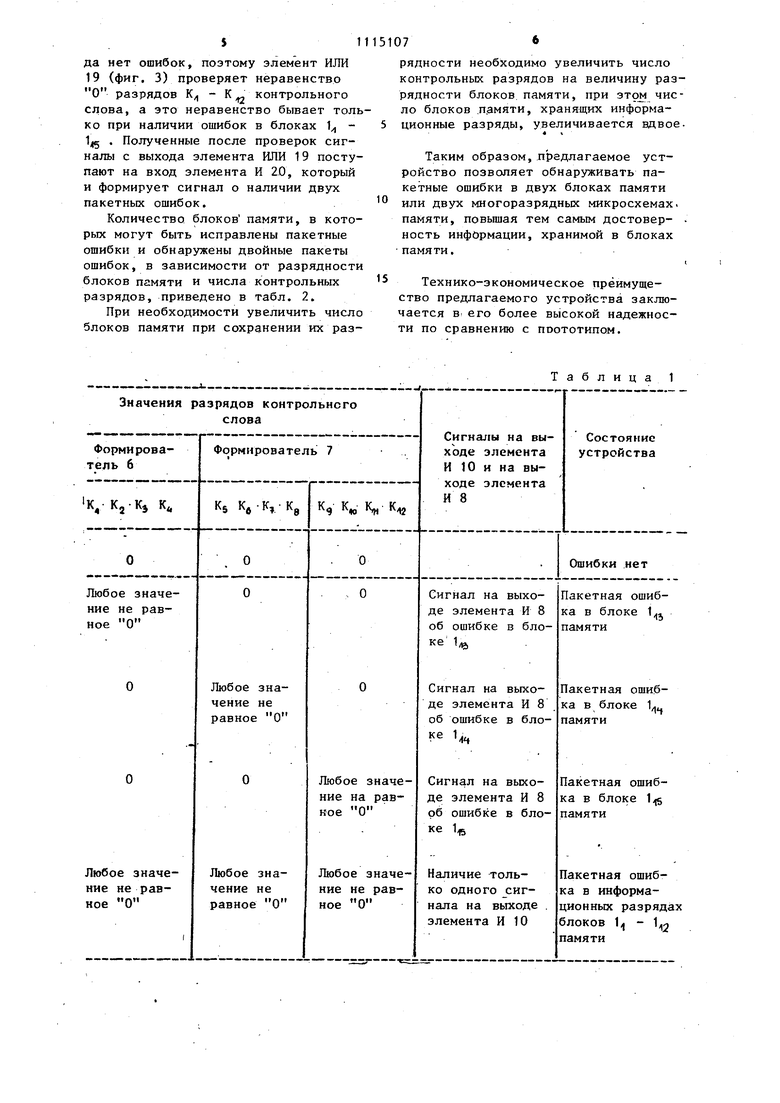

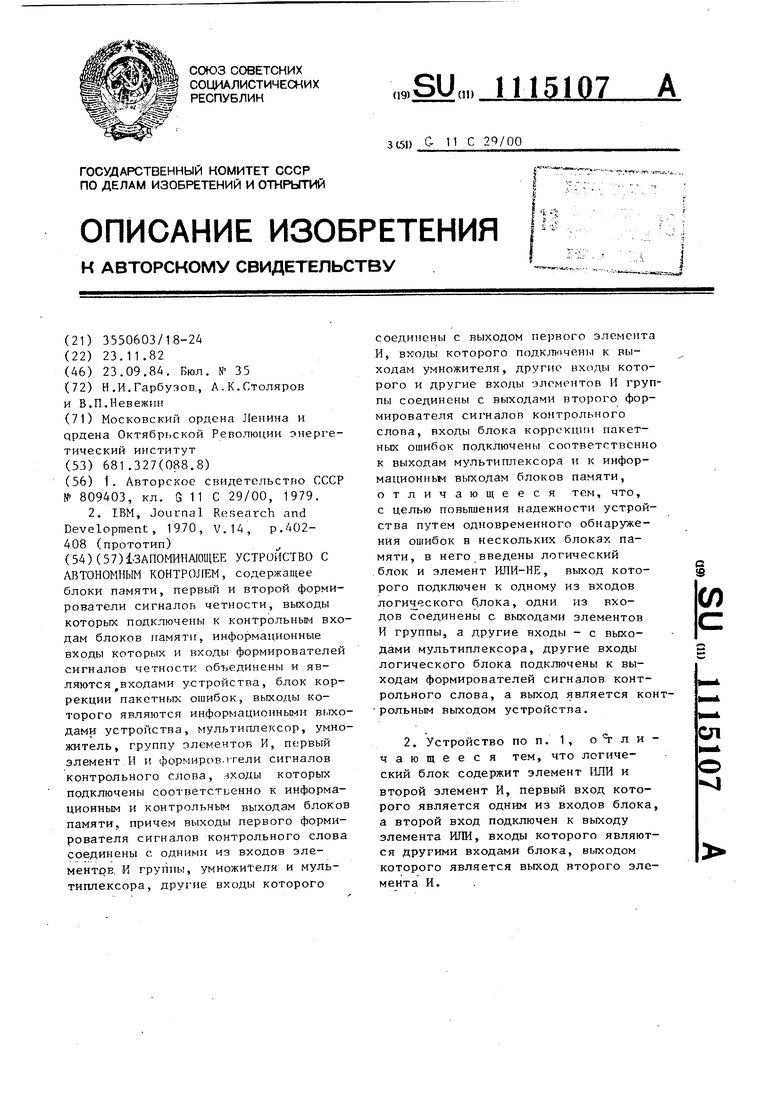

На фиг. 4 обозначены информационные 41-88 и контрольные С, разряды блоков памяти, расположением единиц в которых показана t -матрица используемого корректирующего кода. На 35 фиг, 4 обозначены также разряды К - Kf контрольных слов. Порядок соединения входов 2 с входами формирователей 4 и 5, а также выходов блоков 1 - 1;(5 - входами формирова- 40 телей 6 и 7 определяются приведенной здесь н-матрицей.

Устройство работает следующим образом.45

При записи коды чисел по входам 2 (фиг. 1) поступают на информационные входы блоков 1 - 1.,. памяти и на входы формирователей 4 и 5. Формирование контрольных разрядов С1-С4 50 в формирователе 4 и контрольных разрядов С5-С12 в формирователе 5 происходит в соответствии с и-матрицей кода (фиг. 4).

ц-матрица кода указывает последо- 55 вательность получения значений контрольных разрядов (С1,С2,...,С12) в режиме записи, и определяет значения

7 4

ртрядон К - контрольного слова 1Э режиме считывания.

Например, значение контрольного разряда С5 parsiio сумме сложения по модулю два значений информации, содержащихся в разрядах 41-44, 46, 48, 52, 53, 55, 58, 63-67, 69, 72, 74-78, 81 и 87, а значение разряда Kg контрольного слова равно сумме по модулю два значений вьшеуказанных информационных разрядов и значения контрольного разряда С5.

При возникновении пакетной ошибки вырабатываются сигналы произведения разрядов K -KgKj-K и произведения разрядов Kg - . Это суммирование и-умножение значений контрольных разрядов и разрядов контрольного слова выполняют формирователи 6 и 7 и умножитель 9.

Контрольные разряды с выходов формирователей 4 и 5 поступают на блоки 1у, - 1„5

При считывании информационные и контрольные разряды чисел из блоков 1 - поступают на входы формирователей 6 и 7. На входы блока 12 поступают только информационные разряды чисел. Формирователь 6 формирует разряды К,, - Ki,, а формирователь 7 - разряды Kg - К,, контрольного слова. Все эти разряды контролього слова подаются на входы умножителя 9, элементов И 8 и блока 14. Кроме того, разряды К - К контрольного слова подаются на вход мультиплексора 11. Результаты, полученные с умножителя 9, подаются на входы элемента И 10, вырабатывающего сигналы об отказывающих информационных разрядах (в блоках 1 - Полученные сигналы подаются на входы мультиплексора 11 и элемента ИЛИ-НЕ 13. С выхода мультиплексора 11 сигналы подаются на входы блока 12 и затем на входы 18 устройства. Сигналы оботказавших контрольных разрядах блоов 1;(j в получаемые на выходах лементов И 8, поступают на входы элемента РШИ 13 и с его выхода - на ход блока 14.

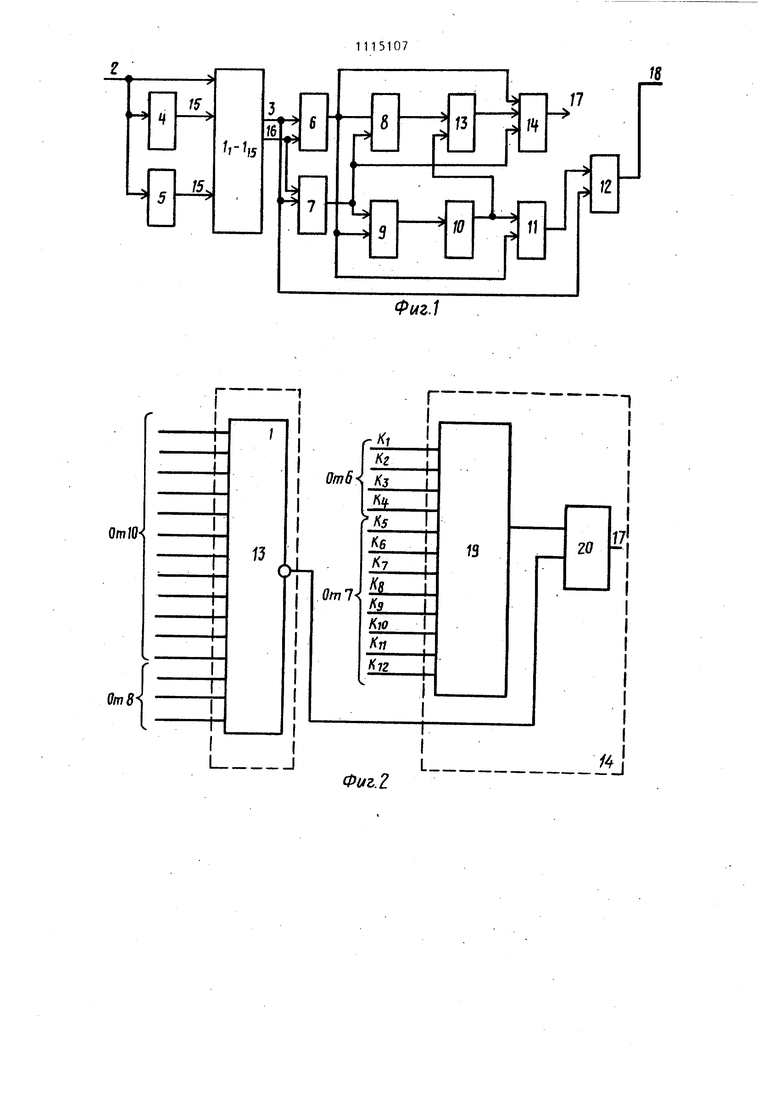

В зависимости от значений контольного слова возможны ситуации, редставленные в табл. 1.

Элемент ИЛИ 13 реализует контроль отсутствия сигналов на выходах элеентов И 8 и 10. Отсутствие этих сигналов может быть при случае, когда нет ошибок, поэтому элемент ИЛИ 19 (фиг. 3) проверяет неравенство О разрядов К, - К „ контрольного слова, а это неравенство бывает толь ко при наличии ошибок в блоках 1 1 . Полученные после проверок сигналы с выхода элемента ИЛИ 19 поступают на вход элемента И 20, который и формирует сигнал о наличии двух пакетных ошибок. Количество блоков памяти, в которых могут быть исправлены пакетные ошибки и обнаружены двойные пакеты ошибок, в зависимости от разрядности блоков памяти и числа контрольных разрядов, приведено в табл. 2. При необходимости увеличить число блоков памяти при сохранении их разрядности необходимо увеличить число контрольных разрядов на величину разрядности блоков памяти, при эт9м число блоков .памяти, хранящих информационные разряды, увеличивается вдвое. Таким образом, предлагаемое устройство позволяет обнаруживать пакетные ошибки в двух блоках памяти или двух многоразрядных микросхемах, памяти, повышая тем самым достовер- ность информации, хранимой в блоках памяти. Технико-экономическое преимущество предлагаемого устройства заключается в- его более высокой надежности по сравнению с поототипом.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1985 |

|

SU1262576A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Запоминающее устройство с исправлением ошибок | 1985 |

|

SU1305781A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с автономным контролем | 1986 |

|

SU1325570A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1411834A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Запоминающее устройство с коррекцией ошибок | 1980 |

|

SU942160A2 |

1.3АПОИИНА10ЩЕЕ УСТРОЙСТВО С ; ВТОНОМНЫМ КОНТРОЛЕМ, содержащее блоки памяти, первый и второй формирователи сигналов четности, выходы которых подключены к контрольным входам блоков памяти, информационные входы которых и входы формирователей сигналов четности объединены и являются входами устройства, блок коррекции пакетных ошибок, выходы которого являются информационными выходами устройства, мультиплексор, умножитель, группу элементов И, первый элемент И и формиров.ггели сигналов контрольного слова, .входы которых подключены соответственно к информационным и контрольным выходам блоков памяти, причем выходы первого формирователя сигналов контрольного слова соединены с одними из входов элементов, -И группы, умножителя и мультиплексора, другие входы которого соединены с выходом первого элемента И, входы которого подклкшены к выходам умножителя, другие входы которого и другие входы элементов И групП1 1 соединены с выходами второго формирователя сигналов контрольного слова, входы блока коррекции пакетных ошибок подключены соответственно к выходам мультиплексора и к информационным выходам блоков памяти, отличающееся тем, что, с целью повышения надежности устройства путем одновременного обнаружения ошибок в нескольких блоках памяти, в него введены логический i блок и элемент ИЛИ-НЕ, выход которого подключен к одному из входов (Л логич еского блока, одни из входов соединены с выходами элементов И группы, а другие входы - с вьсходами мультиплексора, другие входы логического блока подключены к выходам формирователей сигналов контрольного слова, а выход является конт рольным выходом устройства. ел 2. Устройство по п. 1 , о т л и чающееся тем, что логичео ский блок содержит элемент 11ПИ и второй элемент И, первый вход которого является одним из входов блока, а второй вход подключен к вькоду элемента ИЛИ, входы которого являются другими входами блока, вькодом которого является выход второго элемента И.

Таблица 1

8

Продолжение табл. I

Таблица 2

Фиг. 2

J

к к,

ю

11

w

W

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| IBM, Journal Research and Development, 1970, V.14, p,402408 (прототип) | |||

Авторы

Даты

1984-09-23—Публикация

1982-11-23—Подача