Изобретение относится к аналогодискретным преобразователям и предназначено, в частности, для создания высокоэффектинных систем многоканального приема и преобразования в код аналоговых сигналов.

Известна система многоканального приема и преобразования в код аналоговых сигналов , содержащая KONMyтатор входных аналоговых сигналов, выходом соединенный с входом аналого-цифрового преобразователя (АЦП), кодовые выходы которого соединены с информационными входами блока памяти 11J.

Недостатком этой системы является низкая пропускная способность, так как в ней преобразование по каждому каналу выполняется полнотактными изза отсутствия возможности использования результатов преобразования предыдущего цикла преобразования в последующем.

Наиболее близкой по техническому решению явл.чется система многоканаль ного приема и прербразования в код / аналоговых сигналов, содержащая коммутатор, соединенный адресными входами с первыми выходами блока управления, вторые выходы которого соединены с первыми входами блока па-мяти, аналого-цифровой преобразова-5 тель параллельно-последовательного типа, в котором аналоговый вычитатель соединен первым входом с выходом коммутатора, вторьвл входом - с выходом цифро-аналого10 вого преобразователя, третьим

входом - с третьим выходом блока управления и выходом - с входом преобразователя считывания, соединенного первым и вторым выходами соответртвен«5 но с первым и вторым входами блока управления и третьими выходагда - с входами преобразователями код - код, выходы которого соединены с первыми входами первого и второго блоков за20 писи, выходы первого из которых соединены с первыми входами реверсивного счетчика, первые выходы второго блока записи соединены с первыми входами регистра, выхо 5 ды блока памяти соединены с вторыми входами первого и второго блоков записи, третьи входы блоков записи соединены с четвертым выходом блока управления, пятый и шес30 той выхода которого соединены соответственно с четвертыми входами первого и второго блоков записи, выходы реверсивного счетчика соединены с первыми входами цифро-аналогового преобразователя и вторыми входами блока памяти, третьи входы которого соединены с выходом старшего разряда и кодовымивыxoдa 4и регистра и с вторыми входами цифро-аналогового преобразователя,.вторые входы регистра и реверсивного счетчика соединены с седьмым выходом блока управления, восьмой выход которого соединен с третьим входом реверсивного счетчика. Кроме того, девятый выход блока управления соединен с четвертым входом реверсивного счётчика, а второй и третий выходы второго блока записи соответственно соединены с единичным и нулевым входами старшего разряда регистра 2.

Недостатком этой системы является низкая пропускная способность из-за необходимости частого выполнения такта аналоговой коррекции между тактами преобразования.

Цель изобретения - повышение пропускной способности системы,.

Поставленная цель достигается .тем что система многоканального приема и преобразования в код аналоговых сигналов, содержащая коммутатор, соединенный адресными входами с первыми выходами блока управления, вторые выходы которого соединены с первьами входами блока памяти., аналого-цифровой преобразователь параллельно-последовательного типа,в котором аналоговый вычитатель соединен первым JBXOдом с выходом коммутатора, вторым входом - с выходом цифро-аналогового преобразователя, третьим входом третьим выходом блока управления и выходом - с входом преобразователя считывания, соединенного первым и вторым выходами соответственно с первым и вторым входами блока упр вления и третьими выходами - с входами преобразователя код-код выходы которого соединены с первыми входами первого и второго блоков записи, выходы первого из котогих соединены с первыми входами реверсивного счетчика. Первые выходы второго блока записи соединены с первыми входами регистра, выходы блока памяти соединены со вторыми входами первого и второго блоков записи, третьи входы блоков записи соединены с четвертым выходом блока управления, пятый и шестой выходы которого соединены соответственно с четвертыми входами первого и второго блоков записи, выходы реверсивного счетчика соединены с первыми входами цифро-аналогового преобразователя и вторыми входами блока памяти, третьи входы которого соединены старшего разряда и кодовыми выходами регистра и с вторлми входами цифро-аналогового преобразовать. ля, вторые входы регистра и реверсив-« ного счетчика соединены с седьмым выходом блока управления, восьмой выход которого соединен с третьим входом 5 реверсивного счетчика, дополнительно содержит триггер, одноразрядный блок записи, элементы задержки, элементы И и элементы ИЛИ, причем нулевой вход триггера соединен с выходом первого

Q элемента задержки, выход второго

элемента задержки соединен с третьим входом блока управления, четвертый вход которого соединен с выходом триггера и с первыми входами элементов И, второй вход первого элемента И соединен с четвертым входом второго блока записи, выходы второго и третьего элементов И соединены соответственно с входами первого и второго элементов задержки, вторые входы второго и третьего элементов И соединены соответственно с выходакш первого и второго элементов ИЛИ, первый из которых первым входом соединен с третьим входом реверсивного

5 счетчика, входы третьего и четвертого элементов задержки соединены соответственно с нyлeвьпv и единичным выходами одноразрядного блока записи, соединенного первым входом с выQ ходом старшего разряда регистра, вторым входом - с выходом блока памяти, третьим входом - с .единичным входом триггера и с третьим входом блока записи, четвертым входом - с

- выходом первого элемента И, выход

третьего элемента ИЛИ соединен с четвертым входом реверсивного счетчика, первый вход третьего элемента ИJШ соединен со вторым входом первого элемента ИЛИ и с девятым выходом

0 блока управления, выходы четвертого и пятого элементов ИЛИ соединены соответственно с единичным и нулевым входами старшего разряда регистра, выход третьего элемента задержки соединен со вторым входом третьего элемента ИЛИ и с первыми входами второ.го и четвертого элементов ИЛИ, второй вход последнего из которых соединен со вторым выходом второго блока

Q записи, третьим выходом соединенного с первым входом пятого элемен. та ИЛИ, второй вход которого соединен с выходом четв.ертого элемента задержки и вторым входом второго элемента

ИЛИ.

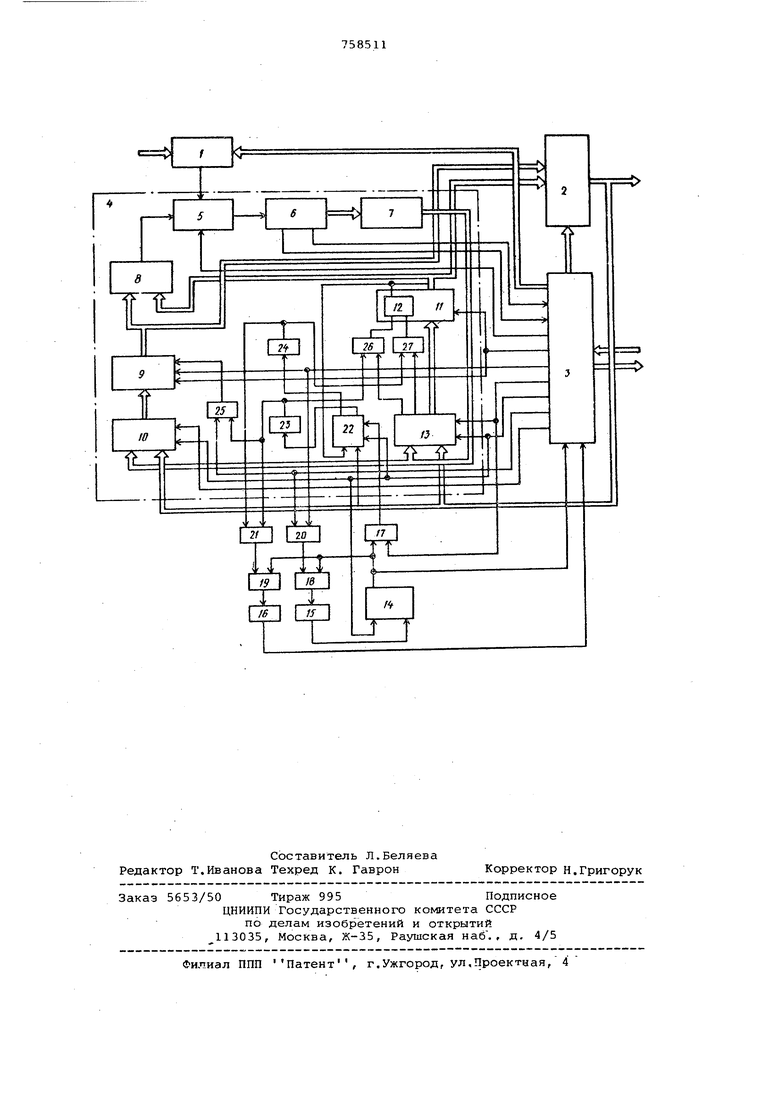

На чертеже представлена структурная схема системы многоканального приема и преобразования в код аналоговых сигналов. Система содержит коммутатор 1,

0 блок памяти 2, блок управления J, аналого-цифровой преобразователь 4 параллельно-последовательного типа, аналоговый вычитатель 5, преобразователь считывания 6, преЬбра;з6ватель.

5 (ЦАП) 8, реверсивный счетчик 9, первый блок записи 10, регистр 1.1, старший разряд 12 регистра,второй блок записи 13, триггер 14, первый 15 и второй 16 элементы задержки, первый 17, второй. 18 и третий 19 элементы, первый 20 и второй 21 элементы ИЛИ, одноразрядный блок записи 22, третий 23 и четвертый 24 элементы задержки, третий элемент ИЛИ 25, четвертый 26 и пятый 27 элементы ИЛИ Система работает следующим образом.

Во время первого цикла преобразования, когда в блоке 2 еще отсутствуют коды, соответствуюише значениям аналоговых сигналов, поданных на входы коммутатора 1. В данной системе, как и в прототипе, осуществляется режим загрузки блока 2, при котором по каждому каналу коммутатора 1 выполняются полные (двухтактные) преобразования. В результате формируются и запоминаются начальные коды/ соответствующие всем входным аналоговым сигналам.

В первом такте преобразования вычитатель 5 имеет передаточный коэффициент такой величины, вто при значении входного сигнала, равного максимально допустимой величине диапазона изменения входных сигналов, на выходах преобразователя 6, являющихся выходами его компараторов, устанавливается максимальный позиционный код. Этот код преобразуется преобразователем 7 в двоичный код с максимальным значением . Поэтому входной сигнал, имеющий любое другое значение внутри допустимого диапазона изменения, преобоазуется в соответствующий двоичный код со значением, лежащий в интервале от О до . Код, образованный в первом такте на выходах преобразователя 7, далее записывается через блок 10 в счетчик 9, выходы которого управляют преобразователем 8. Выходной сигнал последнего вычитается из входного преобразуемого сигнала в вычитателе 5, который т-акже усиливает этот разностный сигнал. После этого блок 3 формирует другой уровень сигнала, управляющего значением передаточного коэффициента вычитателя 5, который увеличивается в 2 раз сравнению со значением, имевшим место в первом такте преобразования. В результате этого усиленный в 2 раз разностный сигнал приводится к тому же диапазону изменения входных сигналов.

Поскольку в рассматриваемом АЦП параллельно-последовательного типа чувствит.ельность компараторов преобразователя 6 обычно в ( ) раз превышает величину кванта преобразователя, к моменту начала выполнения второго такта нередко значение выходного сигнала вычитателя 5 выходит

за пределы диапазона входных сигналов, что приводит к срабатыванию одного из граничных компараторов преобразователя 6 и появлению соответствующего сигнала на его первом или втором выходе. Анализ состояния сигналов на этих выходах производится в блоке 3. При наличии одного из них блок 3 формирует импульс, который проходит на третий или четвертый вход счетчика 9, увеличивая или уменьшая его содержимое на единицу. Одновременно с этим начинает изменяться на соответствующую величину выходной сигнал ЦАП 8. Через некоторое время, определяется максимально

5 возможным временем переходного процесса на выходе ЦАП 8, устанавливается новое значение аналогового сигнала на входе преобразователя б. Б этом состоит выполнение такта ана0логовой коррекции между первым и вторым тактами преобразования.

Такт аналоговой коррекции заканчивается в момент изменения сигнала на первом или втором выхо;:ах преоб5разователя б, инициировавшего эту коррекцию.

Затем блок 3 выполняет второй такт считывания кода с выходов преобразователя 7 в регистр 11 через

0 блок 13. Далее код с выходов счетчика 9 и регистра 11 перезаписывается в соотвествующую ячейку блока 2, чем заканчивается выполнение полнотактного преобразования аналогового сиг5нала по данному каналу.

После выполнения двухтактных преобразований по всем каналам коммутатора 1 и записи кодов их результатов в ячейки блока 2 блок 3 переходит к выполнению следующего цикла преобра0зования. Начиная со второго цикла, в системе выполняется только второй такт преобразования. Причем выполнение этого такта начинается с записи кода предыдущего результата преоб5разования из соответствующей ячейки блока 2 в счетчик 9 через блок 10 и в регистр 11 через блок 13.При этом, в отличие от прототипа, в рассматриваемой системе в старший разряд 12

0 регистра 11 код записывается инверх:ным по отношению к значению разряда, поступающег.1У по к-му выходу блока 2. Операция инверсной записи в старший разряд регистра выполняется с

5 помощью выведенных элементов 22, 23, 24, 26 и 27. При значении О в этом разряде сигнал с выхода элемента 23 поступает также через элемент 25 на четвертый вход счетчика 9, уменьшая его содержимое на единицу.

0 В результате зтих операций код, установленный в счетчике 9 и регистре 11, меньше на значения кода, хранящегося в соответствующей ячейке блока 2. Это приводит к относи5тельному смещению уровней сравнения на входах компараторов преобразователя б на величину, равную половине шкалы и позволяет исключить необходимость выполнения аналоговой коррекции после записи кода результата предыдущего преобразования в случае, если входной сигнал за время предыдущего цикла изменился на величину i. квантов. Итак, введение в систему триггера блока одноразрядной записи, элементов Задержки и элементов И и ИЛИ приводит к существенному повышению -ее пропускной способности, так как практически исключаются такты аналоговой коррекции, начиная со второго цикла преобразований. Формула изобретения Система многоканального приема и преобразования в код аналоговых сигналов , содержащая коммутатор, соединенный адресными входами с первыми выходами блока управления,вторые выходы которого соединены с первыми входами блока памяти,аналого-цифровой преобразователь параллельно-посл довательного типа,в котором аналоговый вычитатель соединен первым входо е выходом коммутатора,вторым входом с выходом цифро-аналогового преобр-азователя, третьим входом - с третьим выходом блока управления и выходом - с входом преобразователя считывания, соединенного первым и вторым выходами соответственно с первым и вторым входами блока управления и третьими выходами - с входами преобразователя код-код, выходы которого соединены с первыми входами первого и второго бл ков записи, выходы первого из которы соединены с первыми входами реверсив ного счетчика, первые выходы второго блока записи соединены с первыми вхо дами регистра, выходы блока памяти соединены со вторыми входами первого и второго блоков записи, третьи вход блоков записи соединены с четвертым выходом блока управления, пятый и ше той выходы которого соединены соотве ственно с четвертыми входами первого и второго блоков записи, выходы ревер сивного счетчика соединены с первыми входами цифро-аналогового преобразов теля и вторыми входами блока памяти, третьи входы которого соединены с вы старшего разряда и кодовыми выходами регистра и со вторыми входами цифро-аналогового преобразователя вторые входы регистра и реверсивного счетчика соеди нены с седЫуым выходом блока управления, восьмой выход которого соединен с третьим входом ревер сивного счетчика, отличающаяся тем, что, с целью повышения пропускной способности, в нее введены триггер, одноразрядный блок записи, элементы задержки, элементы И и элементы ИЛИ, причем нулевой вход триггера соединен с выходом первого-элемента задержки, выход второго элемента задержки соединен с третьим входом блока управления, четвертый вход которого соединен с выходом триггера и с первыми входами элементов И, второй вход первого элемента И соединен с четвертым входом второго блока записи, выходы второго и третьего элементов И соединены соответственно с входами первого и второго элементов задержки, вторые входы второго и третьего элементов И соединены соответственно с выходами :Первого и второго элементов ИЛИ, первый из которых первым входом соединен с третьим входом реверсивного счетчика, входы третьего и четвертого элементов задержки соединены соответственно с нулевым и единичным выходами одноразрядного блока записи, соединенного первым входом с выходом старшего разряда регистра, вторым входом - с выходом блока памяти, третьим входом - с единичным входом триггера и с третьим входом первого блока записи, четвертым входом - с выходом первого элемента И, выход третьего элемента ИЛИ соединен с чет-; вертым входом реверсивного счетчика, первый вход третьего элемента ИЛИ соединен со вторым входом первого элемента ИЛИ и с девятым выходом блока управления, выходы четвертого и i пятого элементов ИЛИ соединены соответственно с единичным и нулейым входами старшего разряда регистра, выход третьего элемента задержки соединен со вторым входом третьего элемента ИЛИ и с первыми входами,, второго и четвертого элементов ИЛИ, второй вход последнего из которых соединен со вторым выходом второго блока записи, третьим выходом соединенного с с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента задержкии втором входом второго элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1.Шушков Е.И. и Цодиков М,Б. Многоканальные аналого-цифровые преобразователи, Л., Энергия, 1975, с, 118, рис,5-6. 2,Помехи в цифровой технике - 71. Тезисы докладов Всесоюзной научно-технической конференции , Вильнюс, 1971, с.167, рис.1.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифроаналоговый преобразователь | 1985 |

|

SU1319280A1 |

| Устройство для воспроизведения аналогового сигнала | 1988 |

|

SU1524175A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Параллельно-последовательный п-разрядный аналого-цифровой преобразователь с автоматической коррекцией функции преобразования | 1988 |

|

SU1732471A1 |

| Параллельно-последовательный аналого- цифровой преобразователь | 1978 |

|

SU790287A1 |

| Аналого-цифровой преобразователь с частотным преобразованием | 1988 |

|

SU1547066A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Устройство для передачи телеметрической информации | 1984 |

|

SU1231529A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

Авторы

Даты

1980-08-23—Публикация

1978-06-23—Подача