Целью изобретения является повышение быстродействия устройства.

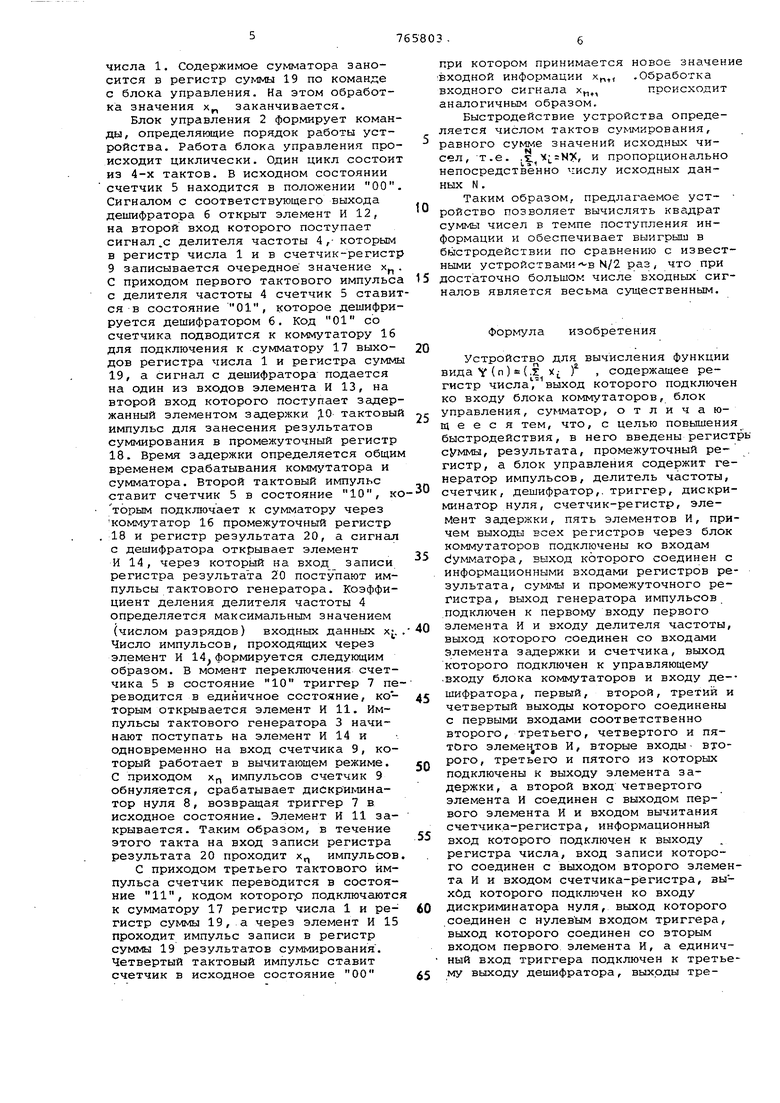

Это достигается тем, что в устройство для вычисления функции вида Y(n) (,t. Х ) , содержащее регистр числа, выход которого подключен ко входублока коммутаторов, блок управления, сумматор, введены регистры суммы, результата промежуточный регистр, ,а блок управления содержит генератор импульсов, делитель частоты, счетчик, дешифратор, триггер, дискриминатор нуля, счетчик-регистр, элемент задержки, пять элементов И, причем выходы всех регистров через блок коммутаторов подключены ко входам сумматора, выход которого соединен с ин-формационными входами регистров результата , суммы и промежуточного регистра, выход генератора импульсов подключен к первому входу первого элемента И и входу делителя частоты, выход которого соединен со входами элемента задержки и счетчика, выход которого подключен к управляющему входу блока коммутаторов и входу дешифратора, первый, второй, третий и четвертый выходы которого соединены с первыми входами соответственно второго, третьего, четвертого и пятого элементов И, вторые входы второго, третьего и пятого из которых подключены к выходу элемента задержки, а второй вход четвертого элемента И соединен с выходом первого элемента И и входом вычитания счетчика-регистра, информационный вход которого подключен к выходу регистра числа, вход записи которого соединен с выходом второго элемента И и входом счетчикарегистра , выход которого подключен ко входу дискриминатора нуля, выход которого соединен с нулевым входом триггера, выход которого соединен со вторым входом первого элемента И, а единичный вход триггера подключен к третьему выходу дешифратора, выходы третьего, четвертого и пятого элементов И соединены соответственно со входами записи промежуточного регистра, регистров суммы и результата, информационный вход регистра числа является входом устройства.

Сущность изобретения заключается в том, что вычисление квадрата суммы

значений х;

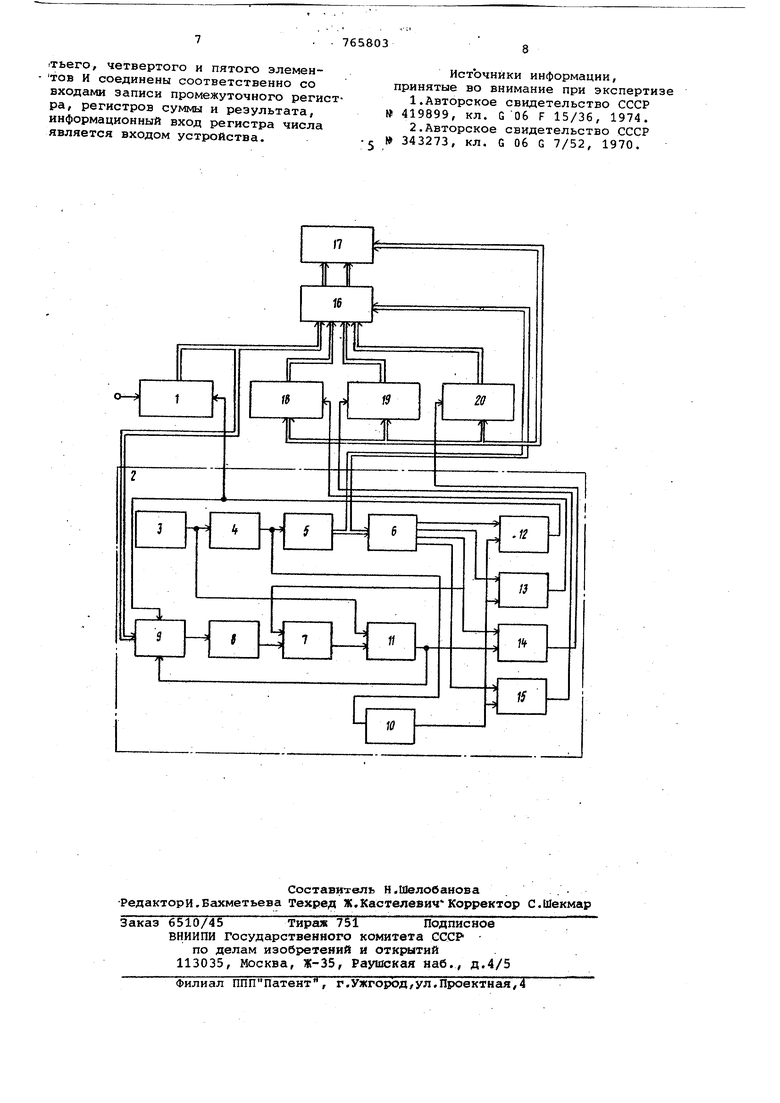

производится в интервале времени между приходом двух соседних .значения х,. и х и выполняе ся в соответствии с рекурентной формулой ,П л h-t 1 , t . (. )( ) На чертеже представлена структур.ная схема предлагаемого устройства. Схема содержит регистр 1 числа, блок 2 управления, генератор 3 импульсов

делитель частоты 4, счетчик 5, де- шифратор 6, триггер 7, дискриминатор нуля 8, счетчик-регистр 9, элемент задержки 10, элементы И 11 - 15, бло 16 коммутаторов, сумматор 17, промежуточный регистр 18, регистр суммы 19, регистры результата 20.

Устройство работает следующим образом.

В исходном состоянии перед поступлением значения Xf, в регистре суммы 19 записана сумма ,i. х , в регистре 20 записан квадрат суммы

/V

(ll/O

По сигналу с блока управления 2 очередное значение х заносится в регистр числа 1, после чего блок управления выдает команду на коммутатор 16 для подключения на входы сумматора 17 выходов регистра числа 1 и регистра суммы 19. Содержимое регистра суммы подается со сдвигом на один разряд влево, благодаря чему осуществляется умножение суммы

,Ji, XL на два без дополнительного тактирования. Сумматор выполнен на потенциальных полусумматорах, поэтому непосредственно после подключения к нему указанных значений чисел на его выходах устанавливается код числа Z .|.Хп который по сигналу с блок управления 2 записывается в промежуточный регистр 18.

После этого к сумматору 17 блоко управления 2 через коммутатор 16 подключаются выходы промежуточного регистра 18 и регистра квадрата суммы 20. Блок управления 2 выдает х, сигналов на вход записи регистра квадрата (результата) 20 для занесения в последний результат суммирования, после чего в регистре 20 образуется число, равное квадрату

.1П суммы

Действительно: .п-1 ., . . , п-

г

Хп

4ХГ-()(1) Число тактов суммирования, равное х„, блок управления определяет благодаря наличию связи его входа с выходом регистра числа х,, . Значение результата запоминается в. регистре ,20, после чего блок управления дает команду на вычисление суммы п п-1 ,1у.-1.Х;+ч . .Ui . путем подключения к сумматору 17-выходов, регистра суммы 19 и регистра числа 1. Содержимое сумматора заносится в регистр суммы 19 по команде с блока управления. На этом обработка значения х заканчивается. Блок управления 2 формирует коман ды, определяющие порядок работы устройства. Работа блока управления про исходит циклически. Один цикл состои из 4-х тактов, В исходном состоянии счетчик 5 находится в положении 00 Сигналом с соответствующего выхода дешифратора б открыт элемент И 12, на второй вход которого поступает сигнал.с делителя частоты 4,- которым в регистр числа 1 и в счетчик-регист 9 записывается очередное значение х С приходом первого тактового импульс с делителя частоты 4 счетчик 5 стави ся в состояние 01, которое дешифри руется дешифратором 6, Код 01 со счетчика подводится к коммутатору 16 для подключения к сумматору 17 выходов регистра числа 1 и регистра сумм 19, а сигнал с дешифратора подается на один из входов элемента И 13, на второй вход которого поступает задер жанный элементом задержки .О тактовы импульс для занесения результатов суммирования в промежуточный регистр 18. Время задержки определяется общи временем срабатывания коммутатора и сумматора. Второй тактовый импульс ставит счетчик 5 в состояние 10, к торым подключает к сумматору через коммутатор 16 промежуточный регистр 18 и регистр результата 20, а сигнал с дешифратора открывает элемент И 14, через который на вход записи регистра результата 20 поступают импульсы тактового генератора. Коэффициент деления делителя частоты 4 определяется максимальным значением (числом разрядов) входных данных xj, Число импульсов, проходящих через элемент И 14 формируется следующим образом. В момент переключения счетчика 5 в состояние 10 триггер 7 пе реводится в единичное состояние, которым открывается элемент И 11, Импульсы тактового генератора 3 начинают поступать на элемент И 14 и одновременно на вход счетчика 9, который работает в вычитающем режиме. С приходом Хр импульсов счетчик 9 обнуляется, срабатывает дискриминатор нуля 8, возвращая триггер 7 в исходное состояние. Элемент И 11 закрывается. Таким образом, в течение этого такта на вход записи регистра результата 20 проходит х,, импульсов С приходом третьего тактового импульса счетчик переводится в состояние 11, кодом которогр подключаютс к сумматору 17 регистр числа 1 и регистр суммы 19, а через элемент И 15 проходит импульс записи в регистр сумгФа 19 результатов суммирования . Четвертый тактовый импульс ставит счетчик в исходное состояние 00 при котором принимается новое значение ВХОДНОЙ информации х,, .Обработка входного сигнала х,,, происходит аналогичным образом. Быстродействие устройства определяется числом тактов суммирования, равного суь1ме значений исходных чисел, -т.е. .,, x N, и пропорционально непосредственно числу исходных данных N. Таким образом, предлагаемое уст- ройство позволяет вычислять квадрат суммы чисел в темпе поступления информации н обеспечивает выигрыш в быстродействии по сравнению с известными устройствами- в N/2 раз, что при достаточно большом числе входных сигналов является весьма существенным. Форь1ула изобретения Устройство для вычисления функции видаУ(п) (.§ i f , содержащее регистр числа , выход которого подключен ко входу блока коммутаторов, блок управления, сумматор, о т л и ч а ющ е е с я тем, что, с целью повышения быстродействия, в него введены регистрь суммы, результата, промежуточный регистр, а блок управления содержит генератор импульсов, делитель частоты, счетчик, дешифратор,, триггер, дискриминатор нуля, счетчик-регистр, элемент задержки, пять элементов И, причем выходы всех регистров через блок коммутаторов подключены ко входам dyMM.aTOpa, выход которого соединен с информационными входами регистров результата, суммы и промежуточного регистра , выход генератора импульсов подключен к первому входу первого элемента И и входу делителя частоты, выход которого соединен со входами элемента згщержки и счетчика, выход которого подключен к управляющему входу блока коммутаторов и входу де-шифратора, первый, второй, третий и четвертый выходы которого соединены с первыми входами соответственно второго, третьего, четвертого и пятого элемен тов И, вторые входы- второго, третьего и пятого из которых подключены к выходу элемента задержки, а второй вход четвертого элемента И соединен с выходом первого элемента И и входом вычитания счетчика-регистра, информационный вход которого подключен к выходу регистра числа, вход записи которого соединен с выходом второго элемента И и входом счетчика-р15гистра, выхйд которого подключен ко входу дискриминатора нуля, выход которого соединен с нулевым входом триггера, выход которого соединен со вторым входом первого элемента И, а единичный вход триггера подключен к третьему выходу дешифратора, выходы треiTbero, четвертого и пятого элементов и соединены соответственно со входами записи промежуточного регистра, регистров суммы и результата, информационный вход регистра числа является входом устройства.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 419899, кл. G Об F 15/36, 1974. 2.Авторское свидетельство СССР 343273, кл. G 06 G 7/52, 1970.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный статистический анализатор | 1980 |

|

SU959092A1 |

| ЛИНЕЙНЫЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2028665C1 |

| Вычислительное устройство | 1985 |

|

SU1269124A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Устройство для возведения в степень (его варианты) | 1982 |

|

SU1076905A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для умножения комплексных чисел | 1986 |

|

SU1388851A1 |

| Декодирующее устройство линейного циклического кода | 1990 |

|

SU1718386A1 |

| УСТРОЙСТВО ФАЗИРОВАНИЯ ШКАЛЫ ВРЕМЕНИ ЭЛЕКТРОННЫХ ЧАСОВ | 1994 |

|

RU2084944C1 |

| Устройство для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации | 2016 |

|

RU2634198C1 |

Авторы

Даты

1980-09-23—Публикация

1978-08-25—Подача