1

Изобретение относится к аналоговой вы числительной технике и может быть использовано в устройствах обработки аналоговой информации.

Известны аналоговые элементы памяти разомкнутого типа, содержащие последовательно соединенные устройство записи, запоминающий элемент -с разрушающим считыванием информации, устройство считывания, обладающее низкой, точностью (I).

Известно устройство, в котором повышение точности достигается за счет шведения отрицательной обратной связи {2. .

Однако отрицательная обратная связь в этом случае применяется только для элементов с неразрушающнм считываимеМ информации.

Целью изобретения является повышение точности аналогового запоминающего устройства.

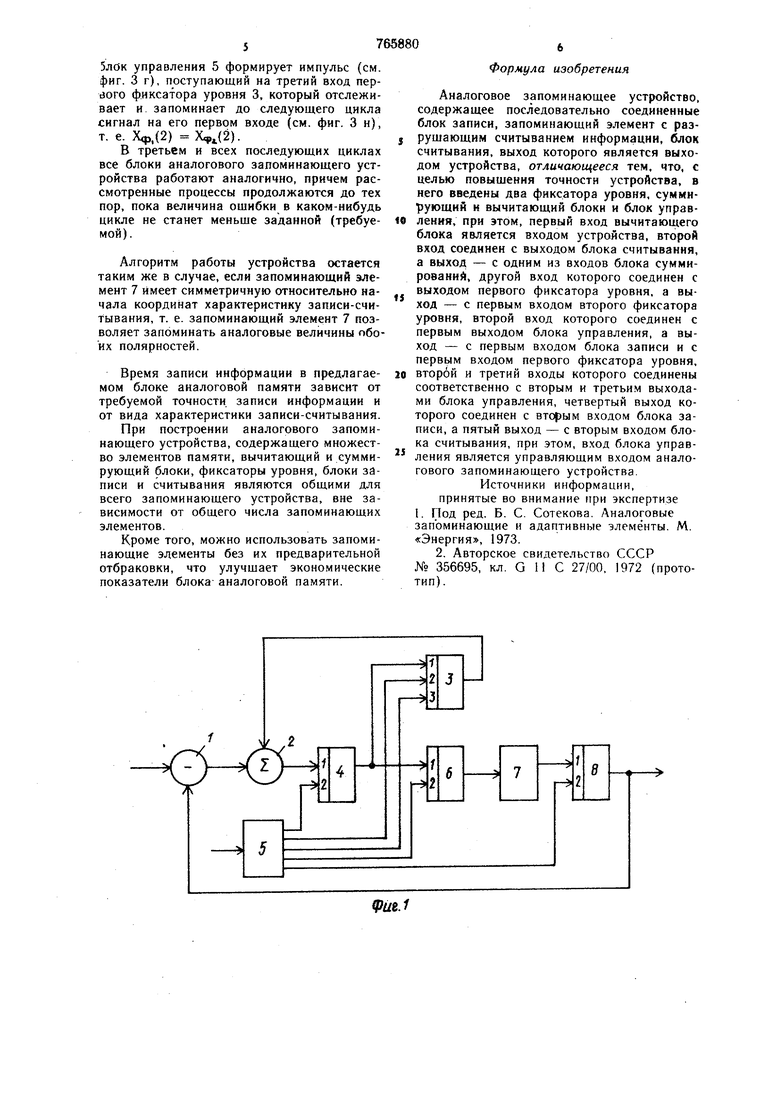

Достигается это тем, что в аналоговое запоминающее устройство, содержащее последовательно соединенные блок записи,-, запоминающий элемент с разрушающим Считыванием информации, блок считывания, выход которого является выходом устройства, введены два фиксатору уровня, суммирующий и вычитающий блокн и блок управлення, при этом, первый вход вычитающего блока является входом устроЛстша, второй вход соединен с выходом блока считывания, а выход - с одинм из входов блока суммирования, другой вжод которого соединен с выходом первого фиксатора уровня, а выход - с первым яходон второго фнкcafopa уровня, второй «яод которого соединен с первым выходом блок управления, а выход - с первым входом блока записи и с первым

10 входом первого фиксатора уровня, второй и третий входы которого соедииены соответственно с вторым и третьим выходами блока управления, четвертый выход которого :оединеи с вторым входом блока запнсн, а пятый выход - с вторым входом блока

ts сч итывания, при этом вход блока управления является управляющнм входом аналогового запомнвающего устройства.

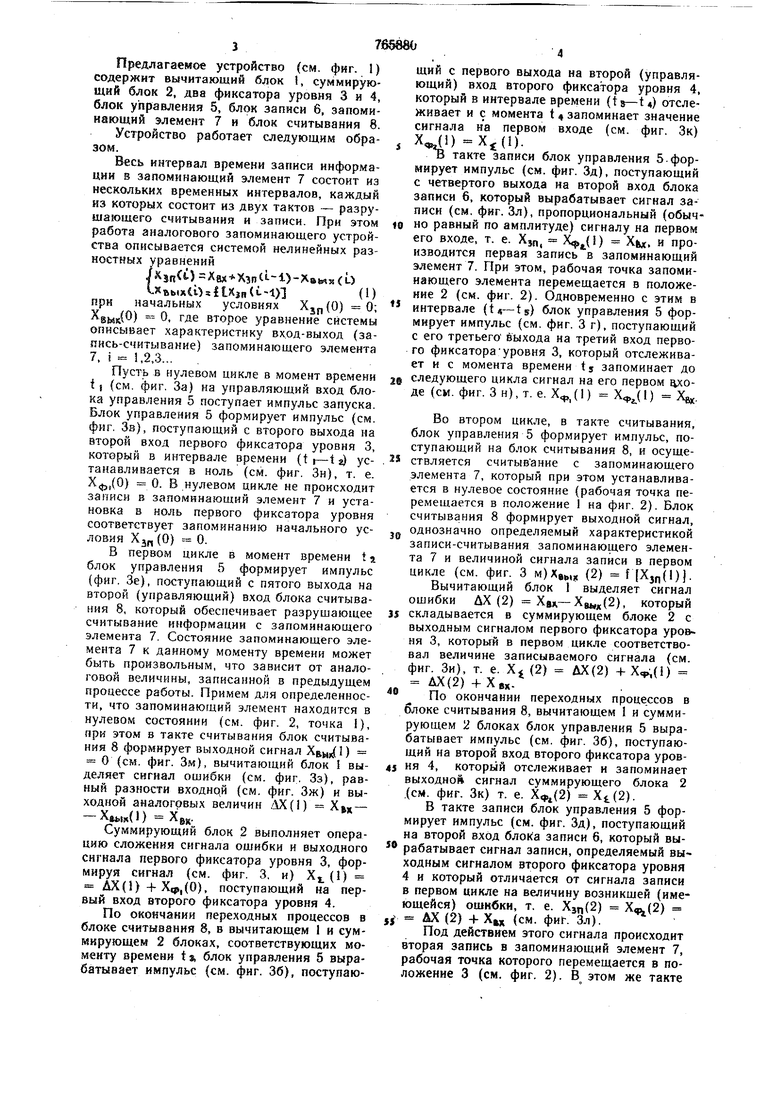

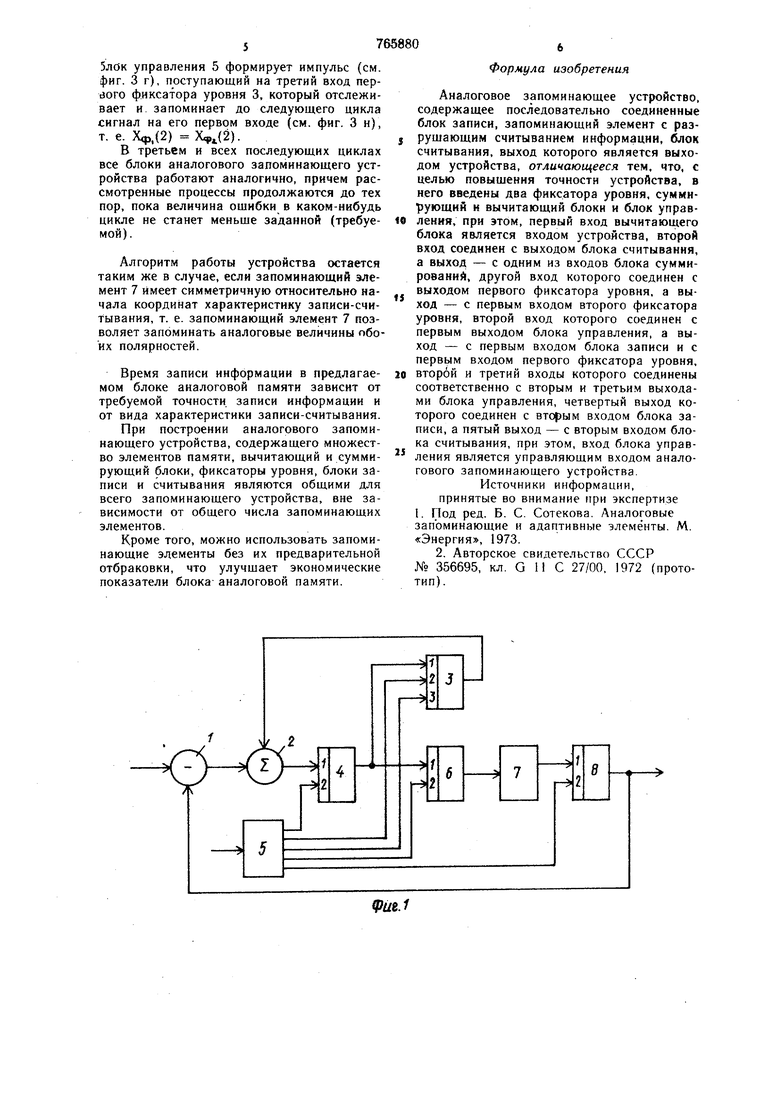

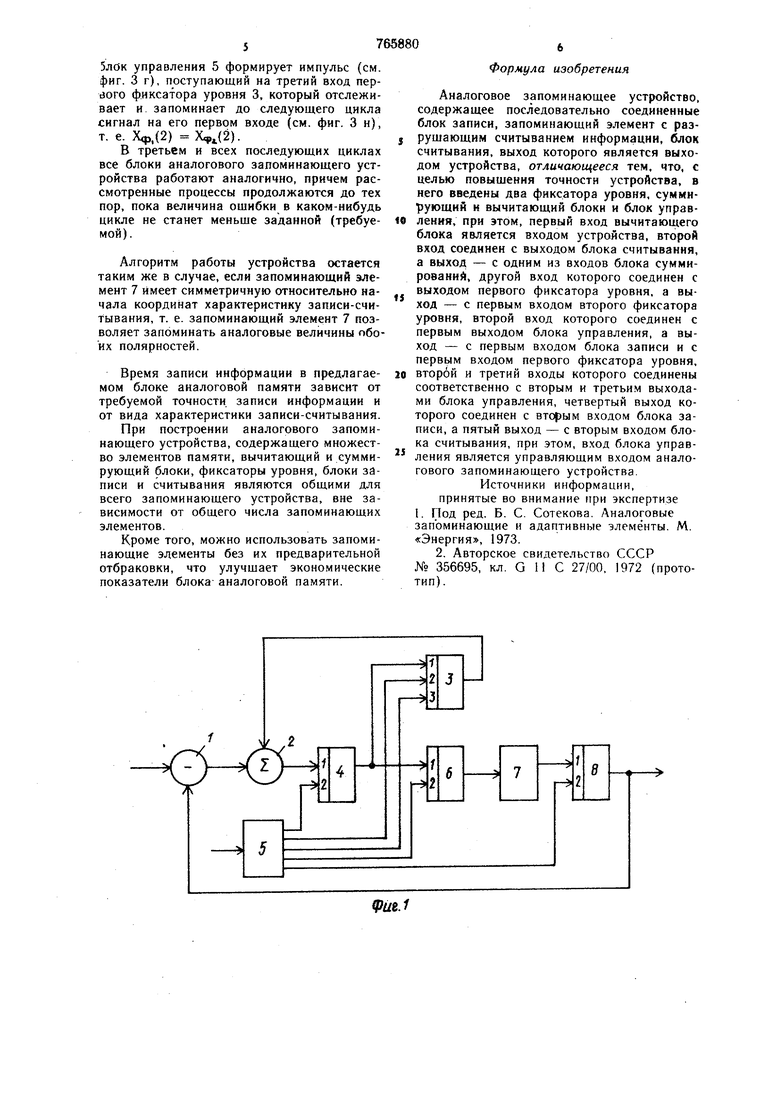

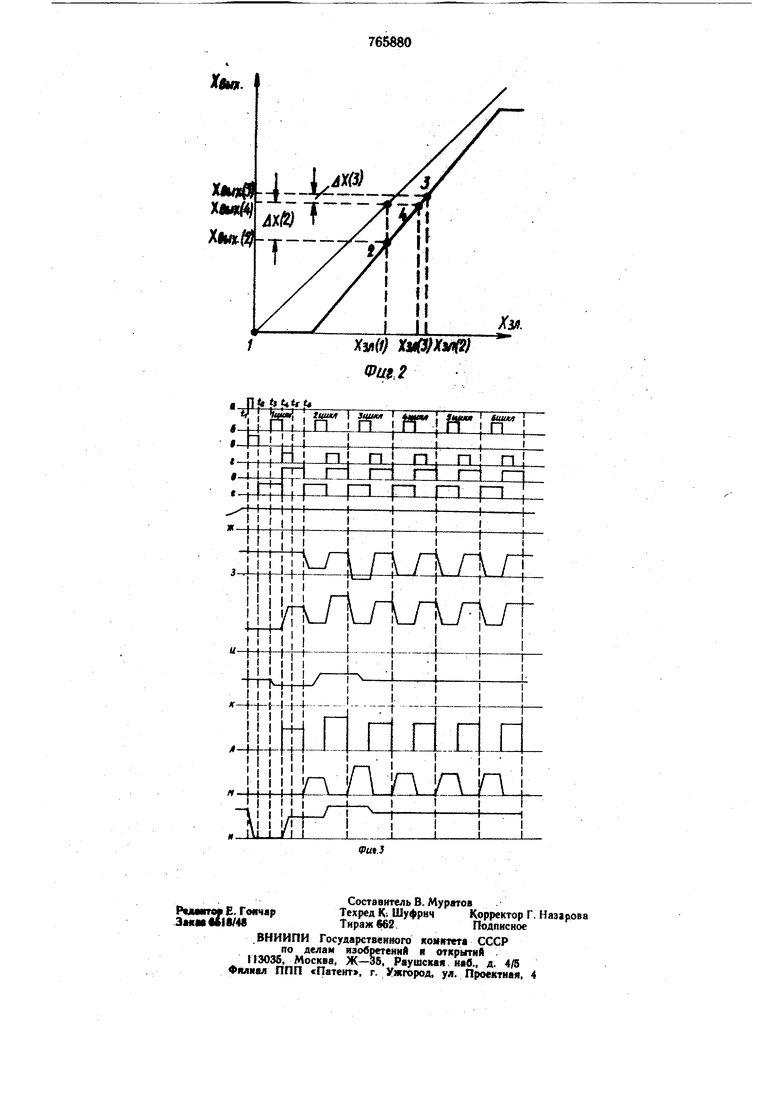

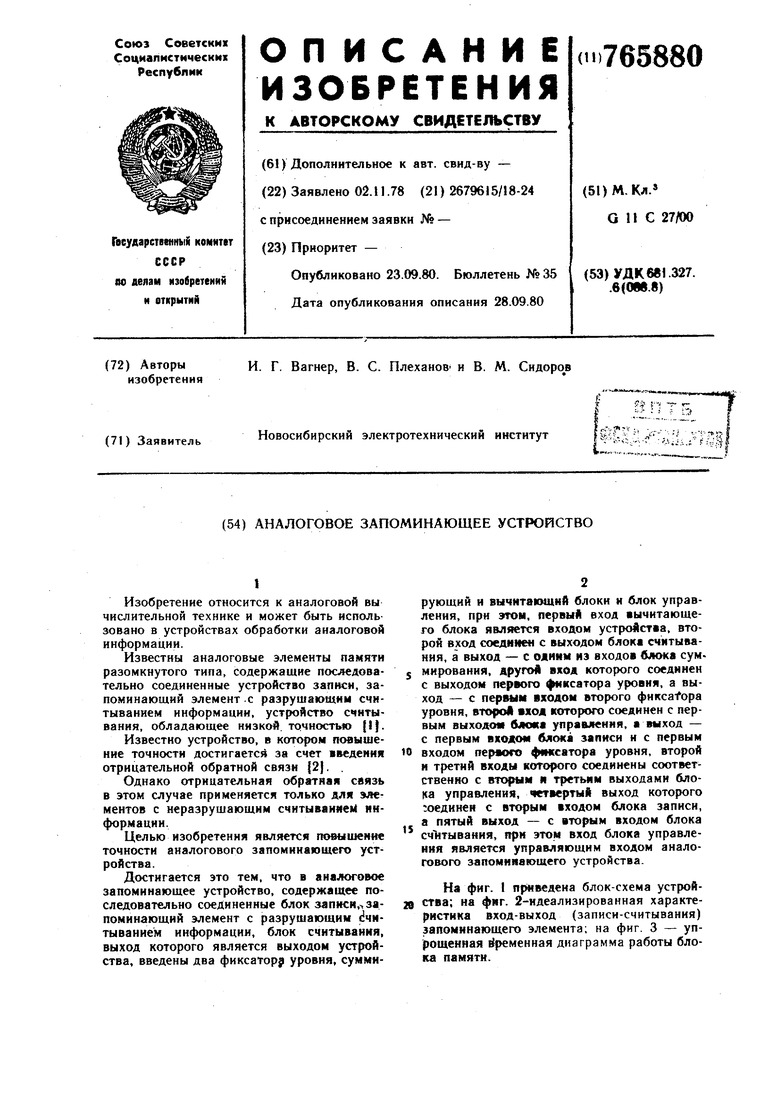

На фиг. 1 приведеиа блок-схема устрой2В ства; на фиг. 2-идеалнзнрованная характеристика вход-выход (записн-счнтывання) запоминающего элемента; на фиг. 3 - упрощенная ({ременная диаграмма работы блока памяти.

Предлагаемое устройство (см. фиг. I) содержит вычитающий блок I, суммирующий блок 2, два фиксатора уровня 3 и 4, блок управления 5, блок записи 6, запоминающий элемент 7 и блок считывания 8.

Устройство работает следующим образом.

Весь интервал времени записи ииформацни S запоминающий элемеит 7 состоит из нескольких времениых иигервалов, каждый из которых состоит из двух тактов разрушающего считывания и записи. При этом работа аналогового запоминающего устройства описывается системой нелинейных разностных уравнений

|X5ri t)X8x X3nCL-l)-Xews(t)

Ubb.xCi)UKj,nU-l)l(1)

гфи начальных условиях Хз,{0) 0; Xg(0) - О, где второе уравнение системы описывает характеристику вход-выход (запись-считывание) запоминающего элемента 7. I - 1,2,3...

Пусть в нулевом цикле в момент времени t j (см. фиг. За) на управляющий вход блока управления 5 поступает импульс запуска. Блок управления 5 формирует импульс (см. фиг. Зв), поступающий с второго выхода на второй вход первого фиксатора уровня 3, который Б интервале времени (t i-i г) устанавливается в ноль (см. фиг. Зн), т. е. Хф,(0) 0. В нулевом цикле не происходит записи в запоминающий элемент 7 и установка в ноль первого фиксатора уровня соответствует запоминанию начального условия Хз„ (0) 0.

В первом цикле в момент времени tj блок управления 5 формирует импульс (фиг. Зе), поступающий с пятого выхода на второй (управляющий) вход блока считывания 8, который обеспечивает разрушающее считывание информации с запоминающего элемента 7. Состояние запоминающего элемента 7 к данному моменту времени может быть произвольным, что зависит от аналоговой величины, записанной в предыдущем процессе работы. Примем для определенности, что запоминающий элемент находится в нулевом состоянии (см. фиг. 2, точка I), при этом в такте считывания блок считывания 8 формирует выходной сигнал О (см. фиг. 3м), вычитающий блок I выделяет сигнал ошибки (см. фиг. Зз), равный разности входнцй (см. фиг. Зж) и выходной аналоговых величин ДХ(1) Х - - XftbtxC) Xgj(.

Суммирующий блок 2 выполняет операцию сложения сигнала ощибки и выходного сигнала первого фиксатора уровня 3, формируя сигнал (см. фиг, 3, и) Х(1) ДХ(})-f Хф,(0), поступающий на первый вход второго фиксатора уровня 4.

По окончании переходных процессов в блоке считывания 8, в вычитающем 1 и суммирующем 2 блоках, соответствующих моменту времени ts, блок управления 5 вырабатывает импульс (см. фиг. 36), поступающий с первого выхода на второй (управляющий) вход второго фиксатора уровня 4, который в интервале времени () отслеживает и с момента t « запоминает значение сигнала на первом входе (см. фиг. Зк)

, Xv(J)-X(l).

в такте записи блок управления 5 формирует импульс (см. фиг. Зд), поступающий с четвертого выхода на второй вход блока записи 6, который вырабатывает сигнал записи (см. фиг. 3л), пропорциональный (обычно равный по амплитуде) сигналу на первом его входе, т. е. Xjn, (1) , и производится первая запись в запоминающий элемент 7. При этом, рабочая точка запоминающего элемента перемещается в положение 2 (см. фиг. 2). Одновременно с этим в

интервале () блок управления 5 формирует импульс (см. фиг. 3 г), поступающий с его третьего выхода на третий вход первого фиксаторауровня 3, который отслеживает и с момента времени t5 запоминает до

в следующего цикла сигнал на его первом аходе (си. фиг. Зн),т. е. Х,(1) ) У.

Во втором цикле, в такте считывания, блок управления 5 формирует импульс, поступающий на блок считывания 8, и осуществляется считывание с запоминающего элемента 7, который при этом устанавливается в нулевое состояние (рабочая точка перемещается в положение 1 на фиг. 2). Блок считывания 8 формирует выходной сигнал, однозначно определяемый характеристикой

30 записи-считывания запоминаюи его элемента 7 и величиной сигнала записи в первом цикле (см. фиг. 3 м)Хвы;,( (2) f Xjf,(l)Вычитающий блок 1 выделяет сигнал ошибки ДХ (2) Хал-Xgt,(2), который JJ складывается в суммирующем блоке 2 с выходным сигналом первого фиксатора уровня 3, которыми в первом цикле соответствовал величине записываемого Сигнала (см. фиг. Зи), т. е. Х, (2) ДХ(2) -f Хч.,(1) АХ(2) -f Хвх.

По окончании переходных процессов в блоке считывания 8, вычитающем 1 и суммирующем 2 блоках блок управления 5 вырабатывает импульс (см. фиг. 36), поступающий на второй вход второго фиксатора уров4J ия 4, которь1Й отслеживает и запоминает выходной сигнал суммирующего блока 2 .(см. фиг. Зк) т. е. Хч,(2) - Xi(2).

В такте записи блок управления 5 формирует импульс (см. фиг. Зд), поступающий на второй вход записи 6, который вырабатывает сигнал записи, определяемый выходным сигналом второго фиксатора уровня 4 и который отличается от сигнала записи в первом цикле на величину возникшей (имеющейся) ошибки, т. е. Хзп(2) (2) „V АХ (2) -1- (см. фиг. 3л).

Под действием этого сигнала происходит вторая запись в запоминающий элемент 7, рабочая точка которого перемещается в положение 3 (см. фиг. 2). В этом же такте

Злок управления 5 формирует импульс (см. фиг. 3 г), поступающий на третий вход первого фиксатора уровня 3, который отслеживает и. запоминает до следующего цикла снгнал на его первом входе (см. фиг. 3 и) т. е. .(2) Х(2).

В третьем и всех последующих циклах все блоки аналогового запоминающего устройства работают аналогично, причем рассмотренные процессы продолжаются до тех пор, пока величина ошибки в каком-нибудь цикле не станет меньще заданной (требуемой).

Алгоритм работы устройства остается таким же в случае, если запоминающий элемент 7 имеет симметричную относительно начала координат характеристику записи-считывания, т. е. запоминающий элемент 7 позволяет запоминать аналоговые величины обоих полярностей.

Время записи информации в предлагаемом блоке аналоговой памяти зависит от требуемой точности записи информации и от вида характеристики записи-считывания.

При построении аналогового запоминающего устройства, содержащего множество элементов памяти, вычитающий и суммирующий блоки, фиксаторы уровня, блоки записи и считывания являются общими для всего запоминающего устройства, вне зависимости от общего числа запоминающих элементов.

Кроме того, можно использовать запоминающие элементы без их предварительной отбраковки, что улучщает экономические показатели блока аналоговой памяти.

Формула изобретения

Аналоговое запоминающее устройство, содержащее последовательно соединенные блок записи, запоминающий элемент с разрушающим считыванием информации, блок считывания, выход которого является выходом устройства, отличающееся тем, что, с целью повышения точности устройства, в него введены два фиксатора уровня, суммирующий к вычитающий блоки и блок управления, при этом, первый вход вычитающего блока является входом устройства, второй вход соединен с выходом блока считывания, а выход - с одним из входов блока суммирований, другой вход которого соединен с j выходом первого фиксатора уровня, а выход - с первым входом второго фиксатора уровня, второй вход которого соединен с первым выходом блока управления, а выход - с первым входом блока записи и с первым входом первого фиксатора уровня, 0 второй и третий входы которого соединены соответственно с вторым и третьим выходами блока управления, четвертый выход которого соединен с вторым входом блока записи, а пятый выход - с вторым входом блока считывания, при этом, вход блока управления является управляющим входом аналогового запоминающего устройства. Источники информации, принятые во внимание при экспертизе 1. Под ред. Б. С. Сотекова. Аналоговые запоминающие и адаптивные элементы. М. «Энергия, 1973.

2. Авторское свидетельство СССР № 356695, кл. G II С 27/00. 1972 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU903985A2 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| Блок аналоговой памяти | 1978 |

|

SU734814A1 |

| Аналоговое запоминающее устройство | 1985 |

|

SU1251184A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799013A1 |

| Способ определения частотной характеристики испытуемого объекта и устройство для его осуществления | 1984 |

|

SU1223074A1 |

| Способ измерения среднеквадратических значений переменных сигналов | 1990 |

|

SU1798705A1 |

Авторы

Даты

1980-09-23—Публикация

1978-11-02—Подача